# SOLUCIÓN PROBLEMAS DE FUNDAMENTOS DE TECNOLOGÍA DE COMPUTADORES

# T5. MEMORIAS

Solución ej. 1, 2 y 3 (Curso 2020-2021)

## Solución ejercicio 1 (Ver video de OLE)

#### 1. Comprobar que existe solución

Para poder comprobarlo, debemos fijarnos en el número de bits que tenemos en el bus de direcciones, y ver que con ese número de bits, podemos direccionar todo el mapa de memoria.

El bus de direcciones tiene 20 líneas, desde la A<sub>19</sub> hasta la A<sub>0</sub>, lo que supone una capacidad de direccionamiento de 2<sup>20</sup> palabras = 1 Mpalabras. En el caso que nos ocupa, necesitamos direccionar 512 Kpalabras de memoria RAM y 256 Kpalabras de memoria ROM, en total 768 Kpalabras. Por lo tanto, vemos que con los 20 bits del bus de direcciones sí se puede direccionar la memoria que se nos pide.

Por otro lado, tenemos que comprobar que el bus de datos soporte el ancho de una palabra de memoria (16 bits). Por tanto, vamos a suponer que el bus de datos cuenta con 16 líneas, desde la D<sub>15</sub> hasta la D<sub>0</sub>.

#### 2. Calcular los módulos de memoria que serán necesarios

Para la memoria RAM, disponemos de los siguientes módulos de memoria:

128 K x 1

$$\frac{512 \text{ K}}{128 \text{ K}} \times \frac{16 \text{ bits}}{1 \text{ bit}} = 4 \times 16 = 64 \text{ pastillas de } 128 \text{ K} \times 1$$

Con esta posibilidad se necesitarían 4 filas de módulos de 128 K posiciones de memoria (para poder direccionar las 512 K posiciones de memoria) y 16 módulos por cada una de las filas para almacenar los 16 bits que componen una palabra.

Con lo cual, el mapa de memoria RAM resultante contaría con  $4 \times 16 = 64$  pastillas de 128 K x 1.

• 256 K x 8

$$\frac{512 \text{ K}}{256 \text{ K}} \times \frac{16 \text{ bits}}{8 \text{ bits}} = 2 \times 2 = 4 \text{ pastillas de } 256 \text{ K} \times 8$$

Con esta posibilidad se necesitarían 2 filas de módulos de 256 K posiciones de memoria (para poder direccionar las 512 K posiciones de memoria) y 2 módulos por cada una de las filas para almacenar los 16 bits que componen una palabra (en cada uno de los módulos se almacenarán los 8 bits que componen las partes alta y baja de una palabra).

Con lo cual, el mapa de memoria RAM resultante contaría con 2 x 2 = 4 pastillas de 256 K x 8.

Para la memoria ROM, disponemos de los siguientes módulos de memoria:

• 128 K x 1

$$\frac{256 \text{ K}}{128 \text{ K}} \times \frac{16 \text{ bits}}{1 \text{ bit}} = 2 \times 16 = 32 \text{ pastillas de } 128 \text{ K} \times 1$$

• 64 K x 8

$$\frac{256 \text{ K}}{64 \text{ K}} \times \frac{16 \text{ bits}}{8 \text{ bit}} = 4 \times 2 = 8 \text{ pastillas de } 64 \text{ K} \times 8$$

• 128 K x 8

$$\frac{256 \text{ K}}{128 \text{ K}} \times \frac{16 \text{ bits}}{8 \text{ bits}} = 2 \times 2 = 4 \text{ pastillas de } 128 \text{ K} \times 8$$

La solución más sencilla es utilizar:

- 2 x 2 = 4 pastillas de 256 K x 8 para la memoria RAM

- 2 x 2 = 4 pastillas de 128 K x 8 para la memoria ROM

#### 3. Diseñar el mapa de memoria

Para diseñar el mapa de memoria, supondremos que la memoria RAM ocupa las posiciones más bajas del mapa de memoria y que la memoria ROM se encuentra a continuación.

En la siguiente figura se muestra un esquema del mapa de memoria resultante:

| $FFFFF\;h$ | Libre | 1024 K – 1 |

|------------|-------|------------|

| C0000 h    | Libre | 768 K      |

| BFFFF h    | ROM   | 768 K – 1  |

| 80000 h    | KOW   | 512 K      |

| 7FFFF h    | RAM   | 512 K – 1  |

| 00000 h    | KAW   | 0          |

Finalmente, la distribución del mapa de memoria resultante es la que aparece en la siguiente figura:

|                    | A19 | A18 | A17    | A16 | <br>Α0     |                        |                                         |

|--------------------|-----|-----|--------|-----|------------|------------------------|-----------------------------------------|

| FFFFF h            | 1   | 1   | 1<br>0 | 1 0 | <br>1<br>0 | 1024 K –<br>1<br>768 K | Libre                                   |

| BFFFF h<br>A0000 h | 1   | 0   | 1      | 1 0 | <br>1<br>0 | 768 K – 1<br>640 K     | 2 <sup>a</sup> fila<br>pastillas<br>ROM |

| 9FFFF h<br>80000 h | 1   | 0   | 0      | 1 0 | <br>1 0    | 640 K – 1<br>512 K     | 1ª fila<br>pastillas<br>ROM             |

| 7FFFF h<br>40000 h | 0   | 1   | 1<br>0 | 1 0 | <br>1<br>0 | 512 K – 1<br>256 K     | 2ª fila<br>pastillas RAM                |

| 3FFFF h<br>00000 h | 0   | 0   | 1 0    | 1 0 | <br>1 0    | 256 K – 1<br>0         | 1ª fila<br>pastillas RAM                |

Para poder direccionar las 256 Kpalabras (=  $2^{18}$  Kpalabras) de cada una de las pastillas de memoria RAM necesitaremos 18 bits, que se corresponden con las líneas  $A_{17}..A_0$  del bus de direcciones. Mientras que para poder acceder a las 128 Kpalabras (=  $2^{17}$  Kpalabras) de cada una de las pastillas de memoria ROM necesitaremos 17 bits, son las líneas  $A_{16}..A_0$  del bus de direcciones.

Las líneas  $A_{19}$  y  $A_{18}$  del bus de direcciones, nos permitirán seleccionar la fila de pastillas sobre la que se realizará la lectura o escritura de los datos.

Por otro lado, la primera pastilla de cada fila del mapa de memoria almacenará la parte alta de una palabra y la segunda la parte alta.

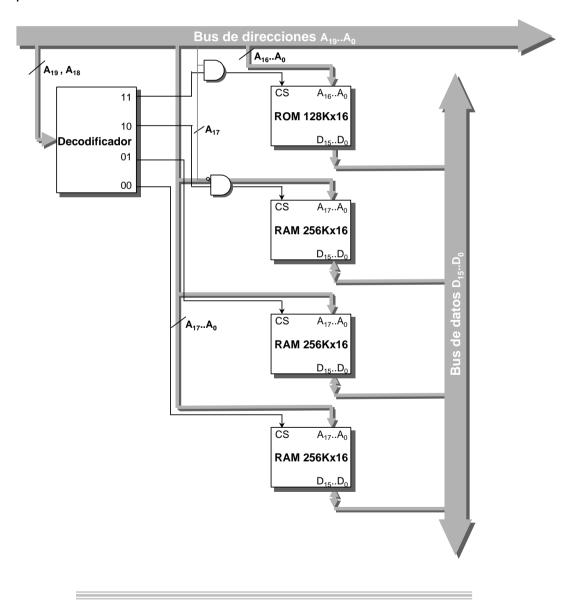

#### 4. Dibujar el esquema del mapa de memoria

Utilizando un decodificador de 3 entradas, líneas A<sub>19</sub> .. A<sub>17</sub>.

Debemos considerar que en el esquema falta una línea de lectura conectada a todas las pastillas de memoria RAM y ROM y una línea de escritura conectada a todas las pastillas de memoria RAM.

Se utiliza un decodificador de tres entradas (A<sub>19</sub>..A<sub>17</sub>) y dos puertas OR para seleccionar las filas de pastillas de memoria RAM.

Las filas de memoria ROM se seleccionan con las salidas del decodificador 101 y 100.

### Solución ejercicio 2

#### 1. Comprobar que existe solución

El bus de direcciones tiene 20 líneas, desde la A<sub>19</sub> hasta la A<sub>0</sub>, lo que supone una capacidad de direccionamiento de 2<sup>20</sup> palabras = 1 Mpalabras. En el caso que nos ocupa, necesitamos direccionar 640 Kpalabras de memoria RAM y 128 Kpalabras de memoria ROM, en total 768 Kpalabras. Por lo tanto, vemos que con los 20 bits del bus de direcciones sí es posible.

#### 2. Calcular los módulos de memoria que serán necesarios

Para la memoria RAM, disponemos de los siguientes módulos de memoria:

128 K x 1

$$\frac{640 \text{ K}}{128 \text{ K}} \times \frac{16 \text{ bits}}{1 \text{ bit}} = 5 \times 16 = 80 \text{ pastillas de } 128 \text{ K} \times 1$$

256 K x 8

$$\frac{640 \text{ K}}{256 \text{ K}} \times \frac{16 \text{ bits}}{8 \text{ bits}} = 3 \times 2 = 6 \text{ pastillas de } 256 \text{ K} \times 8$$

256 K x 16

$$\frac{640 \text{ K}}{256 \text{ K}} \times \frac{16 \text{ bits}}{16 \text{ bits}} = 3 \times 1 = 3 \text{ pastillas de } 256 \text{ K} \times 16$$

Para la memoria ROM, disponemos de los siguientes módulos de memoria:

128 K x 1

$$\frac{128 \text{ K}}{128 \text{ K}} \times \frac{16 \text{ bits}}{1 \text{ bit}} = 1 \times 16 = 16 \text{ pastillas de } 128 \text{ K} \times 1$$

64 K x 8

$$\frac{128 \text{ K}}{64 \text{ K}} \times \frac{16 \text{ bits}}{8 \text{ bits}} = 2 \times 2 = 4 \text{ pastillas de } 64 \text{ K} \times 8$$

128 K x 16

$$\frac{128 \text{ K}}{128 \text{ K}} \times \frac{16 \text{ bits}}{16 \text{ bits}} = 1 \times 1 = 1 \text{ pastilla de } 128 \text{ K} \times 16$$

3 x 1 = 3 pastillas de 256 K x 16 para la memoria RAM

- 1 x 1 = 1 pastilla de 128 K x 16 para la memoria ROM

- 3. Diseñar el mapa de memoria

| FFFFF h | ROM    | 1024 K – 1 |

|---------|--------|------------|

| E0000 h | KOIVI  | 896 K      |

| DFFFF h | Libre  | 896 K – 1  |

| A0000 h | LIDIE  | 640 K      |

| 9FFFF h | RAM    | 640 K – 1  |

| 00000 h | IXAIVI | 0          |

|         |        |            |

|                    | A19  | A18   | A17    | A16     |        | A0  |                    |                                        |    |

|--------------------|------|-------|--------|---------|--------|-----|--------------------|----------------------------------------|----|

| FFFFF h<br>E0000 h | 1    | 1     | 1      | 1       |        | 1   | 1024 K –1<br>896 K | Fila<br>pastillas<br>ROM               |    |

| DFFFF h<br>C0000 h | 1    | 1     | 0      | 0       |        | 1   | 896 K –1<br>768 K  | Libre                                  |    |

| BFFFF h<br>A0000 h | Zona | de RA | M no d | direcci | onable |     | 768 K – 1<br>640 K |                                        |    |

| 9FFFF h<br>80000 h | 1    | 0     | 0      | 1       |        | 1   | 640 K – 1<br>512 K | 3 <sup>a</sup> fil<br>pastillas<br>RAM | la |

| 7FFFF h<br>40000 h | 0    | 1     | 1      | 0       |        | 1   | 512 K – 1<br>256 K | 2 <sup>a</sup> fil<br>pastillas<br>RAM | la |

| 3FFFF h<br>00000 h | 0    | 0     | 1 0    | 1       |        | 1 0 | 256 K – 1<br>0     | 1 <sup>a</sup> fil<br>pastillas<br>RAM | la |

Como puede observarse en el mapa de memoria, la tercera fila de pastillas de memoria RAM no se utiliza de manera completa.

Para poder direccionar las 256 Kpalabras (=  $2^{18}$  Kpalabras) de cada una de las pastillas de memoria RAM necesitaremos 18 bits, que se corresponden con las líneas  $A_{17}..A_0$  del bus de direcciones. Mientras que para poder acceder a las 128 Kpalabras (=  $2^{17}$  Kpalabras) de cada una de las pastillas de memoria ROM necesitaremos 17 bits, son las líneas  $A_{16}..A_0$  del bus de direcciones.

Las líneas  $A_{19}$  y  $A_{18}$  del bus de direcciones, nos permitirán seleccionar la fila de pastillas sobre la que se realizará la lectura o escritura de los datos.

#### 4. Dibujar el esquema del mapa de memoria

En la siguiente figura se muestra el esquema correspondiente a utilizar un decodificador de 2 entradas, líneas A<sub>19</sub> .. A<sub>18</sub>.. Debemos considerar que faltaría añadir una línea de lectura conectada a todas las pastillas de memoria RAM y ROM y una línea de escritura conectada a todas las pastillas de memoria RAM.

# Solución ejercicio 3 Apartado a)

Dado que el contenido de la memoria se podrá cambiar a petición del cliente y que el contenido de la memoria debe permanecer aunque se cambie la pila, se necesitará una memoria permanente de tipo EEPROM.

#### Apartado b)

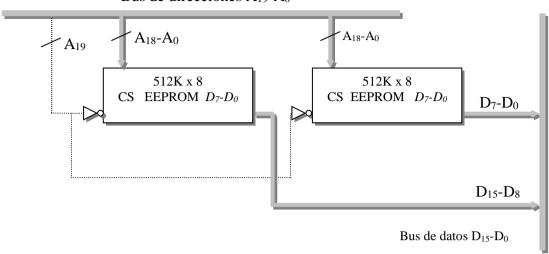

En los dos casos, las especificaciones de memoria, nos dan una necesidad de 512K.

Como el bus de direcciones es de 20 bits que permite direccionar un máximo de 1M x 16. podremos direccionar los 512K que nos piden (solamente 19 bits A18-A0)

El menor número de módulos de memoria, dado que tenemos que escoger la opción de módulos EEPROM se da con dos módulos de 512K x 8 (tipo EEPROM)

#### Apartado c)

El mapa de memoria es el que se requiere para poder direccionar una pastilla de 512Kx8 de EEPROM. Es decir, tendré una fila formada por dos pastillas de memoria que se direccionarán a la vez, una contendrá los 8 bits superiores y otra los 8 bits inferiores de cada dirección.

|         | A19 | A18 | <br>A0 |           |                     |

|---------|-----|-----|--------|-----------|---------------------|

| FFFFF h | 1   | 0   | 1      | 1024 K –1 | Libre               |

| 80000 h |     | 1   | <br>0  | 512 K     | Libre               |

| 7FFFF h |     | 0   | 1      | 512 K – 1 | Fila de             |

| 00000 h | 0   | 1   | <br>0  | 0 K       | pastillas<br>EEPROM |

#### Bus de direcciones A<sub>19</sub>-A<sub>0</sub>