### Arquitectura y Organización de Computadores

TEMA 3

Aspectos básicos

en la

organización del

computador

### **Objetivos**

#### **Generales**

- Conocer la estructura básica de un computador

- Conocer la función básica de cada uno de los subsistemas principales que forman un computador

#### **Específicos**

- Describir la estructura básica de un ordenador y las diferencias entre la Arquitectura Von Neumann y la Harvard

- Describir las diferentes fases en que se divide la ejecución de una instrucción y explicar el concepto de ciclo de reloj.

- Explicar las funciones del procesador y os componentes principales que lo forman

- Clasificar los distintos tipos de memoria en función de su soporte, tipo de acceso, si es de lectura

o lectura escritura y si es o no volátil

- Explicar la función del adaptador de E/S y argumentar la necesidad de usarlo

- Distinguir entre interfaz interna e interfaz externa de un adaptador de E/S y nombrar las interfaces más comunes de ambos tipos.

- Explicar los tres mecanismos básicos de E/S: programada, por interrupciones, con DMA

- Explicar las características básicas de un bus como canal de comunicación.

- Distinguir entre buses paralelos y series, con líneas dedicadas o multiplexadas.

- Explicar en qué consiste el arbitraje de un bus y por qué es necesario.

### **Contenidos**

- Estructura básica de un computador

- Arquitectura Von Neumann

- Arquitectura Harvard

- Estructura y funcionamiento básico del procesador

- Ciclo de ejecución de instrucciones

- Ejemplo: Máquina Rudimentaria

- Sistema de memoria

- Sistema de E/S

- Buses de interconexión

### Bibliografía

- Capítulos 10 y 11 del libro "Organización y Arquitectura de Computadores", de W. Stallings

- Capítulo 7 del libro "Fundamentos de computadores", Volumen 1, de R. Hermida

## Resultados de aprendizaje y evaluación

Describir la estructura básica de los equipos informáticos y el funcionamiento de sus principales componentes: procesador, sistema de memoria, sistema de E/S y buses de interconexión.

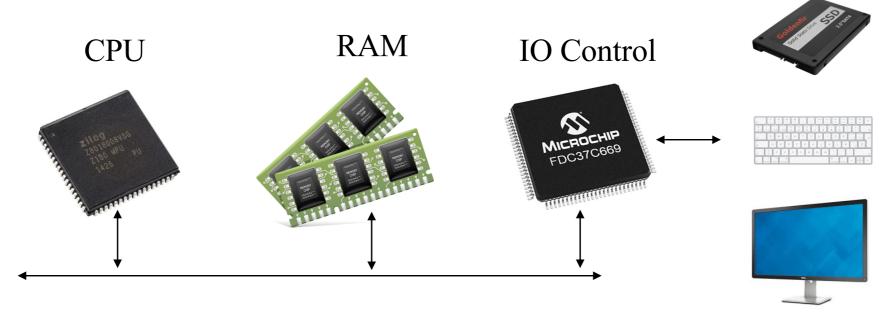

- En todo computador de propósito general pueden distinguirse 4 elementos fundamentales:

- Procesador (CPU)

- Sistema de almacenamiento (memoria)

- Sistema de entrada/salida

- Sistemas de interconexión

### **Arquitectura Von Neumann**

- A.W. Burks, H.H. Goldstine, J. Von Neumann proponen en 1946 una arquitectura para una máquina llamada IAS

- Esta arquitectura está formada por 3 módulos:

- CPU: manipulación de la información mediante la ejecución de instrucciones

- Memoria: almacenamiento de datos e instrucciones

- Unidad de Entrada/Salida: para intercambio de información con el exterior

### **Arquitectura Von Neumann**

Estructura básica (1945)

### COMPUTADOR bus de datos bus de direcciones bus de control **MEMORIA CPU** E/S Periféricos de entrada y salida de datos

Actualmente, la E/S puede tener su propio direccionamiento o estar mapeada en memoria. Lo habitual es un enfoque mixto.

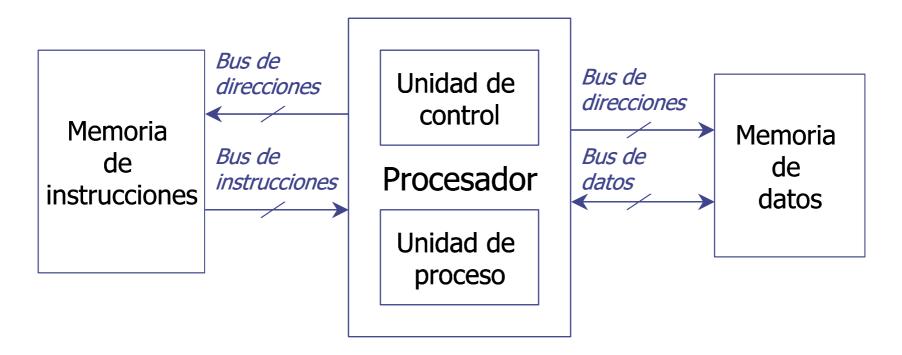

### **Arquitectura Harvard**

Memorias separadas para datos e instrucciones

Muchas implementaciones de esta arquitectura son en realidad una arquitectura Harvard modificada, que proporciona ciertos mecanismos (lentos y no para uso continuo) para acceder a la memoria de instrucciones desde la ejecución de un programa e incluso para modificar la memoria de instrucciones.

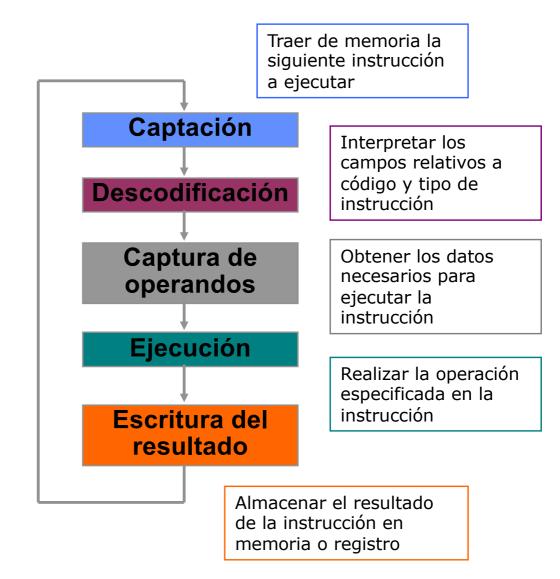

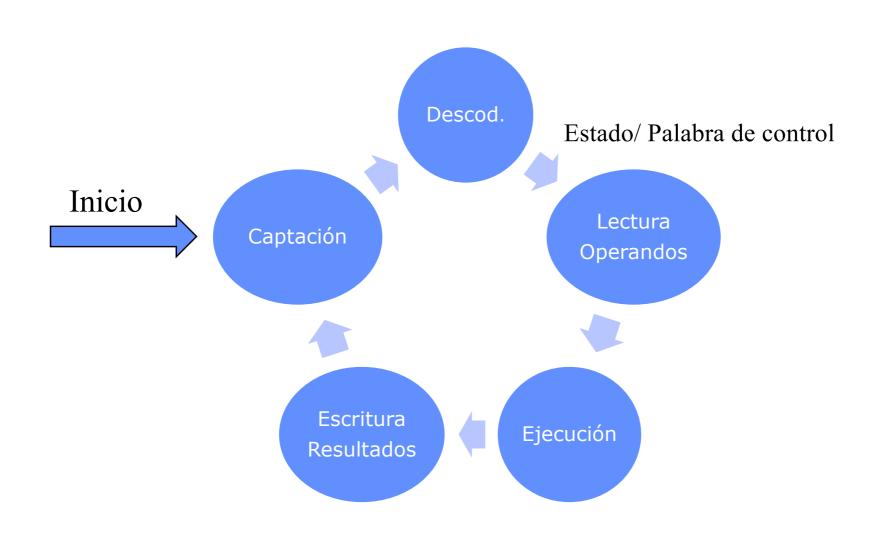

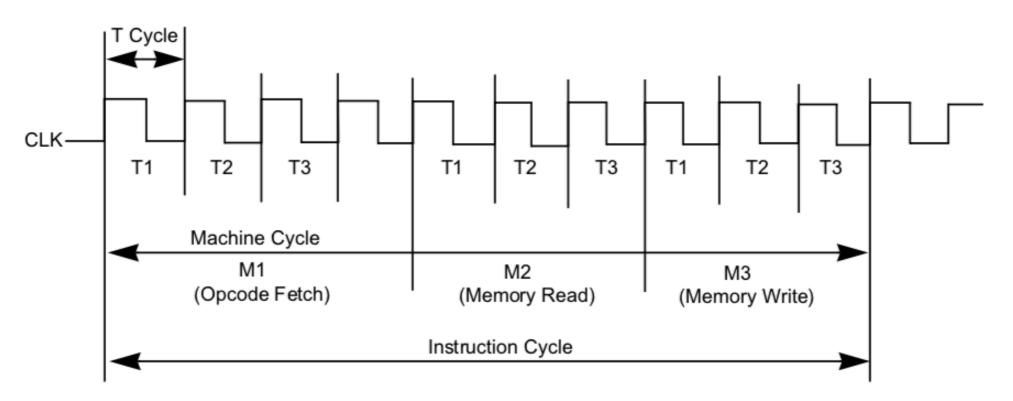

### Modelo de Ejecución

- Para ejecutar un programa hay que ejecutar las instrucciones que lo forman, una a una.

- La ejecución de cada instrucción implica comúnmente las tareas reflejadas en la figura de la derecha.

- Estas tareas se suelen realizar en etapas, donde cada etapa, a su vez, se realiza en un ciclo de reloj.

- El número de etapas y la duración de cada ciclo de reloj depende del procesador.

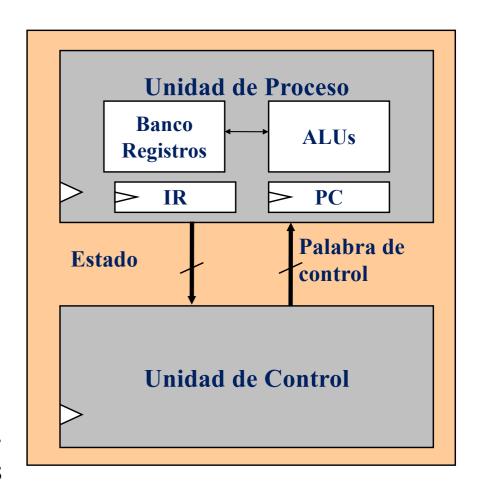

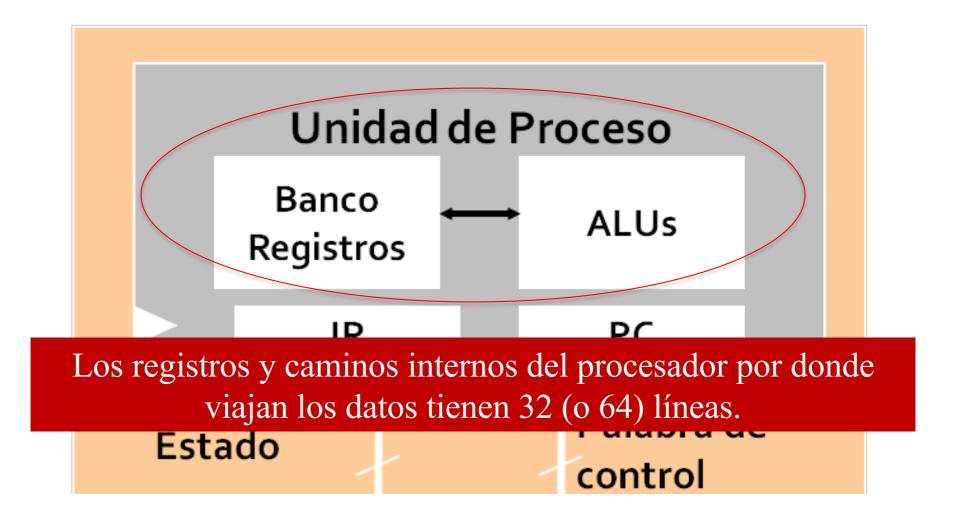

- Unidad de proceso (UP): se encarga de realizar las acciones básicas que permiten completar la ejecución de una instrucción máquina

- búsqueda de la siguiente instrucción

- descodificación

- lectura de operandos

- ejecución

- escritura del resultado

- Unidad de control (UC): se encarga de asegurar que la UP realiza las acciones básicas en la secuencia correcta, generando las señales de control (órdenes) que gobiernan su funcionamiento

#### **Unidad de Proceso**

- Principales elementos

- Unidades de ejecución (o funcionales): unidades aritméticas para enteros, unidades aritméticas para coma flotante, etc.

- Registros de propósito general: conjunto de registros que pueden utilizarse para almacenar datos de manera temporal

- Registros de control y estado: Registro de instrucciones (IR) y Contador de Programa (PC) entre otros

#### **Unidad de Control**

- Es un sistema secuencial que genera órdenes de control (palabra de control) para la Unidad de Proceso a partir de la información recibida sobre su estado

- Su comportamiento se describe habitualmente mediante diagramas de estado, donde cada estado se corresponde con una fase en la ejecución de una instrucción

#### **Unidad de Control**

#### **Unidad de Control**

- Existen dos formas de implementar la unidad de control de un procesador

- Cableada: la unidad de control es un circuito lógico generado a partir de su diagrama de estados. Es más complejo diseñarla y ampliarla para incorporar nuevas instrucciones.

- Microprogramada: la unidad de control se construye utilizando microprogramas para cada instrucción. Existe una memoria de control que tiene todas las microinstrucciones (en esencia, una por cada estado del procesador).

¿Qué significa que un procesador sea de 32 (o 64) bits?

- Implicaciones del número de bits del procesador

- Los datos enteros que se pueden operar están limitados a 32 (o 64) bits. Si se quiere operar con datos mayores, hay que hacer la operación por partes.

- Ejemplo: ADD \$1,\$2,\$3 es una instrucción del procesador MIPS R2000, que es de 32 bits. Los registros almacenan números de 32 bits, y la suma se realiza sobre esos 32 bits.

- El acceso a algunos modos de direccionamiento de registro limita la visibilidad de la memoria disponible.

El Z80 es un procesador de 8 bits, pero permite ciertas operaciones de 16bits

Evolución del número de bits del procesador

Ejemplo: microprocesadores de Intel

1971: **4004**

4 bits

1974: **8080**

8 bits

1978: **8086**

16 bits

1982: **80286**

16 bits

1985: **80386**

32 bits (IA32)

2001: Itanium

IA-64

**2004: Pentium**

4, Xeon

64 bits (EM64T)

#### Modelo básico de ejecución de bajo nivel

- 1. Generación de código máquina (compilador/ensamblador)

- 2. Carga del programa en memoria e inicio del procesador (sistema operativo)

- 3. El procesador comienza a ejecutar a partir de la primera instrucción, cuya dirección de memoria conoce

- 4. A partir de ahí continua la ejecución del resto del programa según está almacenado en memoria (excepto por los saltos y las interrupciones)

- Cada instrucción se ejecuta en varias fases, de acuerdo al diagrama de estados de la UC

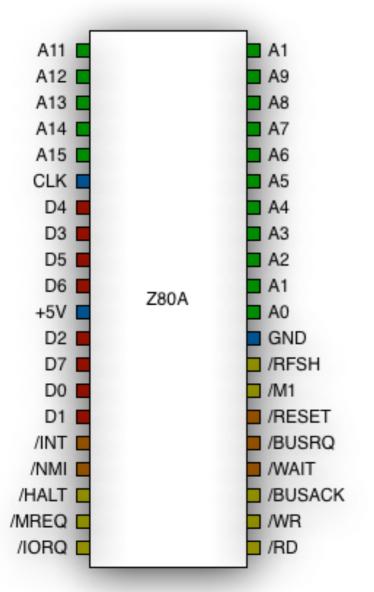

### **Z80 - Pines**

Verde: Líneas de direcciones

Rojo: Líneas de datos

Naranja: Líneas de control de entrada Amarillo: Líneas de control de salida

Azul: Alimentación

#### **Ejemplo: Leer de la dirección \$50AA:**

- ADDR = \$50AA

- /MREQ = 0

- /RD = 0

- Resto de control = 1

- → El dato lo devuelve la memoria por las líneas de datos.

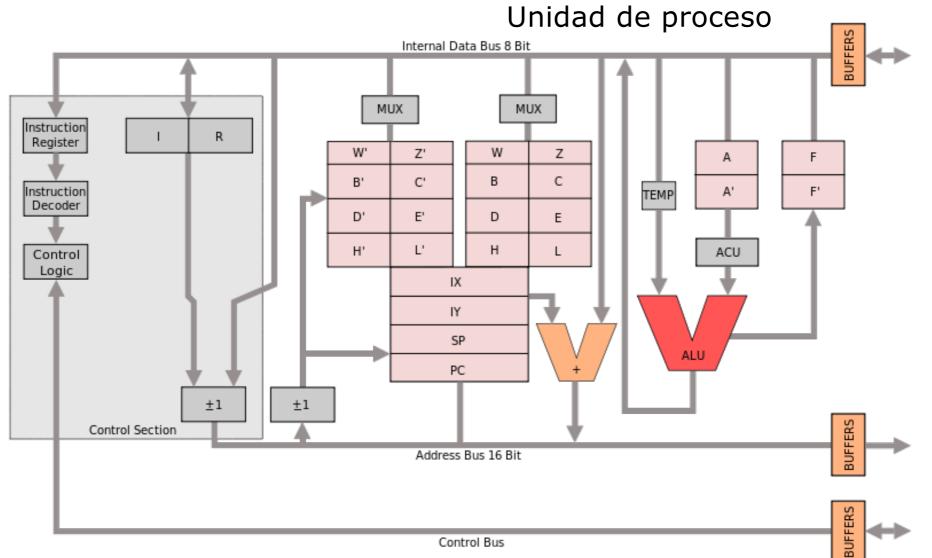

### Ejemplo: estructura del procesador Z80

Pensemos en su repertorio de instrucciones y en lo que sabemos sobre la estructura del procesador. ¿Qué elementos hacen falta en la Unidad de Proceso?

### Ejemplo: estructura del procesador del Z80

### Ejemplo: estructura del procesador Z80

- Unidad de proceso. Descripción de los elementos principales

- **Banco de registros:** estructura que contiene los registros de propósito general (B,C,D,E ...) para almacenamiento temporal de datos del programa.

- REGISTRO A y registro F: Registros para operaciones aritméticas y para flags de resultado de operaciones

- ALU: unidad aritmético-lógica, capaz de ejecutar las operaciones de suma (add, adc), resta (sub), desplazamiento (shift y rotate) y operaciones lógicas (and, or, cpl, xor, neg...) asociadas a las instrucciones aritmético-lógicas del lenguaje máquina.

- PC (contador de programa): registro que almacena la dirección de memoria de la siguiente instrucción a ejecutar.

### Ejemplo: estructura del procesador del Z80

- Unidad de proceso. Descripción de los elementos pricipales

- Instruction Register (registro de instrucción, no confundir con IR, que es Interrupt y Refresh): registro que almacena la instrucción que se está ejecutando en cada momento. La instrucción puede tener argumentos (ej JP \$AABB), esos datos se almacenan en los registros W y Z.

- Incrementadores: para incrementar el valor de distintos registros, tanto de propósito general como el contador de programa

- Otros registros: I, R, WZ, shadow : Funcionalidad detallada fuera del alcance.

- Podrían considerarse los registros de instrucción, los registros

I, R como parte de la unidad de control.

### Ejemplo: estructura del procesador del Z80

Teniendo en cuenta la unidad de proceso, ¿qué fases requiere la ejecución de cada instrucción? ¿Cuál es el diagrama de estados que representa el funcionamiento de la UC?

### Ejemplo: estructura del procesador del Z80

Unidad de control – Fases

- Información detallada en:

- http://www.msxarchive.nl/pub/msx/mirrors/msx2.com/zaks/z80prg02.htm

- http://www.zilog.com/docs/z80/um0080.pdf

### Ejemplo: estructura del procesador Z80

Instrucción LD A,(\$50AA)

| OP CODE:        |        | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> | $D_3D_2D_1D_0$ |  |

|-----------------|--------|-------------------------------------------------------------|----------------|--|

|                 |        | 0011                                                        | 1010           |  |

|                 | T1     | PC OUT STATUS                                               |                |  |

| M1 [ <u>1</u> ] | T2 [2] | PC = PC + 1                                                 |                |  |

|                 | Т3     | INST TMP/IR                                                 |                |  |

|                 | T4     | Decode - Execute                                            |                |  |

| M2              | T1     | PC OUT STATUS [6]                                           |                |  |

|                 | T2 [2] | PC = PC + 1                                                 |                |  |

|                 | Т3     | B2 <b>▶</b> Z                                               |                |  |

|                 | T1     | PC OUT STATUS [6]                                           |                |  |

| М3              | T2 [2] | PC = PC + 1                                                 |                |  |

|                 | Т3     | B3 ➤ W                                                      |                |  |

| M4              | T1     | WZ OUT STATUS [6]                                           |                |  |

|                 | T2 [2] | DATA A                                                      |                |  |

|                 | Т3     |                                                             |                |  |

Z = AA

W = \$50

ADDR = \$50AA

- Existen diferentes tipos de memoria dentro de un sistema informático, que se diferencian en características como:

- Capacidad (tamaño medido en bytes)

- Prestaciones (tiempo de acceso, tiempo de ciclo, velocidad de transferencia)

- Ubicación dentro del sistema

- **Soporte** (magnético, óptico, semiconductor)

- Modo de acceso (secuencial, directo, aleatorio)

- Características físicas (Volátil / No volátil, Lectura / Lectura-escritura)

### Capacidad

- Palabra: unidad "natural" de organización de la memoria.

Anchura de palabra: nº de bits

- Unidad direccionable: conjunto de bits que tienen asociada una dirección (normalmente 1 byte)

- Unidad de transferencia: cjto.de bits que se leen o escriben de una vez

#### Prestaciones

- Tiempo de acceso: tiempo que tarda en realizarse una operación de escritura o lectura

- Tiempo de ciclo de memoria: tiempo mínimo necesario entre dos operaciones consecutivas de lectura/escritura

- Velocidad de transferencia: velocidad a la que se pueden transferir datos a o desde memoria (se mide en bits por segundo, bps)

#### Ubicación dentro del PC

- En el mismo chip que la CPU

- Interna (principal)

- Externa (secundaria)

#### Método de acceso

- Secuencial: el acceso al dato es secuencial, es decir, hay que recorrer todos los datos desde el comienzo hasta llegar al dato buscado: el tiempo de acceso no es constante, depende de la posición a la que se accede

- Directo: tiempo de acceso no constante, depende de la posición a la que se accede, aunque se accede al dato buscado directamente, sin acceder a otros previos

- Aleatorio: se accede al dato directamente, en tiempo constante, independientemente de la posición accedida

- Asociativo: se accede por contenidos en vez de por direcciones (como las anteriores), en tiempo constante independientemente de la posición accedida

### Soporte físico

- Memorias semiconductoras

- Soporte magnético

- Soporte óptico

#### Características físicas

- Volátil / No volátil: si es no volátil, mantiene los datos tras desconectar la fuente de alimentación

- De sólo lectura/ Lectura-escritura: permite borrar y escribir nuevos datos o es solo de lectura

### CLASIFICACIÓN DE ALGUNAS MEMORIAS COMUNES

| Tipo de memoria | Clase  | Borrado    | Escritura | Volátil |

|-----------------|--------|------------|-----------|---------|

| RAM             | L/E    | Eléctrico  | Eléctrica | SI      |

| ROM             | Sólo L | No         | Máscaras  | NO      |

| PROM            | Sólo L | No         | Eléctrica | NO      |

| EPROM           | Más L  | Ultraviol. | Eléctrica | NO      |

| EEPROM          | Más L  | Eléctrico  | Eléctrica | NO      |

| FLASH           | Más L  | Eléctrico  | Eléctrica | NO      |

**PROM**: ROM Programable **EPROM**: ROM Programable y borrable

**EEPROM**: ROM Programable y borrable eléctricamente

### CLASIFICACIÓN DE ALGUNAS MEMORIAS SEMICONDUCTORAS COMUNES

- ROM: el contenido se crea en el momento de fabricación del chip. Es rentable cuando se fabrican muchas memorias de igual contenido.

- PROM: el contenido se escribe 1 UNICA VEZ, pero puede hacerse tras la fabricación: la ROM se programa eléctricamente, con unos equipos especiales.

- EPROM: puede actualizarse su contenido múltiples veces: primero hay que borrar el contenido actual (todas las celdas) mediante exposición a luz ultravioleta, y a continuación escribir el nuevo contenido (programar).

- **EEPROM**: puede actualizarse su contenido byte a byte (funcionamiento similar al de una RAM, pero no volátil)

- FLASH: similar a una EEPROM, pero borra por bloques, no por bytes. Tiempo de acceso mucho mayor.

- NAND FLASH: Un tipo de flash más rápida que es la base de los SSD actuales, con variantes SLC, MLC, TLC, QLC.

- F-RAM, NVSRAM, etc...

#### **MEMORIAS SEMICONDUCTORAS**

### DRAM (RAM dinámica)

Requieren refrescos periódicos para mantener los datos almacenados. Es la tecnología que se utiliza para la memoria principal del sistema (lo que habitualmente llamamos la memoria RAM)

### SRAM (RAM estática)

No necesitan refresco, son mucho más rápidas en el acceso, pero requieren más área por chip y son más costosas. Es la tecnología utilizada en la fabricación de las memorias cachés.

| Tecnología      | Tiempo de<br>acceso | Dólares por GB<br>en 2004 |

|-----------------|---------------------|---------------------------|

| SRAM            | 0,5-2,5 ns          | \$2000-\$5000             |

| DRAM            | 50-70 ns            | \$20-\$75                 |

| Disco magnético | 5 mill-20 mill ns   | \$0,20-\$2                |

#### **ALGUNOS TIPOS DE MEMORIA DRAM**

### SDRAM (Synchronous Dynamic RAM):

Memoria síncrona (misma velocidad que el sistema)

### DDR SDRAM (Double Data Rate SDRAM):

Memoria síncrona, envía los datos dos veces por cada ciclo de reloj del bus. De este modo trabaja al doble de velocidad del bus del sistema, sin necesidad de aumentar la frecuencia de reloj.

### RDRAM (Rambus DRAM):

Memoria de gama alta basada en un protocolo propietario creado por la empresa Rambus, lo cual obliga a sus compradores a pagar royalties en concepto de uso. Esto ha hecho que el mercado se decante por la memoria DDR de uso libre, excepto algunos servidores de grandes prestaciones (Cray) y la famosa PlayStation 2.

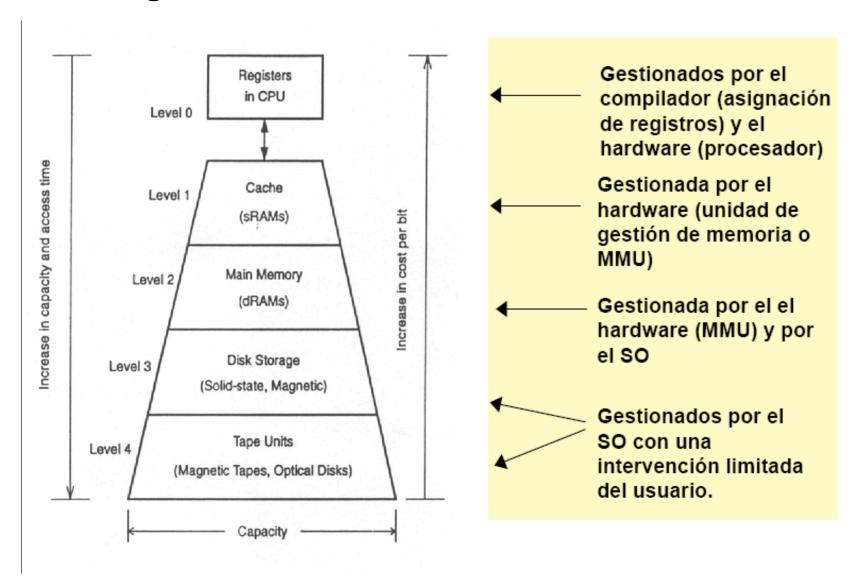

### JERARQUÍA DE MEMORIAS DEL COMPUTADOR

Periféricos: Dispositivos que permiten conectar el ordenador con el exterior. Se conectan a la Unidad Central de Proceso a través de las unidades de Entrada/Salida.

#### CLASIFICACIÓN DE PERIFÉRICOS

#### Función

#### Comunicación

- Comunicación Hombre-Máquina: Terminales

- Comunicación Impresa: Impresoras, lectores ópticos, digitalizadores

- Comunicación Máquina-Máquina: Módems y adaptadores de red

- Comunicación con un sistema físico: Periféricos de control.

#### Almacenamiento

- Discos magnéticos

- Discos ópticos

- Memorias semiconductoras: flash, SD...

#### Sentido de la comunicación:

- De entrada: teclado, escáner, ratón

- De salida: impresora, monitor

- De entrada / salida: modem, tarjeta de sonido, tarjeta de red

#### Distancia al ordenador:

- Locales

- Remotos

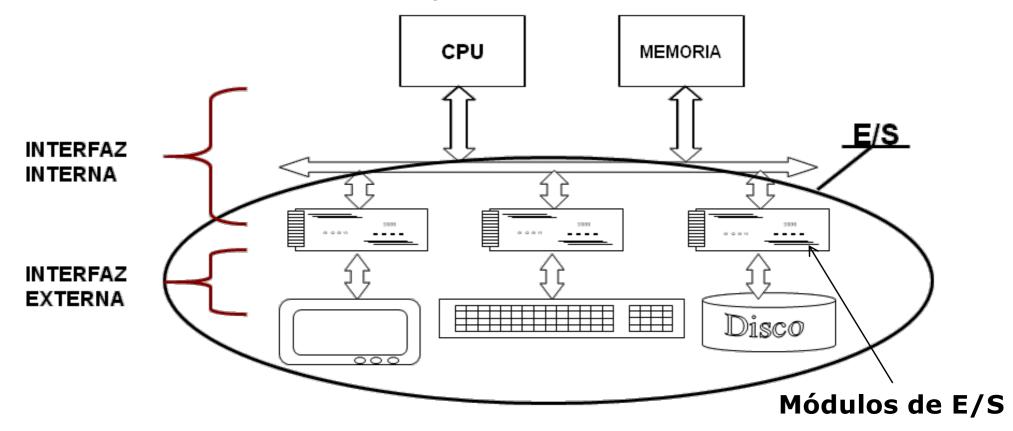

## MÓDULOS DE E/S

- Se comunican con el procesador y la memoria a través de la interfaz de E/S interna (tipos de buses)

- Se comunican con el periférico a través de la interfaz de E/S externa (serie, paralela, FireWire, USB...)

#### Funciones

- Control y sincronización

- Comunicación con el procesador

- Comunicación con el dispositivo

- Almacenamiento temporal de datos

- Detección de errores

### Módulos de E/S

### Control y sincronización:

- Coordinar el tráfico entre los recursos internos y los dispositivos externos, ajustando las diferentes velocidades de trabajo y la conversión de formatos.

- Ejemplo: operación de E/S para la lectura de un dato a través de un dispositivo de entrada

- El procesador pregunta por el estado del dispositivo

- El módulo de E/S devuelve el estado

- Si el dispositivo está listo, el procesador solicita la transferencia del dato mediante una orden al módulo de E/S

- El módulo de E/S obtiene el dato del dispositivo externo y lo transfiere al procesador

## Módulos de E/S

- Comunicación con el procesador

- Reconocimiento de la dirección, asociada a cada dispositivo de E/S

- Información de estado del dispositivo

- Decodificación de órdenes enviadas desde el procesador por el bus de control (por ejemplo, para el controlador de disco las órdenes serían "leer sector", "escribir sector", "buscar número de pista", etc.)

- Intercambio de datos entre la CPU y el módulo de E/S a través del bus de datos.

### Módulos de E/S

- Comunicación con el dispositivo:

- Implica intercambio de órdenes, datos e información del estado

- Almacenamiento de datos (data buffering)

- Necesaria debido a la diferencia de velocidad de transferencia a través de las interfaces internas y externas (varios órdenes de magnitud)

- Envío de datos de CPU o Memoria al periférico: se almacenan para ser enviados al periférico a su velocidad de trabajo

- Envío desde el periférico: se almacenan para no mantener ocupada a la memoria en una operación de transferencia lenta.

## Módulos de E/S

#### Detección de errores

- Deben detectarse e informar de ellos al procesador

- Ejemplos de errores:

- mecánicos y eléctricos (papel atascado o pista en mal estado)

- cambios accidentales en los bits transferidos

(pueden detectarse utilizando códigos detectores de errores, como el código de paridad)

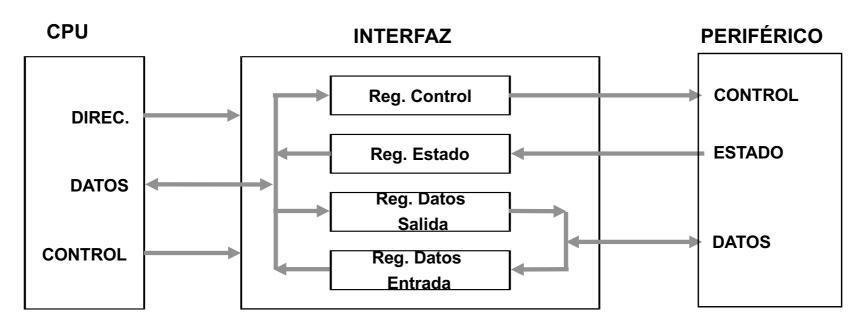

### Estructura de un Módulo de E/S

- Registro de datos de entrada: almacena los datos que envía el periférico a la CPU

- Registro de datos de salida: almacena los datos que envía la CPU al periférico

- Registro de estado: almacena el estado del periférico

- Registro de control: almacena las órdenes dadas por la CPU al periférico

#### Módulos de E/S

- En cada operación de E/S, la CPU proporciona una dirección de un dispositivo externo y una orden de E/S.

- El módulo de E/S genera las órdenes oportunas para el dispositivo correspondiente

- Tipos de órdenes al dispositivo:

- Control: para activar el periférico e indicarle qué hacer.

- Test: para comprobar diversas condiciones de estado asociadas con los periféricos.

- Lectura: el módulo de E/S capta un dato de un periférico, colocándolo en el registro de datos del módulo, donde pasará a la CPU a través del bus de datos.

- **Escritura:** el módulo E/S capta un dato del bus de datos que posteriormente transmitirá al periférico

- Existen dos alternativas para la asignación de direcciones a dispositivos:

- E/S aislada (port-mapped I/O)

- Se dispone de espacios de direcciones independientes (líneas de direcciones y control duplicadas para operaciones de L/E de memoria y de E/S).

- Existen instrucciones específicas para E/S de datos.

- Facilita la protección de la E/S.

- Ejemplo de uso: familia x86 de Intel

- E/S mapeada en memoria (memory-mapped I/O)

- Existe un único espacio de direcciones para las posiciones de memoria y los dispositivos de E/S.

- Los registros de estado y de datos de los módulos de E/S son considerados por la CPU como posiciones de memoria, y se utilizan las mismas instrucciones para acceder a memoria o a dispositivos de E/S.

- Los conjuntos de direcciones en los que se distribuyen los dispositivos de E/S se denomina mapa de E/S.

- Estas direcciones de E/S se agrupan en una zona superior o inferior de memoria para evitar confusión.

- Ejemplo de uso: familia 68k de Motorola

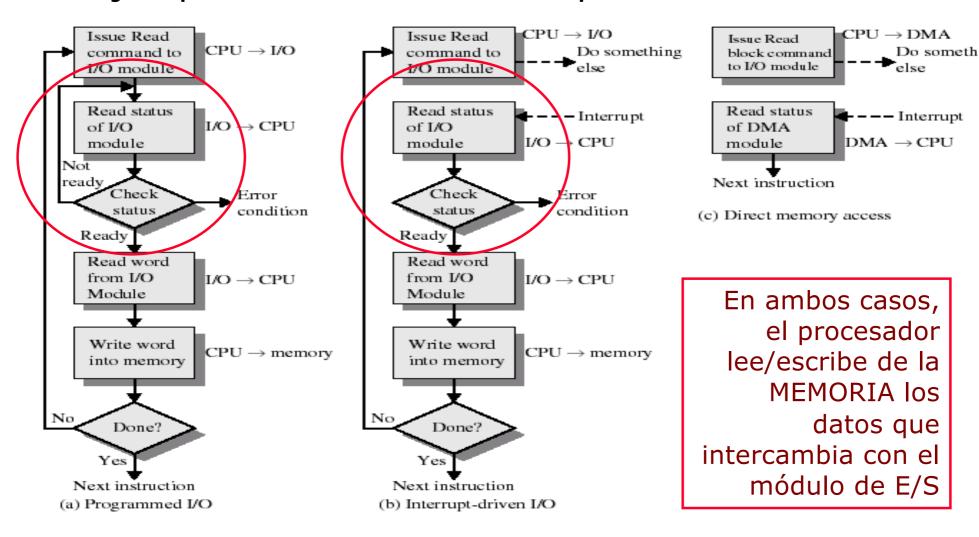

- Existen 3 técnicas de E/S principales:

- E/S programada

- La operación de E/S se produce bajo el control directo y continuo del programa que la solicita

- E/S mediante interrupciones

- El programa genera una orden de E/S y después continua ejecutándose hasta que el dispositivo interrumpe para indicar que la operación ha concluido

- Acceso directo a memoria (DMA)

- Un procesador de E/S toma el control de la operación para transferir un gran bloque de datos entre el dispositivo y la memoria principal, sin intervención de la CPU

Ejemplo: entrada de un bloque de datos

- Bus: Canal de comunicación normalmente compartido entre varios dispositivos

- Está formado por múltiples líneas, cada una capaz de transmitir un bit de información. Existen tres tipos de líneas:

- De direcciones: por ellas se transmite un número que representa la ubicación de los datos en otro lugar del computador

- De datos: transmiten los contenidos intercambiados entre dos componentes (pueden ser datos o instrucciones)

- De control: transmiten información de control relacionada con la operación que hay que realizar en cada momento

- Si bien lógicamente siempre existen esos tres tipos de líneas (porque siempre hay necesidad de transmitir esos tres tipos de información), no siempre existen físicamente.

- Bus con líneas dedicadas: Cuando sí existen líneas distintas para datos, direcciones y control

- Bus con líneas multiplexadas: Las líneas existentes no tienen un uso exclusivo, sino que en cada momento se utilizan para transmitir un tipo de información (datos, direcciones o control).

- Respecto a las líneas de datos, los buses se distinguen entre paralelos (varias líneas para el envío de datos) o series (una única línea por la que se va transmitiendo bit a bit).

#### Sistema de Arbitraje de un bus

- Dado que el bus es un canal de comunicación compartido, que puede ser usado por varios componentes distintos, es necesario establecer un orden en el uso del bus.

- No todos los componentes conectados al bus pueden solicitar el uso del mismo para iniciar una operación

- Bus master: componentes que pueden solicitar el uso del bus (CPU, DMA)

- Bus slave: componentes que responden a una petición de comunicación, utilizando el bus, pero no pueden solicitar su uso (memoria, módulo E/S)

- Cuando existe más de un master conectado a un bus (esquema multi-master), se utilizan los protocolos de arbitraje para coordinar los accesos al bus.

#### Transferencia de datos en un bus

- Ciclo de bus: una transferencia completa implica

- Direccionamiento del módulo de E/S

- Especificación del tipo de operación (lectura o escritura)

- Transferencia del dato propiamente dicha

- Finalización del uso del bus