# PROBLEMAS DE FUNDAMENTOS DE TECNOLOGÍA DE COMPUTADORES

T5. MEMORIAS

# Base teórica

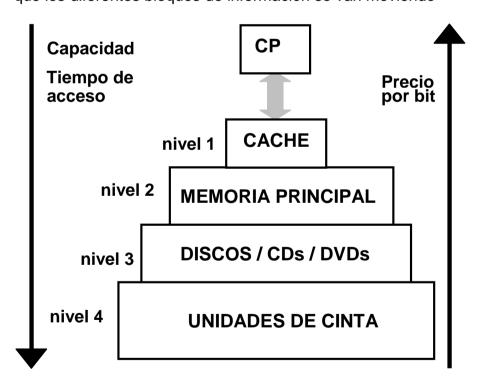

La memoria es el lugar en el que se almacenan las instrucciones y los datos para que se puedan ejecutar los programas. Sin embargo, el sistema de memoria del computador está formado por varios tipos de memorias con diferentes capacidades y tiempos de acceso. La idea es que parezca que las referencias a memoria se sirven a velocidades cercanas a las de los registros del procesador, y que además se tiene un espacio de memoria casi ilimitado para los programas y los datos. La memoria caché es la responsable de la rapidez de los accesos y la memoria virtual la de la gran capacidad del sistema de memoria.

Para que todo el sistema funcione, se diseña de manera jerárquica, por el que los diferentes bloques de información se van moviendo

Figura 1: jerarquía de memoria

## Memoria principal

Centrándose en la memoria principal, se distinguen dos grupos de memorias:

- Memorias de las que solamente se puede leer (ROM)

- Memorias en las que se puede leer y escribir (RAM)

La capacidad de la memoria principal se mide en cuantos bytes o palabras es capaz de almacenar. La manera habitual es indicar *nn*K x *mm* en el que *nn* son el número de direcciones que tiene la memoria con capacidad para poder almacenar *mm* bits en cada una.

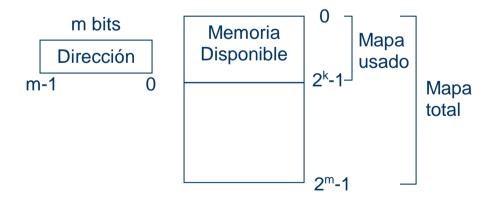

La capacidad de memoria viene dada por el bus de direcciones que establece el máximo número de posiciones direccionables por el computador. Si se tienen n bits para el bus de direcciones, se podrá acceder hasta un máximo de  $2^n$  posiciones.

Independientemente de cuanta memoria sea capaz de direccionar, los computadores no los entregan con el máximo de memoria disponible, por lo que habrá que definir como se accede a las posiciones ocupadas y a las que no están disponibles. Esa información se encuentra en el mapa de memoria del computador.

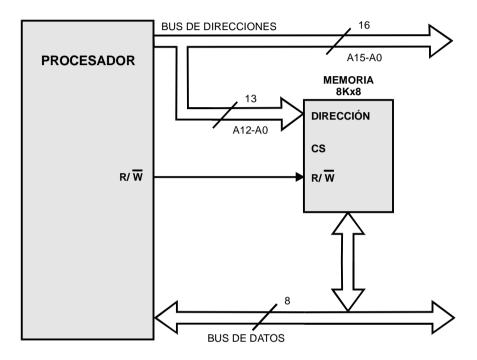

Figura 2: esquema de memoria de un computador.

Las medidas más empleadas para la capacidad de memoria son:

- Kilobyte (KB) = 2<sup>10</sup> bytes

- Megabyte (MB) = 2<sup>20</sup> bytes

- Gigabyte (GB) =  $2^{30}$  bytes

- Terabyte (TB) =  $2^{40}$  bytes

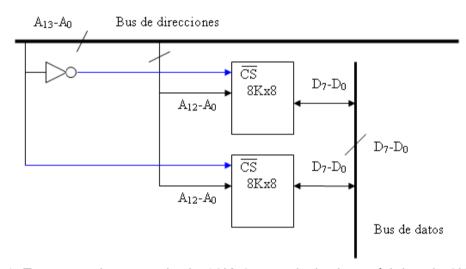

# Aumento de la memoria en número de direcciones

Si se desea una memoria de 16Kx8 a partir de módulos de memoria de 8Kx8 para un procesador con un bus de direcciones de 14 bits, se tendrá que definir cuando se accede a un módulo o al otro.

| 0<br>8K-1   | Módulo 0 de 8Kx8 |

|-------------|------------------|

| 8K<br>16K-1 | Módulo 0 de 8Kx8 |

Figura 3. Esquema de memoria solicitado

Lo primero es ver si podemos direccionar 16K con 14 bits. Para ello, se sabe que  $16K = 2^{14}$  con lo que si se pueden direccionar los 16K.

Para calcular cuantos módulos hacen falta, en este caso es muy sencillo y se ve a simple vista, se realiza la operación siguiente:

$$\frac{16k}{8k}x\frac{8}{8} = 2x1 = 2 \text{ m\'odulos de } 8kx8$$

De la ecuación anterior se desprende que se necesitan dos módulos, tal y como reflejaba la figura 3.

Ahora se tiene que ver cuando se accede a un módulo o al otro. Ya que los dos módulos son de 8K, se necesitarán 13 bits del bus de direcciones para poder direccionar en cada módulo esos 8K (=2<sup>13</sup>). De esa forma, nos queda únicamente un bit para determinar cuando se accede al módulo cero o al módulo uno.

La información de cómo acceder a los módulos se da en el mapa de memoria, tal y como muestra la tabla siguiente:

| Ŀ | A <sub>13</sub> | $A_{12}$ | $A_{11}$ | $A_{10}$ | A9 | Α8 | A7 | $A_6$ | $A_5$ | Α4  | $A_3$ | $A_2$ | $A_1$ | $A_0$ | Módulo |

|---|-----------------|----------|----------|----------|----|----|----|-------|-------|-----|-------|-------|-------|-------|--------|

|   | 1               | 1        | 1        | 1        | 1  | 1  | 1  | 1     | 1     | 1   | 1     | 1     | 1     | 1     | Módulo |

|   | 1               | 0        | 0        | 0        | 0  | 0  | 0  | 0     | 0     | : 0 | 0     | 0     | 0     | 0     | 1      |

|   | ٥               | 1        | 1        | 1        | 1  | 1  | 1  | 1     | 1     | 1   | 1     | 1     | 1     | 1     | Módulo |

|   | ٥               | 0        | 0        | 0        | 0  | 0  | 0  | 0     | 0     | 0   | 0     | 0     | 0     | 0     | 0      |

Tabla 1: mapa de memoria de 16Kx8 a partir de dos módulos de 8Kx8

El esquema de memoria quedaría:

Figura 4 .Esquema de memoria de 16Kx8 a partir de dos módulos de 8Kx8

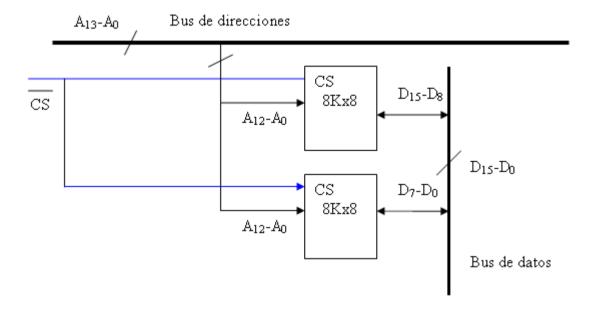

## Aumento de la memoria en el ancho de palabra

Si se desea una memoria de 16Kx16 a partir de módulos de memoria de 16Kx8 para un procesador con un bus de direcciones de 14 bits, se tendrá que definir cuando se accede a un módulo o al otro y cuantos módulos harán falta.

$$\frac{16k}{16k}x\frac{16}{8} = 1x2 = 2 \text{ m\'odulos de } 16kx8$$

En este caso, se deberá acceder a los dos módulos a la vez, dado que en un módulo se almacenarán los 8 bits superiores y en el otro los 8 bits de menor peso. El esquema quedaría de la forma:

Figura 4 .Esquema de memoria de 16Kx16 con de dos módulos de 16Kx8

También es posible aumentar el tamaño de palabra y el número de posiciones de la memoria combinando los dos esquemas anteriores.

# **EJERCICIOS T5**

- Una CPU cuenta con un ancho de palabra de 16 bits. Se quiere dotar a esa CPU de una memoria con las siguientes características:

- 256 Kpalabras (256 K x 16) de memoria ROM.

- 512 Kpalabras (512 K x 16) de memoria RAM.

Diseñar la memoria con el menor número de pastillas, sabiendo que disponemos de las siguientes y que deseamos que la RAM ocupe las posiciones más bajas del mapa de memoria, seguida de la ROM:

| Pastillas de memoria ROM | Pastillas de memoria RAM |

|--------------------------|--------------------------|

| 64 K x 8                 | 128 K x 1                |

| 128 K x 1                | 256 K x 8                |

| 128 K x 8                |                          |

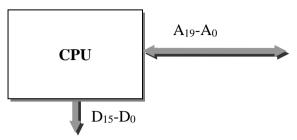

- 2. La CPU de la figura se conecta al bus de datos con 16 bits, además, el bus de direcciones cuenta con 20 bits. Se quiere dotar a esa CPU de una memoria, sin multiplexación de buses, con las siguientes características:

- 128 Kpalabras (128K x 16) de memoria ROM.

- 640 Kpalabras (640K x 16) de memoria RAM.

La memoria ROM debe situarse en las posiciones más altas del mapa de memoria direccionable y la memoria RAM debe situarse en las posiciones más bajas.

Diseñar la memoria con el menor número de pastillas sabiendo que disponemos de:

| Pastillas de memoria ROM | Pastillas de memoria RAM |  |  |  |  |  |  |

|--------------------------|--------------------------|--|--|--|--|--|--|

| 64 k x 8                 | 128 k x 1                |  |  |  |  |  |  |

| 128 k x 1                | 256 k x 8                |  |  |  |  |  |  |

| 128 k x 16               | 256 k x 16               |  |  |  |  |  |  |

3. Se quiere diseñar una memoria para un circuito electrónico que se adaptará a una tarjeta de felicitación de cumpleaños de forma que al abrirla suene la melodía del cumpleaños feliz. El archivo de sonido es de tipo WAV y ocupa 384 K y el programa que reproducirá la melodía ocupará, como máximo, 128 K.

Además se tienen que tener en cuenta los siguientes puntos:

- El cliente puede pedir que el fichero de sonido sea en formato MP3 192

K con lo que el programa ocupará un máximo de 320 K. Dado que no existirán diferentes tarjetas de felicitación se deberá cambiar el contenido de la memoria.

- Se podrá cambiar las baterías sin que se pierda la información de las memorias.

Se sabe que el bus de datos es de 16 bits y el de direcciones de 20 bits y que se cuenta con los siguientes módulos de memoria disponibles para realizar el circuito:

| Memoria ROM | Memoria EEPROM | Memoria RAM |  |  |  |

|-------------|----------------|-------------|--|--|--|

| 128 K x 8   | 128 K x 8      | 128 K x 8   |  |  |  |

| 256 K x 8   | 256 K x 8      | 256 K x 8   |  |  |  |

| 512 K x 8   | 512 K x 8      | 512 K x 16  |  |  |  |

- Razonar brevemente el tipo de módulos de memoria que se deberán emplear para realizar el circuito con las especificaciones requeridas.

- Calcular el menor número de módulos necesario para realizar las especificaciones anteriores.

- c. Realizar el mapa de memoria con una capacidad máxima para almacenar el fichero de sonido (WAV o MP3) y el programa correspondiente.

4. Se desea situar el bloque de memoria de 8Kx8 mostrado en la figura 1, al principio del mapa de memoria del procesador, es decir, ocupando desde la posición 0000h a la 1FFFh. Diseñar la lógica auxiliar que controle la señal CS mediante las líneas de mayor peso del bus de direcciones no usadas en el direccionamiento de la posición interna.

Figura 1. Sistema ejercicio 1

5. Se dispone de dos módulos de memoria M1 y M2 de 256x8 de capacidad, que se desean ubicar en el mapa de memoria correspondiente a un procesador que tiene un bus de direcciones de 10 líneas y un bus de datos de ocho. M1 hay que situarlo al principio del mapa, o sea, en las 256 primeras posiciones, mientras que M2 hay que situarlo al final del mapa.

Diseñar el esquema de conexionado correspondiente.

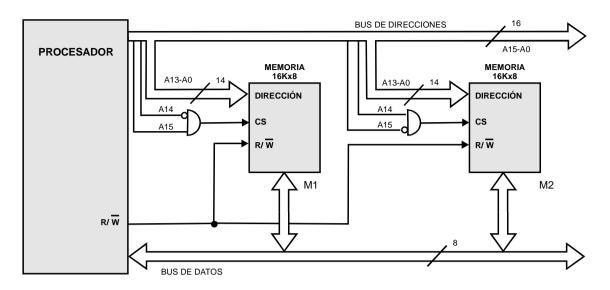

6. Se dispone de un subsistema de memoria como el mostrado en la figura 2. Averiguar el rango de direcciones a los que corresponden los módulo M1 y M2.

Figura 2. Sistema ejercicio 10

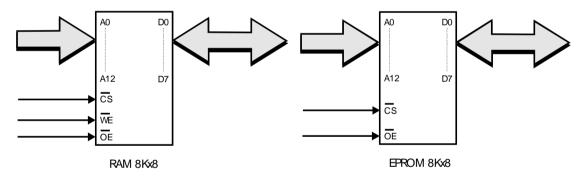

7. Se desea dotar a un sistema microprocesador basado en una CPU de 16 bits de datos y 16 bits de direcciones, de un banco de memoria RAM de 16 kpalabras y un banco de memoria EPROM de 8 kpalabras. Para ello se dispone de circuitos integrados como los mostrados en las figuras 3a y 3b.

Figura 3a. Memoria RAM

Figura 3b. Memoria EPROM

La CPU tiene una línea de lectura y una de escritura, ambas activas a nivel bajo ( $\overline{RD}$  y  $\overline{WR}$  respectivamente). Los rangos de direcciones que se desean para ambos bancos son los siguientes:

|       | Dirección inicio | Dirección fin |

|-------|------------------|---------------|

| RAM   | 2000h            | 5FFFh         |

| EPROM | 8000h            | 9FFFh         |

- a) Diseñar el sistema de memoria que se pide empleando puertas lógicas para el circuito decodificador de direcciones.

- b) Diseñar el mismo sistema que en el apartado anterior pero recurriendo al decodificador 3 a 8 74LS138 (figura 4).

|     | 74LS             | <b>1138</b>                                                  |                      |

|-----|------------------|--------------------------------------------------------------|----------------------|

| 1   | Α                |                                                              | 15                   |

| 3 6 | B<br>C           | Y0 O<br>Y1 O<br>Y2 O<br>Y3 O<br>Y4 O<br>Y5 O<br>Y6 O<br>Y7 O | 14<br>13<br>12<br>11 |

| 4 0 | G1<br>G2A<br>G2B | Y5 O<br>Y6 O<br>Y7 O                                         | 10<br>9<br>7         |

|               | Inputs      | Outputs |   |   |    |    |           |            |            |    |            |            |

|---------------|-------------|---------|---|---|----|----|-----------|------------|------------|----|------------|------------|

| Enable Select |             |         |   |   |    |    |           | Juli       | Juis       |    |            |            |

| G1            | G2 (Note 1) | С       | В | Α | YΟ | Y1 | <b>Y2</b> | <b>Y</b> 3 | <b>Y</b> 4 | Y5 | <b>Y</b> 6 | <b>Y</b> 7 |

| Χ             | Н           | Χ       | Χ | Χ | Н  | Н  | Н         | Н          | Н          | Н  | Н          | Н          |

| L             | X           | Х       | Х | Х | Н  | Н  | Н         | Н          | Н          | Н  | Н          | Н          |

| Н             | L           | L       | L | L | L  | Н  | Н         | Н          | Н          | Н  | Н          | Н          |

| Н             | L           | L       | L | Н | Н  | L  | Н         | Н          | Н          | Н  | Н          | Н          |

| Н             | L           | L       | Н | L | Н  | Н  | L         | Н          | Н          | Н  | Н          | Н          |

| Н             | L           | L       | Н | Н | Н  | Н  | Н         | L          | Н          | Н  | Н          | Н          |

| Н             | L           | Н       | L | L | Н  | Н  | Н         | Н          | L          | Н  | Н          | Н          |

| Н             | L           | Н       | L | Н | Н  | Н  | Н         | Н          | Н          | L  | Н          | Н          |

| Н             | L           | Н       | Н | L | Н  | Н  | Н         | Н          | Н          | Н  | L          | Н          |

| Н             | L           | Н       | Н | Н | Н  | Н  | Н         | Н          | Н          | Н  | Н          | L          |

Nota 1: G2 = G2A + G2B

Figura 4. Decodificador 3 a 8 74LS138