**NOMBRE: SOLUCIONES**

**EJERCICIO 1 - 1,25 puntos**

Se quiere realizar un circuito combinacional que calcule la resta de dos números de dos bits cada uno  $(A_1A_0 - B_1B_0)$ , expresados en binario natural. El resultado tendrá tres bits: el bit de signo S y el resultado de la resta  $R_1R_0$ , expresado en complemento a 2. Se pide:

a) Rellenar la tabla de verdad del circuito

| A1 | Α0 | B1 | В0 | S | R1 | R0 | resultado |

|----|----|----|----|---|----|----|-----------|

| 0  | 0  | 0  | 0  | 0 | 0  | 0  | 0         |

| 0  | 0  | 0  | 1  | 1 | 1  | 1  | -1        |

| 0  | 0  | 1  | 0  | 1 | 1  | 0  | -2        |

| 0  | 0  | 1  | 1  | 1 | 0  | 1  | -3        |

| 0  | 1  | 0  | 0  | 0 | 0  | 1  | 1         |

| 0  | 1  | 0  | 1  | 0 | 0  | 0  | 0         |

| 0  | 1  | 1  | 0  | 1 | 1  | 1  | -1        |

| 0  | 1  | 1  | 1  | 1 | 1  | 0  | -2        |

| 1  | 0  | 0  | 0  | 0 | 1  | 0  | 2         |

| 1  | 0  | 0  | 1  | 0 | 0  | 1  | 1         |

| 1  | 0  | 1  | 0  | 0 | 0  | 0  | 0         |

| 1  | 0  | 1  | 1  | 1 | 1  | 1  | -1        |

| 1  | 1  | 0  | 0  | 0 | 1  | 1  | 3         |

| 1  | 1  | 0  | 1  | 0 | 1  | 0  | 2         |

| 1  | 1  | 1  | 0  | 0 | 0  | 1  | 1         |

| 1  | 1  | 1  | 1  | 0 | 0  | 0  | 0         |

| A1A0<br>B1B0 | 00 | 01 | 11 | 10 |  |

|--------------|----|----|----|----|--|

| 00           | 0  | 1  | 1  | 0  |  |

| 01           | 1  | 0  | 0  | 1  |  |

| 11           | 1  | 0  | 0  | 1  |  |

| 10           | 0  | 1  | 1  | 0  |  |

|              |    |    |    |    |  |

b) Función lógica minimizada de Ro

$$R_0 = \overline{B_0} \cdot A_0 + B_0 \cdot \overline{A_0} = B_0 \oplus A_0$$

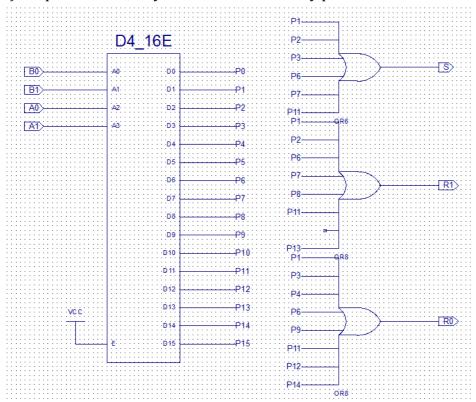

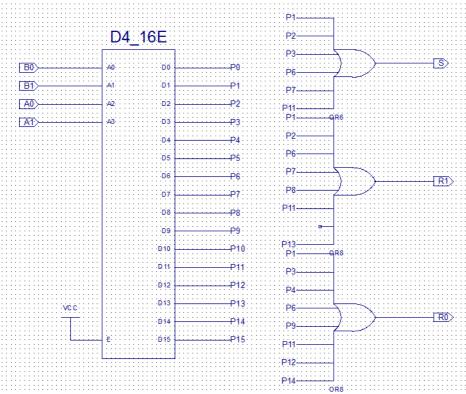

c) Implementar S, R<sub>1</sub> y R<sub>0</sub> con decodificador y puertas OR

# **EJERCICIO 2 - 1,25 puntos**

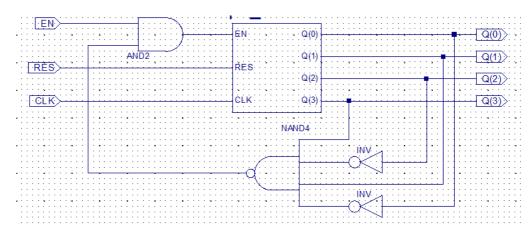

Se dispone de un contador síncrono de cuatro bits con habilitación (EN) y reset asíncrono (RES).

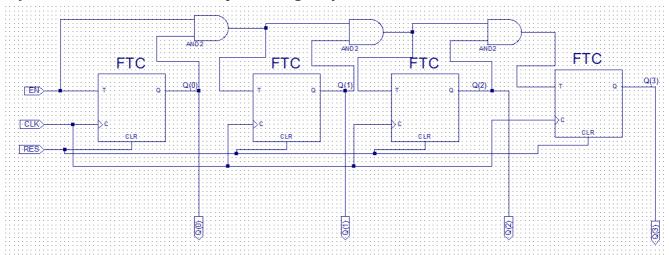

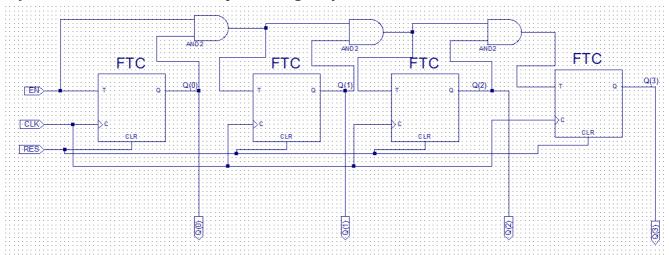

a) Diseñar el contador usando puertas lógicas y biestables

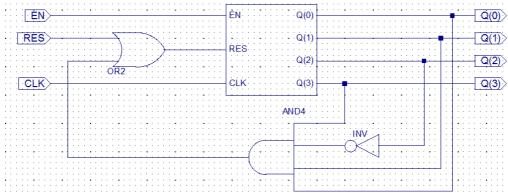

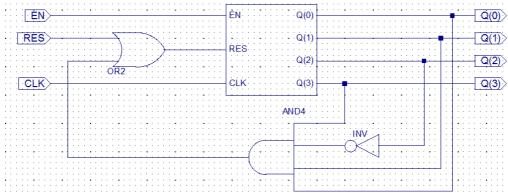

b) A partir del contador de 4 bits, añadir la lógica necesaria para que el contador cuente de 0 a 10 de manera indefinida (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 0, 1...)

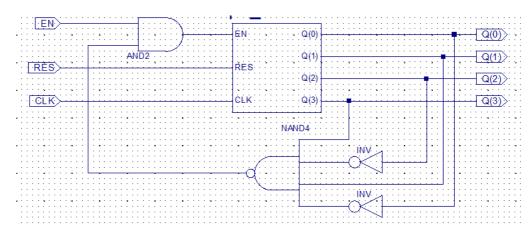

c) A partir del contador de 4 bits, añadir la lógica necesaria para que el contador cuente de 0 a 10 y luego se pare (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 10, 10, 10...)

# Test (puede haber más de una respuesta correcta) 0,5 puntos

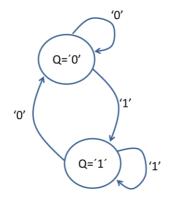

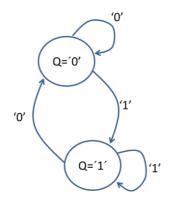

- a) El siguiente diagrama de estados corresponde a

- 1. Un biestable T

- 2. Un biestable D

- 3. Un registro de un bit

- 4. Un contador de un bit

- 5.—Ninguno de los anteriores

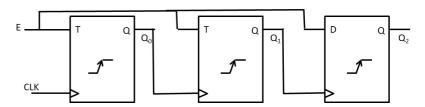

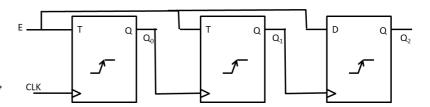

- b) El siguiente circuito es

- 1. Un registro de desplazamiento

- 2. Un detector de secuencia

- 3. Un contador

- 4. Un divisor de frecuencia

- 5. Ninguno de los anteriores

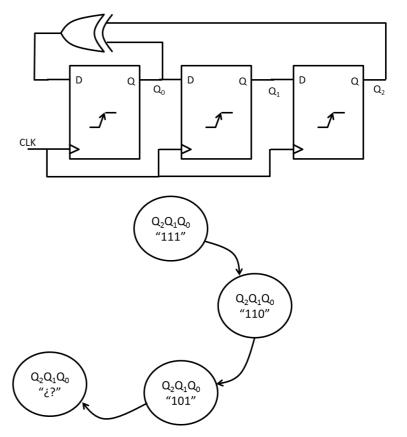

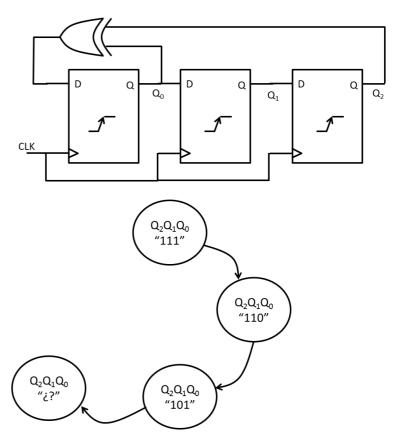

- c) El estado siguiente correspondiente al circuito de la figura, es:

- 1.  $Q_2Q_1Q_0 = "010"$

- $Q_1 = Q_2 Q_1 Q_0 = 100$

- $3.-Q_2Q_1Q_0 = "001"$

- 4.  $Q_2Q_1Q_0 = "101"$

- 5. Ninguno de los anteriores

**NOMBRE: SOLUCIONES**

**EJERCICIO 1 - 1,25 puntos**

Se quiere realizar un circuito combinacional que calcule la resta de dos números de dos bits cada uno  $(A_1A_0 - B_1B_0)$ , expresados en binario natural. El resultado tendrá tres bits: el bit de signo S y el resultado de la resta  $R_1R_0$ , expresado en complemento a 2. Se pide:

a) Rellenar la tabla de verdad del circuito

| A1 | A0 | B1 | В0 | S | R1 | R0 | resultado |

|----|----|----|----|---|----|----|-----------|

| 0  | 0  | 0  | 0  | 0 | 0  | 0  | 0         |

| 0  | 0  | 0  | 1  | 1 | 1  | 1  | -1        |

| 0  | 0  | 1  | 0  | 1 | 1  | 0  | -2        |

| 0  | 0  | 1  | 1  | 1 | 0  | 1  | -3        |

| 0  | 1  | 0  | 0  | 0 | 0  | 1  | 1         |

| 0  | 1  | 0  | 1  | 0 | 0  | 0  | 0         |

| 0  | 1  | 1  | 0  | 1 | 1  | 1  | -1        |

| 0  | 1  | 1  | 1  | 1 | 1  | 0  | -2        |

| 1  | 0  | 0  | 0  | 0 | 1  | 0  | 2         |

| 1  | 0  | 0  | 1  | 0 | 0  | 1  | 1         |

| 1  | 0  | 1  | 0  | 0 | 0  | 0  | 0         |

| 1  | 0  | 1  | 1  | 1 | 1  | 1  | -1        |

| 1  | 1  | 0  | 0  | 0 | 1  | 1  | 3         |

| 1  | 1  | 0  | 1  | 0 | 1  | 0  | 2         |

| 1  | 1  | 1  | 0  | 0 | 0  | 1  | 1         |

| 1  | 1  | 1  | 1  | 0 | 0  | 0  | 0         |

| A1A0<br>B1B0 | 00 | 01 | 11 | 10 |   |

|--------------|----|----|----|----|---|

| 00           | 0  | 1  | 1  | 0  |   |

| 01           | 1  | 0  | 0  | 1  | - |

| 11           | 1  | 0  | 0  | 1  |   |

| 10           | 0  | 1  | 1  | 0  |   |

|              |    |    |    |    |   |

b) Función lógica minimizada de Ro

$R_0 = \overline{B_0} \cdot A_0 + B_0 \cdot \overline{A_0} = B_0 \oplus A_0$

c) Implementar S,  $R_1\,y\,R_0\,con\,decodificador\,y\,puertas\,OR$

# **EJERCICIO 2 - 1,25 puntos**

Se dispone de un contador síncrono de cuatro bits con habilitación (EN) y reset asíncrono (RES).

a) Diseñar el contador usando puertas lógicas y biestables

b) A partir del contador de 4 bits, añadir la lógica necesaria para que el contador cuente de 0 a 10 de manera indefinida (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 0, 1...)

c) A partir del contador de 4 bits, añadir la lógica necesaria para que el contador cuente de 0 a 10 y luego se pare (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 10, 10, 10...)

# Test (puede haber más de una respuesta correcta) 0,5 puntos

- a) El siguiente diagrama de estados corresponde a

- 1. Un biestable D

- 2. Un biestable T

- 3. Un registro de un bit

- 4. Un contador de un bit

- 5.—Ninguno de los anteriores

- b) El siguiente circuito es

- 1. Un detector de secuencia

- 2. Un divisor de frecuencia

- 3. Un registro de desplazamiento

- 4. Un contador

- 5. Ninguno de los anteriores

- c) El estado siguiente correspondiente al circuito de la figura, es:

- 1.  $Q_2Q_1Q_0 = "101"$

- $2. Q_2Q_1Q_0 = "100"$

- $3.-Q_2Q_1Q_0 = "001"$

- 4.  $Q_2Q_1Q_0 = "010"$

- 5. Ninguno de los anteriores

Nombre:

# UNIVERSIDAD POLITÉCNICA DE MADRID ■ Escuela Técnica Superior De Ingenieros Industriales Departamento De Automática, Ingeniería Electrónica E Informática Industrial DIVISIÓN DE INGENIERÍA ELECTRÓNICA (DIE)

| 4 |   |   |

|---|---|---|

|   | A |   |

|   | А | J |

Asignatura: Fundamentos de Electrónica (ANALÓGICA)

Titulación: Grado de Ingeniería en Tecnologías Industriales

Publicación de preactas: 15/7/2015

Fecha: 1/7/2015

Nº Mat.:

**Convocatoria:** Julio 2014/15 **Revisión:**. 17/5/2015 a las 10:00h.

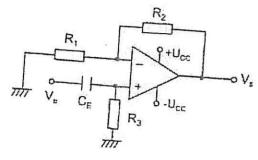

# PROBLEMA 1. (2 puntos)

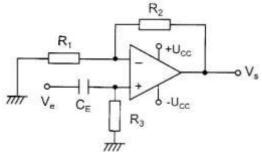

A partir del circuito de la figura, y considerando que el amplificador operacional es ideal, se pide:

#### Datos:

$R_1$ = 1 $k\Omega$ ;  $R_2$ = 10 $k\Omega$ ;  $R_3$ =1 $k\Omega$ ;  $U_{CC}$  = 15v

|    | mr                                                                                                           |

|----|--------------------------------------------------------------------------------------------------------------|

| a) | Obtener la expresión de la ganancia de tensión a frecuencias medias.                                         |

|    |                                                                                                              |

|    |                                                                                                              |

|    |                                                                                                              |

|    |                                                                                                              |

|    |                                                                                                              |

|    |                                                                                                              |

| b) | Obtener la expresión de la ganancia de tensión a frecuencias altas.                                          |

|    |                                                                                                              |

| c) | Calcular C <sub>E</sub> para que la frecuencia de corte inferior del amplificador realimentado sea de 100Hz. |

|    |                                                                                                              |

|    |                                                                                                              |

|    |                                                                                                              |

|    |                                                                                                              |

|    |                                                                                                              |

#### UNIVERSIDAD POLITÉCNICA DE MADRID • Escuela Técnica Superior De Ingenieros Industriales Departamento De Automática, Ingeniería Electrónica E Informática Industrial DIVISIÓN DE INGENIERÍA ELECTRÓNICA (DIE)

| Ī | entre tensión de salida y entrada en función de la frecuencia y dibuje el diagrama de Bode |

|---|--------------------------------------------------------------------------------------------|

|   |                                                                                            |

|   |                                                                                            |

|   |                                                                                            |

|   |                                                                                            |

|   |                                                                                            |

|   |                                                                                            |

Nº Mat.:

| 4 |   |   |

|---|---|---|

|   | A |   |

| • | A | • |

Nombre:

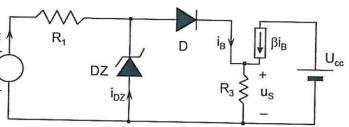

### PROBLEMA 2. (2 puntos)

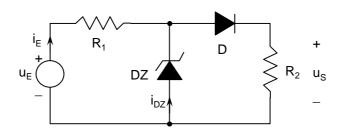

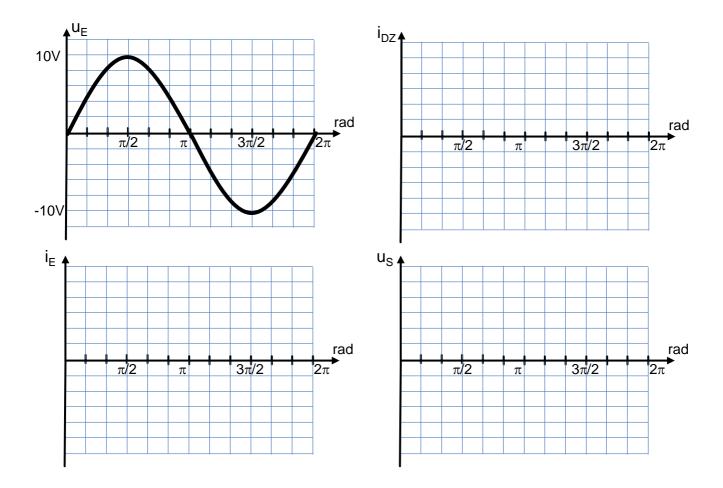

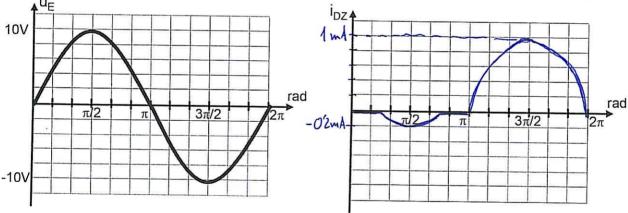

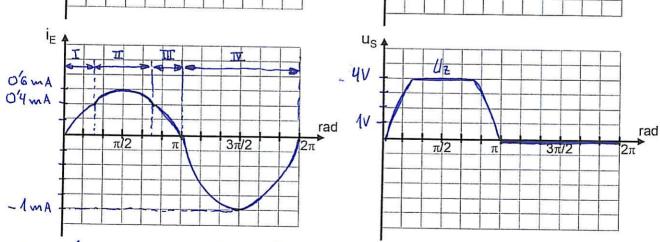

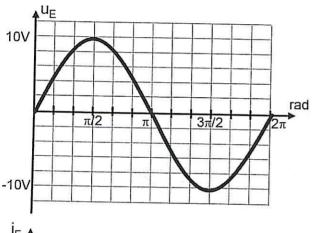

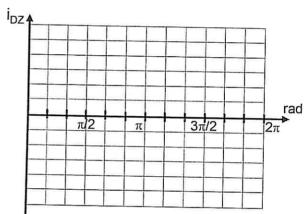

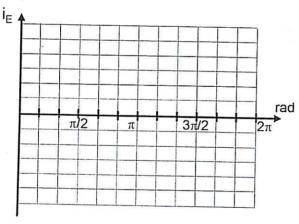

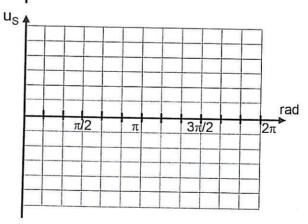

Para los circuitos de las figuras y asumiendo ideales todos los componentes, se pide dibujar la evolución en el tiempo de la corriente ( $i_E$ ) demandada a la fuente de entrada ( $u_E$ ), la corriente por el diodo Zener ( $i_{DZ}$ ) y la tensión de salida ( $u_S$ ) indicando los valores más significativos. Determinar, para cada circuito, el estado de cada uno de los diodos en los diferentes intervalos de tiempo por los que va evolucionando el circuito.

**Nota:** Dibujar en esta misma hoja la evolución de las formas de onda y sus valores más significativos, escalando cada gráfica a los valores de la forma de onda correspondiente. De igual forma, indicar el estado de los diodos en los distintos intervalos de tiempo.

A) Datos:  $R_1 = 10k\Omega$ ,  $R_2 = 10k\Omega$ ,  $U_Z = 4V$ ,  $U_E = 10sen(\omega t)V$

| <sup>o</sup> Mat.: |

|--------------------|

| o                  |

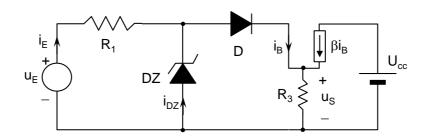

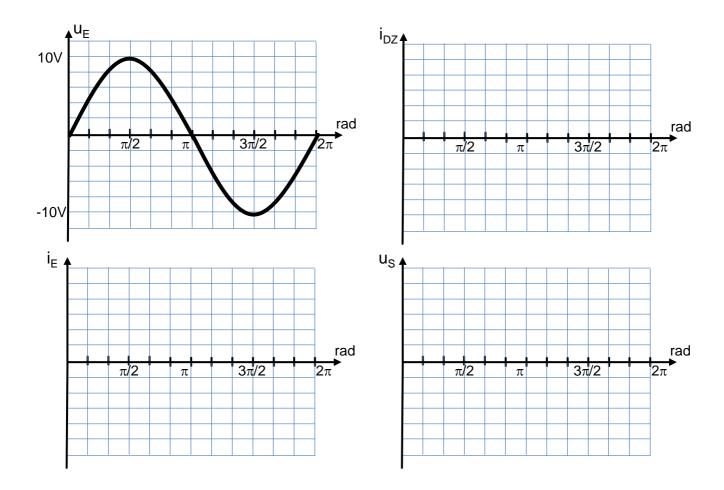

**B)** Datos:  $R_1 = 10k\Omega$ ,  $R_2 = 10k\Omega$ ,  $R_3 = 100\Omega$ ,  $U_Z = 4V$ ,  $\beta = 99$ ;  $u_E = 10sen(\omega t)V$ ;  $U_{CC} = 20V$

Nº Mat.:

Nombre:

# PROBLEMA 2. (2 puntos)

Para los circuitos de las figuras y asumiendo ideales todos los componentes, se pide dibujar la evolución en el tiempo de la corriente  $(i_E)$  demandada a la fuente de entrada  $(u_E)$ , la corriente por el diodo Zener  $(i_{DZ})$  y la tensión de salida (us) indicando los valores más significativos. Determinar, para cada circuito, el estado de cada uno de los diodos en los diferentes intervalos de tiempo por los que va evolucionando el circuito.

Nota: Dibujar en esta misma hoja la evolución de las formas de onda y sus valores más significativos, escalando cada gráfica a los valores de la forma de onda correspondiente. De igual forma, indicar el estado de los diodos en los distintos intervalos de tiempo.

A) Datos:  $R_1 = 10k\Omega$ ,  $R_2 = 10k\Omega$ ,  $U_Z = 4V$ ,  $u_E = 10sen(\omega t)V$

· D conduce y DZ NO conduce:

$$i_E = \frac{u_E}{\eta_1 + \eta_2} \qquad u_s = \frac{u_E}{2}$$

$$i_{E} = \frac{u_{E}}{\eta_{1} + \eta_{2}} \quad u_{S} = \frac{u_{E}}{2} \quad i_{E}$$

$$D \text{ conduce } y \quad D \neq \text{ Zona Zener} \quad -$$

$$i_{E} = \frac{u_{E} - U_{2}}{\eta_{1}} \quad u_{S} = U_{2}$$

·  $U_E < OV = > D$  NO conduce y Dz conduce como diodo  $i_{Dz} = -i_E = -\frac{U_E}{R_A}$

Internalos I y III: D'anduce y DZ NO CONDUCE

Intervalo II: Diconduce y DE conduce en Zona ZENER Intervalo IV: DNO conduce y DE conduce como un diodo

#### UNIVERSIDAD POLITÉCNICA DE MADRID • Escuela Técnica Superior De Ingenieros Industriales Departamento De Automática, Ingeniería Electrónica E Informática Industrial DIVISIÓN DE INGENIERÍA ELECTRÓNICA (DIE)

R

Nombre: \_\_\_\_\_ Nº Mat.: \_\_\_\_\_

- B) Datos:  $R_1 = 10k\Omega$ ,  $R_2 = 10k\Omega$ ,  $R_3 = 100\Omega$ ,  $U_Z = 4V$ ,  $\beta = 99$ ;  $u_E = 10sen(\omega t)V$ ;  $U_{CC} = 20V$

- · Us = (1+B) iB. Rg

• D conduce y Dt NO and.ie

UE = iE R1 + (1+13)iER3 UE

US = (1+13)iER3 -

· D conduce y DZ ZONA ZENER: i= =  $\frac{UE - U_2}{R_1}$ ;  $\dot{U}_B = \frac{U_2}{(1+B)R_3}$ ;  $u_5 = U_2$ ;  $\dot{u}_{D2} = -\dot{l}_E + \dot{l}_B$

Como (1+13). R3 = 10 KR = Rz, las seculas iE, ioz y Us sesultan exactamente ignales a las del circuito del agrastado A)

Nombre:

Nº Mat.:

Fundamentos de Electrónica (ANALÓGICA) Titulación: Grado de Ingeniería en Tecnologías Industriales

Publicación de preactas: 15/7/2015

Fecha: 1/7/2015

Convocatoria: Julio 2014/15

Revisión:. 17/5/2015 a las 10:00h.

PROBLEMA 1. (2 puntos)

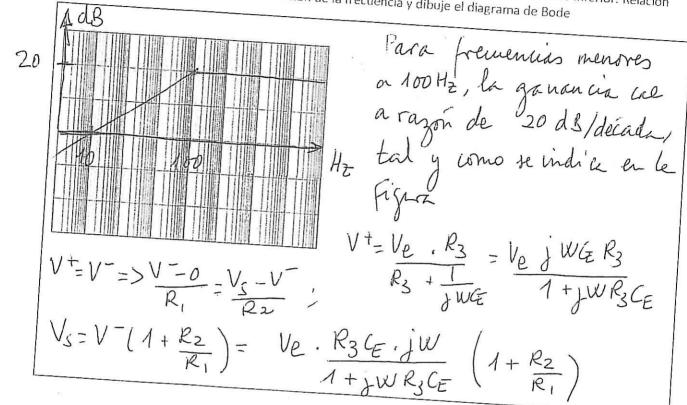

A partir del circuito de la figura, y considerando que el amplificador operacional es ideal, se pide:

Datos:

$R_1$ = 1k $\Omega$ ;  $R_2$ = 10k $\Omega$ ;  $R_3$ =1k $\Omega$ ;  $U_{CC}$  = 15v

a) Obtener la expresión de la ganancia de tensión a frecuencias medias.

Es un amplificador no inversor, realimentado regativamente. Por lo tauto, a fremencias medias  $V^+=V^-=Ve$ , ya que el condensador se comporta como un cortocismito. Por otro lado:  $V^+=V^-=Ve$ ;  $V^-=Vs$ .  $R_1+R_2=>Vs=Ve$   $(1+R_2)$

b) Obtener la expresión de la ganancia de tensión a frecuencias altas.

Es igual que en el apartado anterior.

c) Calcular  $C_{\rm f}$  para que la frecuencia de corte inferior del amplificador realimentado sea de 100Hz.

como el A.O. es ideal, solo hay que considerar R3, ya que la impedancia de entrada es infinita. fci =  $\frac{1}{2 \text{ TTR}_3 C_E}$  = 100 Hz => CE = 116 Mf.

Nombre:

Nº Mat.:

a) Explique qué ocurre para señales de entrada de frecuencia menor a la frecuencia de corte inferior. Relación entre tensión de salida y entrada en función de la frecuencia y dibuje el diagrama de Bode