#### TEMA 1. Sistemas Combinacionales.

#### **OBJETIVOS**

- 1. Introducción a los sistemas digitales. Familias lógicas (3-22)

- 2. Definición de circuito combinacional (23-27)

- 3. Funciones combinacionales. Simplificación e implementación (28-86)

- 3.1 Variables, funciones y representación de redes lógicas (29-32)

- 3.2 Axiomas y teoremas del álgebra de Boole, Dualidad (33-36)

- 3.3 Expresión de funciones como suma de productos y producto de sumas. Términos canónicos. Tablas de verdad. (37-44)

- 3.4 Simplificación de funciones. Mapas de Karnaugh (45-46)

- 3.5 Implementación (47-85)

- 4. Estructuras combinacionales básicas (86-129)

- 4.1 Puertas lógicas básicas (86)

- 4.2 Multiplexores y demultiplexores (87-112)

- 4.3 Codificadores y decodificadores (113-122)

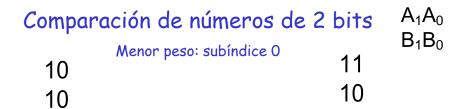

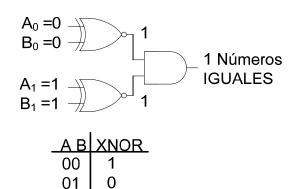

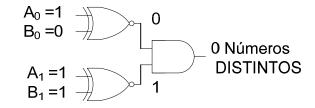

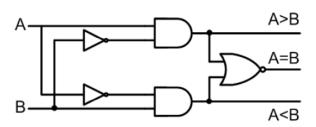

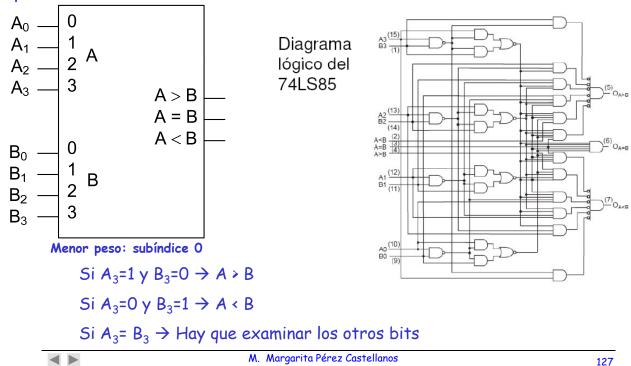

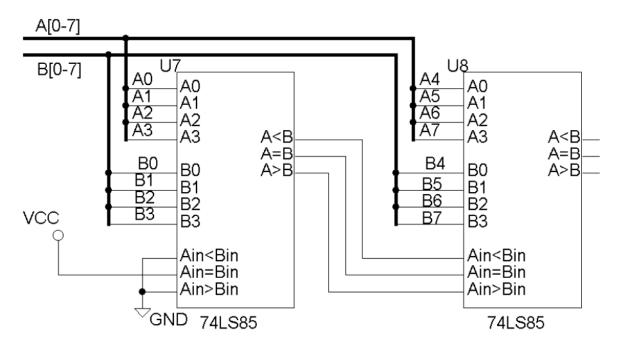

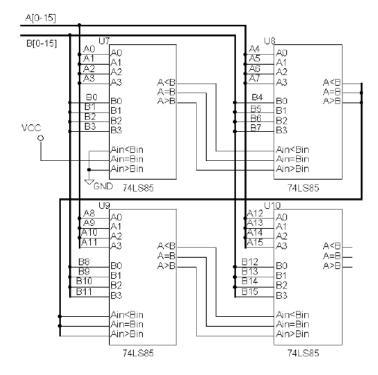

- 4.4 Compradores (123-129) Comparadores

M. Margarita Pérez Castellanos

1

#### **OBJETIVOS**

El objetivo principal de este capitulo es presentar los sistemas lógicos combinacionales y compararlos con los sistemas lógicos secuenciales, objeto estos últimos, de capítulos posteriores.

Establecer los aspectos básicos sobre el diseño de los sistemas combinacionales y su construcción utilizando puertas lógicas básicas.

Introducir estructuras combinacionales más complejas y su utilización en la construcción de sistemas

Por último descender en los niveles de diseño hasta aquel en que se utilizan de Circuitos Integrados, en nuestro caso, de baja y media escalas de integración; así como presentar y simular modelos de sistemas combinacionales construidos mediante herramientas de diseño de alto nivel.

### 1. Introducción (I)

- 1. Distinción entre las representaciones digitales y las analógicas

- 2. Mención de las ventajas y desventajas de las tecnologías digitales comparadas con las analógicas

- 3. Introducción a los sistemas digitales básicos

M. Margarita Pérez Castellanos

3

# 1. Introducción (II) Analógico versus Digital (I)

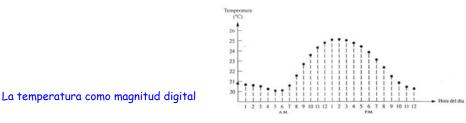

La información viene dada por los valores que toman un conjunto de magnitudes significativas. Las magnitudes pueden ser de dos tipos: analógicas y digitales.

Magnitudes analógicas: toman valores en un rango continuo. Ejemplos: temperatura, voltaje, corriente eléctrica, tiempo, etc.

La ELECTRONICA ANALOGICA es la parte de la Electrónica que trabaja con variables continuas de tal forma que un pequeño cambio en alguna variable puede producir un gran cambio en el comportamiento del circuito. Por lo tanto, las variables serán números reales.

Magnitudes digitales: su rango de posibles valores es discreto. Ejemplos: número de personas en un lugar, número de libros en una biblioteca, etc.

La ELECTRONICA DIGITAL es la parte de la Electrónica que trabaja con variables discretas. Este hecho implica que un pequeño cambio en alguna de las variables del circuito (siempre que no cambie su valor su característica de "discreto") no producirá un cambio apreciable en el comportamiento del circuito.

Es decir, el comportamiento del circuito no depende del valor exacto de la señal. Se corresponden matemáticamente con el concepto de números enteros.

#### 1. Introducción (III) Analógico versus Digital (II)

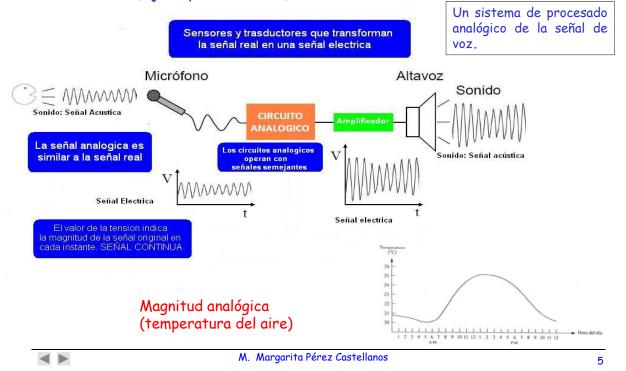

Electrónica Analógica:

Trata con señales análogas a las que hay en el mundo real, modificando sus

características (ej. amplificándolas).

#### 1. Introducción (IV) Analógico versus Digital (III)

En las señales analógicas, la información se encuentra en la forma de la onda.

Inconvenientes de los sistemas analógicos son:

La información está ligada a la forma de la onda.

Si la forma de onda se degrada, se pierde información.

2. Cada tipo de señal analógica necesita unos circuitos electrónicos particulares.

No es lo mismo un sistema electrónico para audio que para vídeo, puesto que las señales tienen características completamente diferentes.

# 1. Introducción (V) Analógico versus Digital (IV)

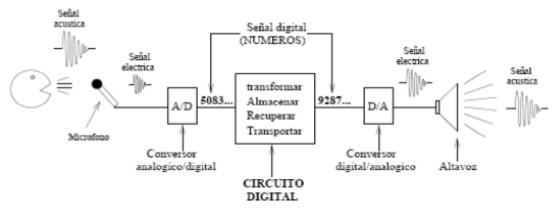

Para minimizar los inconvenientes indicados

→ conversión de las señales analógicas en digitales

y posteriormente, si se requiere, reconstrucción de la señal

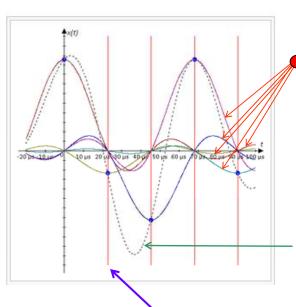

La validez de proceso de conversion analógico-digital y digital-analógico depende de la condición que impone *Nyquist*.

En 1927 el ingeniero sueco, Harry Nyquist, determinó que una señal analógica limitada en banda, para ser convertida en una representación adecuada en forma digital, debería ser muestreada, como mínimo, con una frecuencia doble que el ancho de banda de la señal.

Esta regla se conoce actualmente como el teorema de muestreo de *Nyquist-Shannon* y garantiza que cualquier señal se puede representar mediante números, y que con estos números se puede reconstruir la señal original.

M. Margarita Pérez Castellanos

7

# 1. Introducción (VI) Analógico versus Digital (V)

La reconstrucción teórica se obtiene mediante la suma ponderada de la función de interpolación g(t-nT) con  $-\infty < n < \infty$ , siendo los coeficientes de interpolación las muestras x(n)

Los 5 funciones de interpolación (5 colores), están ponderadas al valor de su correspondiente muestra (punto azul); el máximo de cada función pasa por el punto que representa su muestra

<u>Ejemplo</u> de reconstrucción de una señal de 14,7 kHz, con 5 muestras

Cada ciclo se compone de solo 3 muestras a 44100 muestras/sq.

# 1. Introducción (VII) Analógico versus Digital (VI)

Una señal digital, es una señal que está descrita por números. La electrónica digital es la que trabaja con señales digitales.

Un sistema de tratamiento de voz, con electrónica digital

M. Margarita Pérez Castellanos

9

#### 1. Introducción (VIII)

Analógico versus Digital (VII)

Analógico vs. Digital

¿Por qué del éxito de los sistemas digitales?:

- Programables

- Flexibilidad y funcionalidad

- Mayor velocidad de procesamiento

- Mayor inmunidad al ruido

- Mayor capacidad de integración

#### Revolución digital:

- Cámaras Digitales

- DVD (video)

- •CD (audio)

- Automóviles, teléfonos, tabletas, dispositivos

3D, efectos especiales...

- •MEMS, NEMS..

# 1. Introducción (IX) Señales y sistemas digitales (I)

Un sistema digital es una combinación de dispositivos (eléctricos, mecánicos, fotoeléctricos,....) ensamblados con el fin de desempeñar funciones, en las cuales, las magnitudes se representan en forma digital.

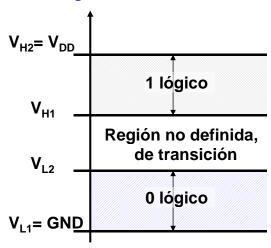

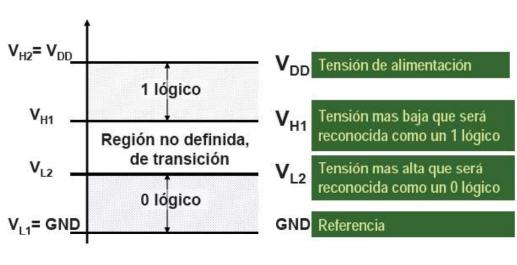

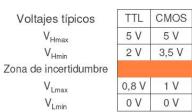

o Están diseñados para responder y producir tensiones en su entrada y salida respectivamente, que se clasifican dentro de los intervalos de tensión determinados como "0" y "1". Esto se traduce en que un circuito digital responde de la misma forma a todos los voltajes de entrada que se clasifiquen dentro del intervalo del 0 o 1 lógicos y, no diferenciará entre los voltajes de entrada que es clasifiquen dentro del 1 o 0 lógicos.

o Las características de operación en modo binario nos va a permitir utilizar como herramienta, el álgebra booleana para analizar y diseñar sistemas digitales. Los sistemas digitales son: S. Combinacionales y S. Secuenciales

$\triangleleft$

M. Margarita Pérez Castellanos

11

# 1. Introducción (X) Señales y sistemas digitales (II)

# 1. Introducción (XI) Señales y sistemas digitales (III)

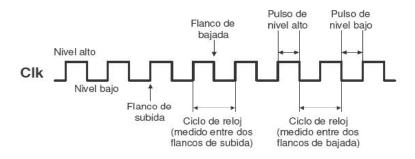

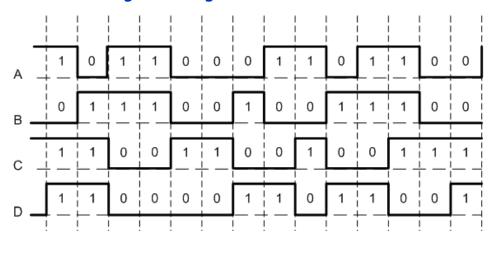

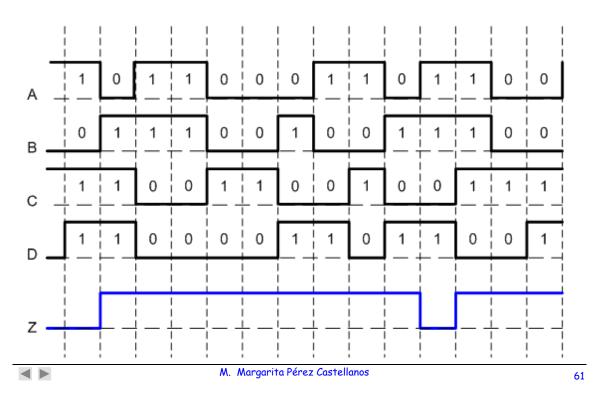

Las señales digitales son, esencialmente, **niveles de tensión** que varían entre los estados alto y bajo. Una señal digital está compuesta por una **serie de pulsos**.

Formas de onda es la representación del conjunto de pulsos (tren de pulsos) que componen una señal digital

La información binaria que manejan los sistemas digitales aparece en forma de señales que representan **secuencias de bits**. Cuando la señal está en nivel alto, se representa con un 1 binario, mientras que si la señal está a a nivel bajo se indica con un 0 binario

Diagrama de tiempos o cronograma es una gráfica que representa de forma precisa las relaciones temporales de varias señales y la variación de cada señal en función del tiempo

M. Margarita Pérez Castellanos

13

# 1. Introducción (XII) Señales y sistemas digitales (IV)

- ·La evolución de una señal a lo largo del tiempo es: la Forma de onda de la señal

- •Las formas de onda digitales se suelen representar en forma ideal, con transiciones instantáneas.

- •Pulso: transiciones  $H \rightarrow L$  (alto  $\rightarrow$  bajo) y  $L \rightarrow H$  (bajo  $\rightarrow$  alto) (o viceversa) consecutivas y de una anchura determinada.

Representación de un pulso positivo no ideal

# 1. Introducción (XIII) Señales y sistemas digitales (V)

<u>Señal de Reloj (CLK)</u>: es una señal que varía periódicamente de forma infinita.

Los sistemas digitales suelen contar con una señal de reloj (o varias) que sincroniza (n) a todas las demás.

M. Margarita Pérez Castellanos

15

# 1. Introducción (XIV) Señales y sistemas digitales (VI)

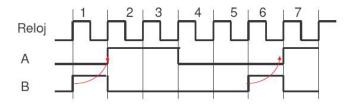

<u>Cronograma o diagrama de tiempo</u>: conjunto de formas de onda de varias señales, que normalmente están interrelacionadas

Los diagramas de tiempo suelen incluir una señal de reloj, que marca la evolución temporal de las señales

Evolución de las señales:

- •En el periodo de reloj 1 A = "0" y B = "1".

- •En el periodo 2 A = "1" y B = "0".

## 1. Introducción (XV) Señales y sistemas digitales (VII)

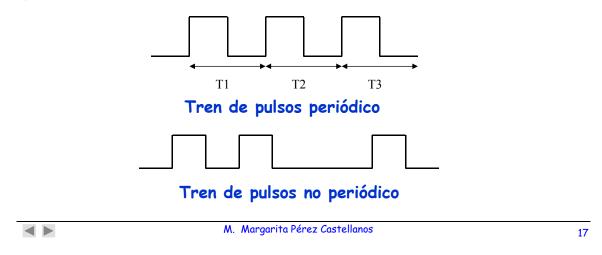

Un tren de pulsos es un conjunto de pulsos continuos en el tiempo.

Cuando los intervalos de tiempo son fijos se forma un tren periódico, que queda definido mediante el valor de su periodo (T) o el de su inversa, la frecuencia (f)

Si no tiene repetición de pulsos en forma periódica, se obtiene un tren de pulsos no periódico.

# 1. Introducción (XVI) Señales y sistemas digitales (VIII)

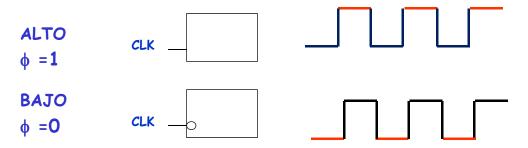

·Activación de los sistemas mediante una señal de reloj (CLK): POR NIVEL

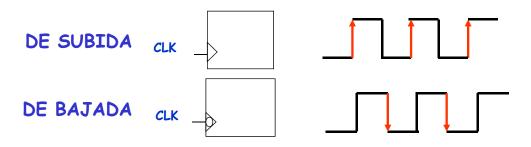

·Activación de los sistemas mediante una señal de reloj (CLK): POR FLANCO

#### 1. Introducción (XVII)

FAMILIAS LÓGICAS: Resumen (I)

#### Los circuitos digitales están agrupados en familias:

- □ Cada miembro de la familia, se fabrica con la misma tecnología, tiene una estructura similar y muestra las mismas características básicas

- □ Las características tanto eléctricas como lógicas, que son un conjunto de parámetros que discriminan a una familia.

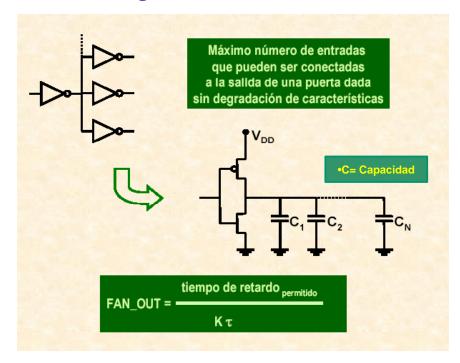

Son: tecnología de fabricación, retardos de propagación, fan-out, potencia disipada, .....

- □ 74HC (XXXX)

- □ Para elegir una familia u otra tendremos en cuenta: versatilidad lógica, velocidad, inmunidad al ruido, rango de temperaturas de operación, potencia disipada, .......

◀ ▶

M. Margarita Pérez Castellanos

19

#### 1. Introducción (XVIII)

FAMILIAS LÓGICAS: Resumen (II)

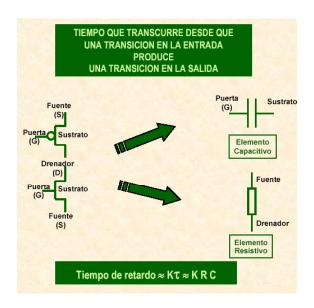

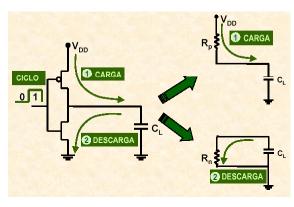

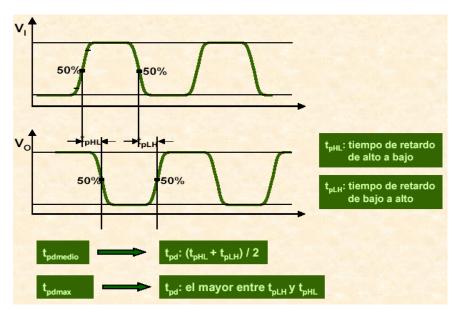

#### Retardos de propagación

#### 1. Introducción (XIX)

FAMILIAS LÓGICAS: Resumen (III)

#### Retardos de propagación

t<sub>pHL</sub> = tiempo de retardo de propagación desde la entrada (V<sub>input</sub>) hasta la salida (V<sub>output</sub>) para obtener una transición de salida de nivel alto (H) a nivel bajo (L).

t<sub>pLH</sub> = tiempo de retardo de propagación desde la entrada (V<sub>input</sub>) hasta la salida (V<sub>output</sub>) para obtener una transición de Salida de nivel bajo (L) a nivel alto (H).

t<sub>pd</sub> = retardo de propagación (propagation delay)

< ▶

M. Margarita Pérez Castellanos

21

#### 1. Introducción (XX)

FAMILIAS LÓGICAS: Resumen (IV)

#### Factor de carga (FAN-OUT)

### 2. DEFINICIÓN DE CIRCUITO COMBINACIONAL (I)

Un circuito lógico digital es puramente combinacional si la salida del mismo, en un instante dado, depende única y exclusivamente del valor que tengan sus entradas en el momento considerado.

En un circuito combinacional, salvo por el pequeño intervalo de tiempo que tarden en propagarse las señales, desde la entrada a la salida, <u>dada la entrada</u>, <u>la salida estará determinada inmediatamente</u>.

M. Margarita Pérez Castellanos

22

#### 2. CIRCUITO COMBINACIONAL (II)

# De la definición de circuito combinacional, podemos deducir:

- □ Las funciones de salida son una combinación de las variables de entrada presentes en cada momento → se puede representar mediante Funciones Lógicas de sus variables

- □ Es un sistema sin memoria

- □ Cada combinación de entrada sólo da lugar a un valor para la salida, por tanto el funcionamiento puede representarse mediante una tabla de verdad.

#### 2. CIRCUITO COMBINACIONAL (III)

<u>EJEMPLO</u>: Sea un circuito de dos entradas que nos informe en su salida si ambas entradas son iguales entre si, o no lo son.

Entradas: A, B

Salida: z

$$A = B = 0 \rightarrow Z = 1$$

$A = B = 1 \rightarrow Z = 1$

$$A = 0, B = 1 \rightarrow Z = 0$$

$A = 1, B = 0 \rightarrow Z = 0$

$$F(A,B) = Z = \overline{AB} + AB$$

$\overline{F}(A,B) = \overline{Z} = \overline{AB} + A\overline{B}$

| A | В | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$\triangleleft$

M. Margarita Pérez Castellanos

21

#### 2. CIRCUITO COMBINACIONAL (IV)

<u>Ejemplo de un circuito que NO ES combinacional</u>: Constrúyase un circuito que nos indique si el número total de 1's presentados en su entrada hasta un instante determinado, es par o impar.

El sistema se puede especificar con una tabla de verdad en la que aparezcxan las variables que intervienen en el sistema

Entrada x, salida z, "situación del sistema en un instante t" estado Q

#### 2. CIRCUITO COMBINACIONAL (V)

Tabla de verdad

|                                 | ENTRADA | SALIDA |

|---------------------------------|---------|--------|

| Situación hasta el instante "t" | X(†)    | Z(†)   |

| N° par de 1's                   | 0       | par    |

|                                 | 1       | impar  |

| N° impar de                     | 0       | impar  |

| 1's                             | 1       | par    |

#### Consecuencias

- ·Este circuito no se puede representar en una tabla de verdad solamente con las variables de entrada

- ·Para el mismo valor de la entrada tenemos dos valores de la salida

- ·Tiene que recordar la información previa el instante actual: MEMORIA

M. Margarita Pérez Castellanos

27

# 3. Funciones combinacionales. Simplificación e implementación (I)

Para construir las funciones que representan a los circuitos combinacionales, se utiliza un conjunto de herramientas que permite especificar estos circuitos lógicos digitales.

SOPORTE ALGEBRAICO: ÁLGEBRA DE BOOLE.

### 3.1 Variables, funciones y representación de redes lógicas (I)

Un poco de historia....

El matemático británico George Boole, publicó en 1854 la obra: INVESTIGACIÓN DE LAS LEYES DEL PENSAMIENTO, SOBRE LAS QUE SE BASAN LAS TEORÍAS MATEMÁTICAS DE LA LÓGICA Y LA PROBABILIDAD.

En esta publicación se generó la idea de "un álgebra de las operaciones lógicas" que se conoce en la actualidad como ÁLGEBRA DE BOOLE.

En 1938 Claude Shannon, publicó su tesis doctoral en el MIT ("A Symbolic Analysis of Relay and Switching Circuits") aplicando la obra de Boole al análisis y diseño de circuitos electrónicos.

M. Margarita Pérez Castellanos

29

## 3.1 Variables funciones y representación de redes lógicas (II)

#### TERMINOLOGÍA:

VARIABLE: es un símbolo que se utiliza para representar magnitudes lógicas (valor puede cambiar). Se designa  $a_i$ ,  $A_i$ ,  $x_i$ ...

Cualquier variable puede tener el valor 1 o 0

COMPLEMENTO: es el inverso de una variable y se indica mediante una barra encima de la misma  $\bar{a}_i$ ,  $\bar{x}_i$   $\bar{A}_i$  ...

LITERAL: se define como una variable o el complemento de una variable

CONSTANTE: es un valor fijo (0,1)

### 3.1 Variables funciones y representación de redes lógicas (III)

#### TERMINOLOGÍA:

OPERACIONES en el álgebra de Boole son reglas que permiten diferentes combinaciones de elementos. Las básicas son:

ADICIÓN: A+B, AUB

MULTIPLICACIÓN: A·B, AUB

INVERSIÓN:Ā, ¬A,-A,

EXPRESIONES BOOLEANAS (Formas Booleanas, Expresiones Lógicas) son combinaciones de variables, constantes y operadores

FUNCIONES BOOLEANAS (Funciones Lógicas) son expresiones sin constantes

M. Margarita Pérez Castellanos

2

### 3.1 Variables funciones y representación de redes lógicas (IV)

#### TERMINOLOGÍA:

FORMAS ESTÁNDAR DE LAS EXPRESIONES BOOLENAS: todas las expresiones booleanas independientemente de su forma pueden convertirse en: suma de productos o producto de sumas. Permite evaluar, simplificar e implementar expresiones booleanas de forma más sistemática.

Los términos suma o producto de una expresión si contienen todas las variables de la función afirmadas o negadas se denominan términos canónicos. Minterms, para el término producto y Maxterms para el término suma

TABLAS DE VERDAD es una forma de representar una expresión booleana utilizando todos los valores binarios de cada término de la expresión. Se forman con una columna por cada variable y otra para el valor de la función, y una fila por cada posible combinación de los valores de las variables.

#### 3.2. AXIOMAS Y TEOREMAS DEL ÁLGEBRA DE BOOLE. DUALIDAD (I)

- 1. Ley conmutativa.

- $\Box$  A+B = B+A

- $\Box$   $A \cdot B = B \cdot A$

- 2. Ley Asociativa.

- $\Box$  A+B+C= (A+B)+C= A+(B+C)

- $\Box$   $A \cdot B \cdot C = (A \cdot B) \cdot C = A \cdot (B \cdot C)$

- 3. Ley distributiva.

- $\Box$   $A \cdot (B+C) = A \cdot B + A \cdot C$

- $\Box$   $A+(B\cdot C)=(A+B)\cdot (A+C)$

M. Margarita Pérez Castellanos

2.

#### 3.2. AXIOMAS Y TEOREMAS DEL ÁLGEBRA DE BOOLE. DUALIDAD (II)

7.

$$A \cdot 1 = A$$

9.

$$A+\overline{A}=1$$

10.

$$A \cdot A = A$$

11.

$$A \overline{A} = 0$$

12.

$$A = \overline{\overline{A}}$$

13

$$A+\overline{A}\cdot B=A+B$$

15.

$$(A+B)\cdot (A+C) = A+B\cdot C$$

16.

$$A \cdot (A+B) = A \cdot B$$

17.

$$A \cdot (\overline{A} + B) = A$$

# 3.2. AXIOMAS Y TEOREMAS DEL ÁLGEBRA DE BOOLE. DUALIDAD (III)

#### Teoremas de DE MORGAN

- 1.  $\overline{A \cdot B} = \overline{A} + \overline{B}$

- 2.  $\overline{A+B} = \overline{A} \cdot \overline{B}$

#### **EJEMPLO:**

$$Z = A + B \cdot C =$$

$$= A \cdot (B \cdot C) = A \cdot (B + C) = A \cdot (B + C) = A \cdot B + A \cdot C$$

$\triangleleft$

M. Margarita Pérez Castellanos

25

# 3.2. AXIOMAS Y TEOREMAS DEL ÁLGEBRA DE BOOLE. DUALIDAD (IV)

PRINCIPIO DE DUALIDAD: dado un teorema del Álgebra de Boole, existe otro teorema llamado TEOREMA DUAL que se obtiene sustituyendo:

- "+" por "•"

- "•" por "+"

- "0" por "1"

- "1" por "0"

EJEMPLO: de A+B = B+A DUAL A • B = B • A

# 3.3. EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉRMINOS CANÓNICOS. TABLAS DE VERDAD (I)

EL ÁLGEBRA DE BOOLE proporciona una manera de expresar el funcionamiento de un circuito lógico formado por una combinación de puertas lógicas, de tal manera que la salida puede determinarse por la combinación de valores de entrada.

Cualquier circuito lógico se puede expresar mediante una EXPRESIÓN BOOLEANA.

La expresión boolena de un circuito lógico se puede desarrollar mediante una TABLA DE VERDAD. Dicho de otra forma, el funcionamiento de un circuito lógico se puede representar mediante una tabla de verdad.

**◄** ▶

M. Margarita Pérez Castellanos

37

# 3.3. EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉR-MINOS CANÓNICOS. TABLAS DE VERDAD (II)

- La tabla de verdad representa todos los valores posibles que puede tomar la salida de un circuito lógico, para todas y cada una de las combinaciones posibles de las variables de entrada de las que depende.

- Es otra forma de representar una función lógica y se puede utilizar para obtener el desarrollo en forma canónica de la misma.

La tabla tiene una columna por cada variable del circuito

La tabla tiene una fila por cada posible combinación de valores de las variables de las que depende

Sea F (a,b) =

$$a\overline{b} + \overline{a}b$$

| α | Ь | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

# 3.3. EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉRMINOS CANÓNICOS. TABLAS DE VERDAD (III)

- Cualquier expresión booleana que represente el funcionamiento de un circuito lógico, se puede convertir en una SUMA DE PRODUCTOS o en un PRODUCTO DE SUMAS.

- Si todos los términos de una suma de productos o de un producto de sumas, contienen todas las variables del sistema, estén complementadas (negadas) o no, se denominan EXPRESIONES CANÓNICAS O FORMAS NORMALES

- -PRIMERA FORMA CANÓNICA, PRIMERA FORMA NORMAL O FORMA NORMAL DISYUNTIVA: es una expresión de una función booleana compuesta por suma de minitérminos (*minterms*)

- SEGUNDA FORMA CANÓNICA, SEGUNDA FORMA NORMAL O FORMA NORMAL CONJUNTIVA: es una expresión de una función booleana compuesta por suma de maxitérminos (maxterms)

M. Margarita Pérez Castellanos

39

# 3.3 EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉRMINOS CANÓNICOS. TABLAS DE VERDAD (IV)

- Si la suma o el producto está formada por términos que contienen todas las variables, negadas o sin negar, tenemos: SUMA CANÓNICA O PRODUCTO CANÓNICO

- Cada PRODUCTO CANONICO corresponde a una fila de la tabla de verdad, en la cual la función toma el valor "1"

- Cada SUMA CANÓNICA corresponde a una fila de la tabla de verdad, en la cual la función toma el valor "0"

# 3.3 EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉRMINOS CANÓNICOS. TABLAS DE VERDAD (V)

- Las formas canónicas se pueden extraer directamente de la tabla de verdad

- La primera forma canónica (1FC): suma de minterms, asociada a las filas cuyo valor de la función es 1.

- F (a,b,c,d) =  $\sum_{4}$  m (0,1,8,9,10,11)

- La segunda forma canónica (2FC): producto de maxterms, asociada a las filas cuyo valor de la función es 0.

- $\cdot$  F (a,b,c,d) =  $\prod_4$  M (2,3,4,5,6,7,12,13,14,15)

- Las formas canónicas de una función son únicas. Las expresiones (1FC) y (2FC) son únicas.

- · Las formas 1FC y 2FC de una función son equivalentes

# 3.3 EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉRMINOS CANÓNICOS. TABLAS DE VERDAD (VI)

| а | b | С | d | Minitérmino | m,              | а | b | С | d | Maxitérmino                                                 | M <sub>i</sub>  |

|---|---|---|---|-------------|-----------------|---|---|---|---|-------------------------------------------------------------|-----------------|

| 0 | 0 | 0 | 0 | ā⋅b⋅c⋅d     | m <sub>o</sub>  | 0 | 0 | 0 | 0 | a+b+c+d                                                     | Mo              |

| 0 | 0 | 0 | 1 | ā⋅b⋅c⋅d     | m <sub>1</sub>  | 0 | 0 | 0 | 1 | $a+b+c+\overline{d}$                                        | M <sub>1</sub>  |

| 0 | 0 | 1 | 0 | ā⋅b⋅c⋅d     | m <sub>2</sub>  | 0 | 0 | 1 | 0 | $a+b+\overline{c}+d$                                        | M <sub>2</sub>  |

| 0 | 0 | 1 | 1 | ā⋅b⋅c⋅d     | m <sub>3</sub>  | 0 | 0 | 1 | 1 | a+b+c+d                                                     | M <sub>3</sub>  |

| 0 | 1 | 0 | 0 | ā⋅b⋅c̄⋅d̄   | m <sub>4</sub>  | 0 | 1 | 0 | 0 | $a+\overline{b}+c+d$                                        | M <sub>4</sub>  |

| 0 | 1 | 0 | 1 | ā⋅b⋅c̄⋅d    | m <sub>s</sub>  | 0 | 1 | 0 | 1 | $a+\overline{b}+c+\overline{d}$                             | M <sub>5</sub>  |

| 0 | 1 | 1 | 0 | ā⋅b⋅c⋅d     | m <sub>6</sub>  | 0 | 1 | 1 | 0 | $a+\overline{b}+\overline{c}+d$                             | M <sub>6</sub>  |

| 0 | 1 | 1 | 1 | ā⋅b⋅c⋅d     | m <sub>7</sub>  | 0 | 1 | 1 | 1 | $a+\overline{b}+\overline{c}+\overline{d}$                  | M <sub>7</sub>  |

| 1 | 0 | 0 | 0 | a⋅b̄⋅c̄⋅d̄  | m <sub>s</sub>  | 1 | 0 | 0 | 0 | $\overline{a}+b+c+d$                                        | M <sub>s</sub>  |

| 1 | 0 | 0 | 1 | a⋅b⋅c⋅d     | m <sub>9</sub>  | 1 | 0 | 0 | 1 | $\overline{a}+b+c+\overline{d}$                             | M <sub>9</sub>  |

| 1 | 0 | 1 | 0 | a⋅b̄⋅c⋅d̄   | m <sub>10</sub> | 1 | 0 | 1 | 0 | $\overline{a}+b+\overline{c}+d$                             | M <sub>10</sub> |

| 1 | 0 | 1 | 1 | a⋅b⋅c⋅d     | m <sub>11</sub> | 1 | 0 | 1 | 1 | $\overline{a}+b+\overline{c}+\overline{d}$                  | M <sub>11</sub> |

| 1 | 1 | 0 | 0 | a⋅b⋅c̄⋅d̄   | m <sub>12</sub> | 1 | 1 | 0 | 0 | $\overline{a} + \overline{b} + c + d$                       | M <sub>12</sub> |

| 1 | 1 | 0 | 1 | a⋅b⋅c̄⋅d    | m <sub>13</sub> | 1 | 1 | 0 | 1 | $\overline{a} + \overline{b} + c + \overline{d}$            | M <sub>13</sub> |

| 1 | 1 | 1 | 0 | a⋅b⋅c⋅d     | m <sub>14</sub> | 1 | 1 | 1 | 0 | $\overline{a} + \overline{b} + \overline{c} + d$            | M <sub>14</sub> |

| 1 | 1 | 1 | 1 | a·b·c·d     | m <sub>15</sub> | 1 | 1 | 1 | 1 | $\overline{a} + \overline{b} + \overline{c} + \overline{d}$ | M <sub>15</sub> |

# 3.3 EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉRMINOS CANÓNICOS. TABLAS DE VERDAD (VII)

$F(x_1, x_2, x_3, x_4)$

| X <sub>1</sub> | X <sub>2</sub> | <b>X</b> <sub>3</sub> | X <sub>4</sub> | F |

|----------------|----------------|-----------------------|----------------|---|

| 0              | 0              | 0                     | 0              | 1 |

| 0              | 0              | 0                     | 1              | 1 |

| 0              | 0              | 1                     | 0              | 0 |

| 0              | 0              | 1                     | 1              | 0 |

| 0              | 1              | 0                     | 0              | 0 |

| 0              | 1              | 0                     | 1              | 0 |

| 0              | 1              | 1                     | 0              | 0 |

| 0              | 1              | 1                     | 1              | 0 |

| 1              | 0              | 0                     | 0              | 1 |

| 1              | 0              | 0                     | 1              | 1 |

| 1              | 0              | 1                     | 0              | 1 |

| 1              | 0              | 1                     | 1              | 1 |

| 1              | 1              | 0                     | 0              | 0 |

| 1              | 1              | 0                     | 1              | 0 |

| 1              | 1              | 1                     | 0              | 0 |

| 1              | 1              | 1                     | 1              | 0 |

□ Suma de productos (empleando los unos)

$$F = \overline{X_1} \overline{X_2} \overline{X_3} \overline{X_4} + \overline{X_1} \overline{X_1} \overline{X_2} \overline{X_3} \overline{X_4} + \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_2} \overline{X_1} \overline{X_1} + \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} + \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} \overline{X_1} + \overline{X_1} \overline{X_1}$$

□ Producto de sumas (empleando los ceros)

$$F = (X_{1} + X_{2} + \overline{X_{3}} + X_{4})(X_{1} + X_{2} + \overline{X_{3}} + \overline{X_{4}})$$

$$(X_{1} + \overline{X_{2}} + X_{3} + X_{4})(X_{1} + \overline{X_{2}} + X_{3} + \overline{X_{4}})$$

$$(X_{1} + \overline{X_{2}} + \overline{X_{3}} + X_{4})(X_{1} + \overline{X_{2}} + \overline{X_{3}} + \overline{X_{4}})$$

$$(\overline{X_{1}} + \overline{X_{2}} + X_{3} + X_{4})(\overline{X_{1}} + \overline{X_{2}} + X_{3} + \overline{X_{4}})$$

$$(\overline{X_{1}} + \overline{X_{2}} + \overline{X_{3}} + X_{4})(\overline{X_{1}} + \overline{X_{2}} + \overline{X_{3}} + \overline{X_{4}})$$

$$(\overline{X_{1}} + \overline{X_{2}} + \overline{X_{3}} + X_{4})(\overline{X_{1}} + \overline{X_{2}} + \overline{X_{3}} + \overline{X_{4}})$$

**◄** ▶

M. Margarita Pérez Castellanos

43

# 3.3 EXPRESIONES DE FUNCIONES COMO SUMAS DE PRODUCTOS O PRODUCTOS DE SUMAS. TÉRMINOS CANÓNICOS. TABLAS DE VERDAD (VIII)

□ Suma de productos (empleando los unos)

$$F = X_1 \overline{X}_2 + \overline{X}_2 \overline{X}_3$$

$$F = \overline{X_1} \overline{X_2} \overline{X_3} \overline{X_4} + \overline{X_1} \overline{X_2} \overline{X_3} \overline{X_4}$$

□ Producto de sumas (empleando los ceros)

$$F = \overline{X}_2 (X1 + \overline{X}_3)$$

$$F = X_{1} + X_{2} + \overline{X}_{3} + X_{4}) (X_{1} + X_{2} + \overline{X}_{3} + \overline{X}_{4})$$

$$(X_{1} + \overline{X}_{2} + X_{3} + X_{4}) (X_{1} + \overline{X}_{2} + X_{3} + \overline{X}_{4})$$

$$(X_{1} + \overline{X}_{2} + \overline{X}_{3} + X_{4}) (X_{1} + \overline{X}_{2} + \overline{X}_{3} + \overline{X}_{4})$$

$$(\overline{X}_{1} + \overline{X}_{2} + X_{3} + X_{4}) (\overline{X}_{1} + \overline{X}_{2} + X_{3} + \overline{X}_{4})$$

$$(\overline{X}_{1} + \overline{X}_{2} + \overline{X}_{3} + X_{4}) (\overline{X}_{1} + \overline{X}_{2} + \overline{X}_{3} + \overline{X}_{4})$$

# 3.4 SIMPLIFICACIÓN DE FUNCIONES. MAPAS DE KARNAUG (I)

Procedimiento regular de reducción de las expresiones Lógicas mediante una tabla.

#### Sea P $(c_1c_2c_3)$

| c <sub>1</sub> | C <sub>2</sub> | <b>c</b> <sub>3</sub> | P |

|----------------|----------------|-----------------------|---|

| 0              | 0              | 0                     | 0 |

| 0              | 0              | 1                     | 0 |

| 0              | 1              | 0                     | 0 |

| 0              | 1              | 1                     | 1 |

| 1              | 0              | 0                     | 0 |

| 1              | 0              | 1                     | 1 |

| 1              | 1              | 0                     | 1 |

| 1              | 1              | 1                     | 1 |

| P <sub>1</sub> | C <sub>2</sub> C <sub>3</sub> |    |    |    |

|----------------|-------------------------------|----|----|----|

| C <sub>1</sub> | 00                            | 01 | 11 | 10 |

| 0              | 0                             | 0  | 1  | 0  |

| 1              | 0                             | 1  | 1  | 1  |

|                |                               |    |    |    |

$$P = C_1C_2 + C_1C_3 + C_2C_3$$

**◄** ▶

M. Margarita Pérez Castellanos

45

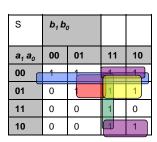

### 3.4 SIMPLIFICACIÓN DE FUNCIONES. MAPAS DE KARNAUG (II)

$S(a_1a_0b_1b_0)$

| $a_1$ | <b>a</b> <sub>0</sub> | <b>b</b> <sub>1</sub> | b <sub>0</sub> | S |

|-------|-----------------------|-----------------------|----------------|---|

| 0     | 0                     | 0                     | 0              | 1 |

| 0     | 0                     | 0                     | 1              | 1 |

| 0     | 0                     | 1                     | 0              | 1 |

| 0     | 0                     | 1                     | 1              | 1 |

| 0     | 1                     | 0                     | 0              | 0 |

| 0     | 1                     | 0                     | 1              | 1 |

| 0     | 1                     | 1                     | 0              | 1 |

| 0     | 1                     | 1                     | 1              | 1 |

| 1     | 0                     | 0                     | 0              | 0 |

| 1     | 0                     | 0                     | 1              | 0 |

| 1     | 0                     | 1                     | 0              | 1 |

| 1     | 0                     | 1                     | 1              | 1 |

| 1     | 1                     | 0                     | 0              | 0 |

| 1     | 1                     | 0                     | 1              | 0 |

| 1     | 1                     | 1                     | 0              | 0 |

| 1     | 1                     | 1                     | 1              | 1 |

S

$$(a_1a_0b_1b_0)=\overline{a_1}\overline{a_0}+\overline{a_1}b_1+\overline{a_0}b_1+\overline{a_1}b_0+b_1b_0$$

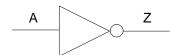

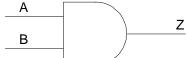

#### 3.5 IMPLEMENTACIÓN: PUERTAS LÓGICAS BÁSICAS (I)

Operación Función

Símbolo

Tabla de verdad

NOT

$$Z = \overline{A}$$

| Α | Z |

|---|---|

| 0 | 1 |

| 1 | 0 |

| Α | В | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

OR

| Α | В | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

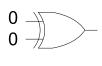

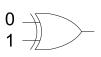

XOR

| Α | В | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

M. Margarita Pérez Castellanos

47

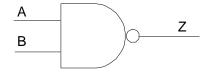

#### 3.5 IMPLEMENTACIÓN: PUERTAS LÓGICAS BÁSICAS (II)

Función Operación

Símbolo

Tabla de verdad

NAND

$$Z = \overline{A \cdot B}$$

| Α | В | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

NOR

$$Z = \overline{A+B}$$

| Α | В | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

XNOR  $Z = \overline{A \oplus B}$

| Α   | В | Z |

|-----|---|---|

| 0   | 0 | 1 |

| 0   | 1 | 0 |

| _ 1 | 0 | 0 |

| 1   | 1 | 1 |

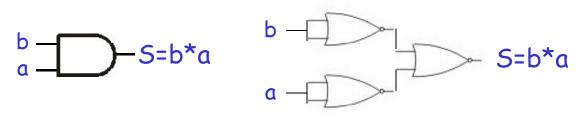

# 3.5 IMPLEMENTACIÓN DE AXIOMAS DE ÁLGEBRA DE BOOLE (III)

$$a$$

$b$

$z = a.b$

$$a \rightarrow z = \overline{b+a}$$

$$b - z = \overline{b.a}$$

Conmutativa de la suma

Conmutativa del producto

M. Margarita Pérez Castellanos

49

# 3.5 IMPLEMENTACIÓN DE AXIOMAS DE ÁLGEBRA DE BOOLE (IV)

T7 y T10

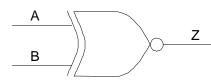

# 3.5 IMPLEMENTACIÓN DE AXIOMAS DE ÁLGEBRA DE BOOLE (V)

**T4 Y T8**

NOT:

$$S=a'=(a+a)'=(a+0)'$$

a

$$\longrightarrow$$

S=a' a  $\longrightarrow$  S=(a+a)' =a'

a  $\longrightarrow$  S=(a+0)' =a'

0

**◄** ▶

M. Margarita Pérez Castellanos

51

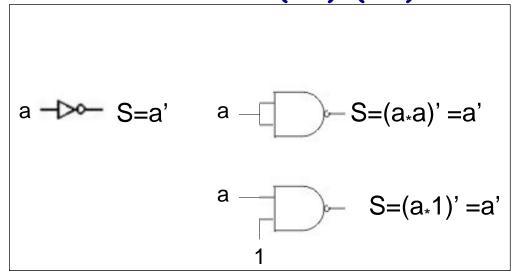

#### 3.5 IMPLEMENTACIÓN DE FUNCIONES CON PUERTAS LÓGICAS BÁSICAS (VI)

#### **ENTRADAS NO UTILIZADAS:**

- a) Dos entradas unidas

- b) NAND con entrada de valor alto

- c) NOR con entrada a valor bajo

$$Z = \overline{X}$$

#### 3.5 IMPLEMENTACIÓN DE FUNCIONES CON PUERTAS LÓGICAS BÁSICAS (VII)

IMPLEMENTACIÓN DE UNA PUERTA LÓGICA CON PUERTAS NAND

IMPLEMENTACIÓN DE UNA PUERTA LÓGICA CON PUERTAS NOR

< ▶

M. Margarita Pérez Castellanos

E 2

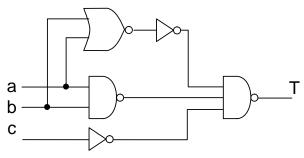

# 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (VIII)

$$T(a b c) = ab + \bar{a}\bar{b} + c$$

$F(a b c) = ((a \oplus b) \oplus c) \oplus 1) = \overline{a \oplus b \oplus c}$

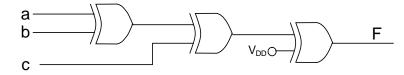

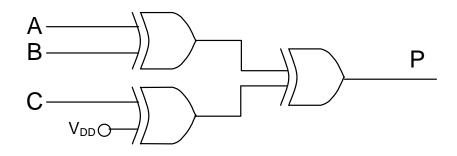

### 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (IX)

$$P(A B C) = (A \oplus B) \oplus (C \oplus 1)$$

< ▶

M. Margarita Pérez Castellanos

55

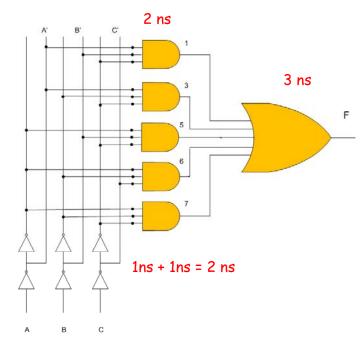

# 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (X)

Implementación con puertas AND y OR con cualquier n° de entradas, de la función: F(A,B,C) = AB'C + A'B'C + A'B'C + A'B'C + ABC'

•F(

$$A,B,C$$

) =  $\Sigma$  (1,3,5,6,7)

- •2 niveles de puertas sin contar los inversores

- ·Suponiendo que los retardos asociados a las puertas son:

Inversores 1ns

AND 2ns

OR 3ns

RETARDO TOTAL: 7 ns

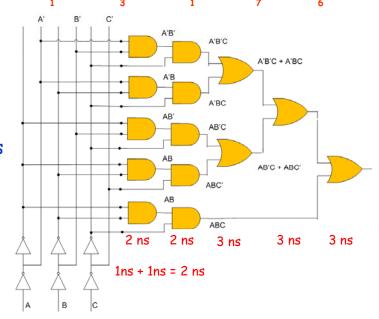

# 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (XI)

Implementación , con puertas AND y OR de 2 entradas, de la función:

F(A,B,C) = AB'C + A'B'C + A'BC + A'B'C + ABC + ABC'

- $F(A,B,C) = \Sigma (1,3,5,6,7)$

- 5 niveles de puertas sin contar los inversores

- •Suponiendo que los retardos asociados a las puertas son:

Inversores 1ns

AND 2ns

OR 3ns

RETARDO TOTAL: 15 ns

M. Margarita Pérez Castellanos

57

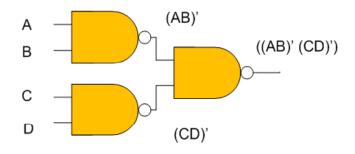

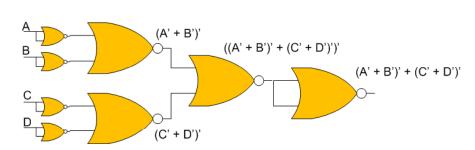

# 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (XII)

Sea la función: F(ABCD) = AB + CD

IMPLEMENTACIÓN CON PUERTAS NAND

IMPLEMENTACIÓN CON PUERTAS NOR

$$F'' = (AB + CD)''$$

$F = ((AB)' (CD)')'$

$F = ((A' + B') (C' + D'))'$

$F = (A' + B')' + (C' + D')'$

### 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (XIII)

Sea la función F(A,B,C,D) = A'B'C+A'BD+ABD'+B'CD'+AB'C'DDibújese la forma de onda de la salida cuando las entradas evolucionan según se indica en la gráfica siguiente:

**◄** ▶

M. Margarita Pérez Castellanos

59

### 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (XIV)

$$F(A,B,C,D) = A'B'C + A'BD + ABD' + B'CD' + AB'C'D$$

términos

2 3

5 7

12 14

2 10

F=A'B'CD+A'B'CD'+A'BCD+A'BC'D+ABCD'+ABC'D'+AB'CD'+A'B'CD'+AB'C'D

$F(A,B,C,D) = \Sigma (2,3,5,7,9,10,12,14)$

| A | В | C | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

# 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (XV)

F=A'B'CD+A'B'CD'+A'BCD+A'BC'D+ABCD'+ABC'D'+AB'CD'+A'B'CD'+AB'C'D

## 3.5 IMPLEMENTACIÓN DE FUNCIONES COMBINACIONALES (XVI)

EJEMPLOS para trabajo personal. Sean las funciones:

1.-

$$F(x,y,z,t) = x \cdot (y+z) \cdot t$$

$$2.-F(a,b,c)=\overline{ab+ac}$$

3.-

$$F(a,b) = a XOR b = \bar{a}b + a\bar{b}$$

Impleméntense:

- a) Con cualquier tipo de puertas con el  $n^{\rm o}$  de entradas que se desee

- b) Con puertas NAND

- C) Con puertas NOR

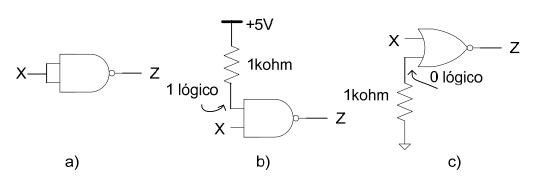

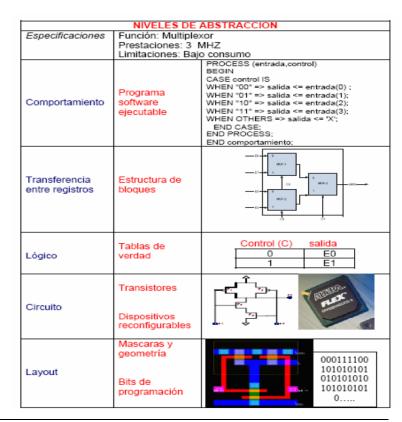

### 3.5 IMPLEMENTACIÓN CON LENGUAJES DE ALTO NIVEL LENGUALES DE DESCRIPCIÓN HARDWARE: Características (XVII)

Descripcion y simulación de circuitos combinando diferentes niveles de abstracción

**◄** ▶

M. Margarita Pérez Castellanos

63

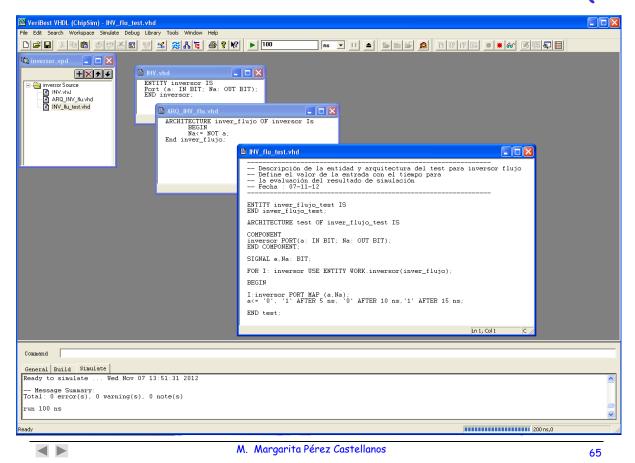

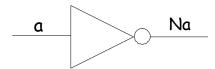

#### 3.5 IMPLEMENTACIÓN CON LENGUAJES DE ALTO NIVEL (XVIII)

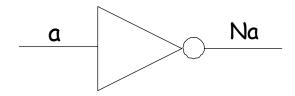

ESPECIFICACIÓN Y SIMULACIÓN: INVERSOR

El principal dominio de aplicación de los lenguajes de alto nivel es el modelado de dispositivos hardware, para la comprobación de su funcionalidad. Dado que es un lenguaje con una semántica orientada a la simulación, posteriormente al modelado, se pueden simular.

| a | Na |

|---|----|

| 0 | 1  |

| 1 | 0  |

Herramienta VeriBest VHDL.

#### 3.5 IMPLEMENTACIÓN: LENGUAJE DE ALTO NIVEL (XIX)

#### 3.5 IMPLEMENTACIÓN: LENGUAJE DE ALTO NIVEL (XX)

#### ESPECIFICACIÓN DEL INVERSOR

| a | Na |

|---|----|

| 0 | 1  |

| 1 | 0  |

**ENTITY** inversor IS

Port (a: IN BIT; Na: OUT BIT);

END inversor;

ARCHITECTURE inver\_flujo OF inversor Is BEGIN

Na<= NOT a;

END inver\_flujo;

### 3.5 IMPLEMENTACIÓN: LENGUAJE DE ALTO NIVEL (XXI)

ESPECIFICACIÓN del INVERSOR: FICHERO DE TEST

```

ENTITY inver_flujo_test IS

END inver_flujo_test;

ARCHITECTURE test OF inver_flujo_test IS

COMPONENT

inversor PORT(a: IN BIT; Na: OUT BIT);

END COMPONENT;

SIGNAL a, Na: BIT;

FOR I: inversor USE ENTITY WORK.inversor(inver_flujo);

BEGIN

I:inversor PORT MAP (a, Na);

a<= '0', '1' AFTER 5 ns, '0' AFTER 10 ns,'1' AFTER 15 ns;

END test;

M. Margarita Pérez Castellanos

67

```

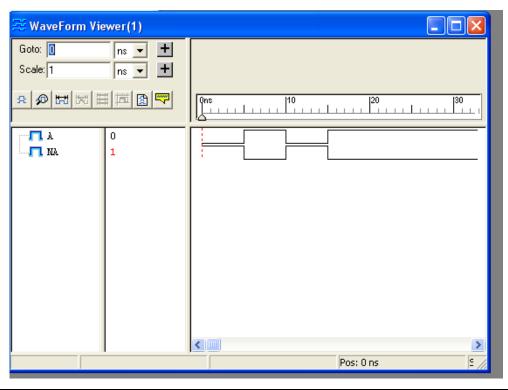

#### 3.5 IMPLEMENTACIÓN: LENGUAJE DE ALTO NIVEL (XXII

SIMULACIÓN DEL INVERSOR: CRONOGRAMA

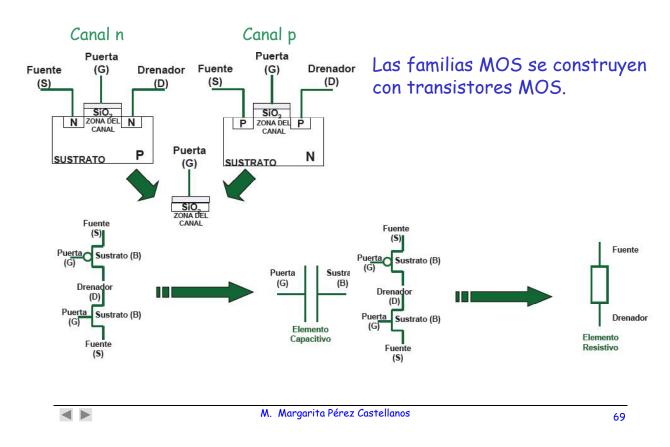

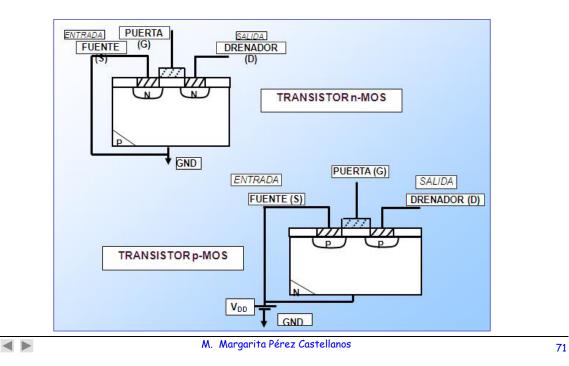

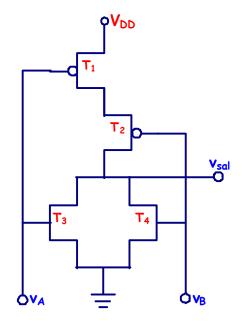

## 3.5 IMPLEMENTACIÓN MEDIANTE TECNOLOGÍAS MOS (XXIII) (REPASO de FFyTI) (I)

# 3.5 IMPLEMENTACIÓN MEDIANTE TECNOLOGÍAS MOS (XXIV) (REPASO de FFyTI) (II)

MODELO IDEAL DE TRANSISTOR: Las señales se consideran discretas

# 3.5 IMPLEMENTACIÓN MEDIANTE TECNOLOGÍAS MOS (XXV) (REPASO de FFyTI) (III)

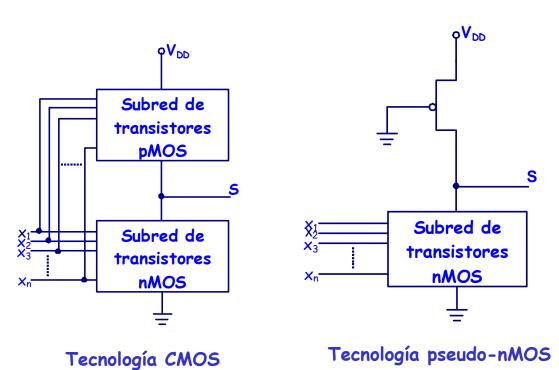

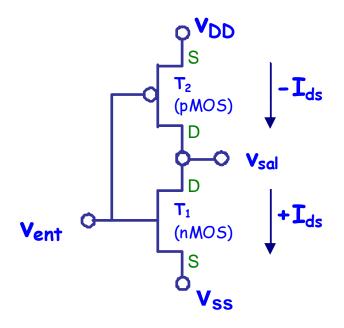

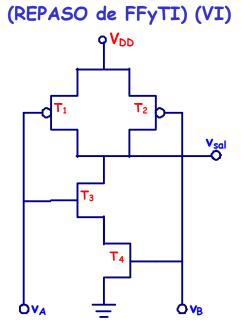

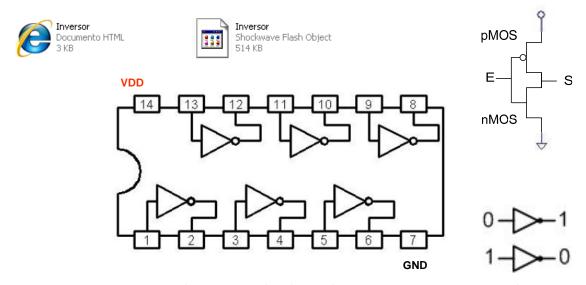

La familia CMOS, se construye con utilizando el mismo número de transistores de canal p que de canal n.

# 3.5 IMPLEMENTACIÓN MEDIANTE TECNOLOGÍAS MOS (XXVI) (REPASO de FFyTI) (IV)

# 3.5 IMPLEMENTACIÓN MEDIANTE TECNOLOGÍAS MOS (XXVII) (REPASO de FFyTI) (V)

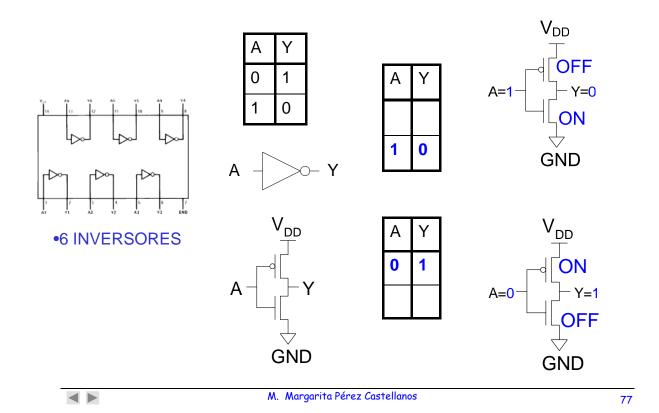

#### **INVERSOR CMOS**

M. Margarita Pérez Castellanos 73

# 3.5 IMPLEMENTACIÓN MEDIANTE TECNOLOGÍAS MOS (XXVIII)

Puerta NOR

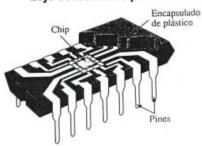

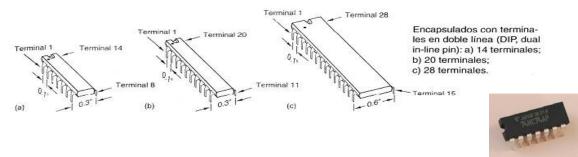

## 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXIX)

#### CIRCUITOS DIGITALES INTEGRADOS

Realizan funciones lógicas.

Características: - tamaño reducido

- alta fiabilidad

- bajo coste

- bajo consumo de potencia

#### **ENCAPSULADOS DE CI**

(b)Encapsulado SOIC

#### NUMERACIÓN DE LOS PINES

DIP o SOIC

M. Margarita Pérez Castellanos

75

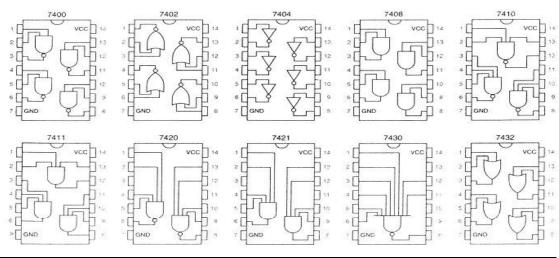

#### 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXX)

Diagramas de terminales para varios CIs SSI de la serie 7400.

#### 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXXI): EL INVERSOR 74HC04 (III)

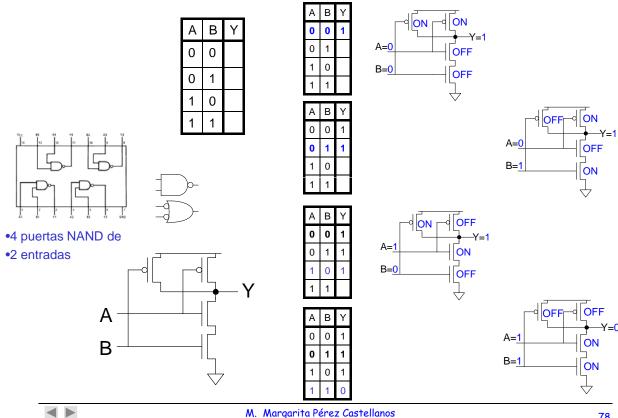

#### 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXXII): LA PUERTA NAND 74HC00 (IV)

M. Margarita Pérez Castellanos

78

#### 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXXIII): LA PUERTA NOR 74HC02 (V)

- •4 puertas NOR de

- •2 entradas

M. Margarita Pérez Castellanos

79

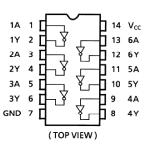

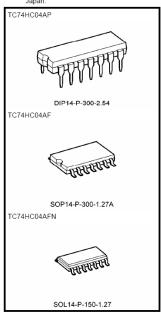

#### 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXXIV):

#### TC74HC04AP,TC74HC04AF,TC74HC04AFN

Hex Inverter

EL INVERSOR 74HC04 (VI)

The TC74HC04A is a high speed CMOS INVERTER fabricated with silicon gate C<sup>2</sup>MOS technology.

It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation.

The internal circuit is composed of 3 stages, including buffered

output, which provide high noise immunity and stable output. All inputs are equipped with protection circuits against satic discharge or transient excess voltage

#### **Features**

- High speed:  $t_{pd} = 6$  ns (typ.) at  $V_{CC} = 5$  V

- Low power dissipation: ICC = 1  $\mu$ A (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Output drive capability: 10 LSTTL loads

- Symmetrical output impedance: |IOH| = IOL = 4 mA (min)

- Balanced propagation delays:  $t_pLH \simeq t_pHL$

- Wide operating voltage range: VCC (opr) = 2 to 6 V

- Pin and function compatible with 74LS04

#### Pin Assignment

Note: xxxFN (JEDEC SOP) is not available in

Weight DIP14-P-300-2.54

0.96 g (typ.) SOP14-P-300-1.27A 0.18 g (typ.)

SOL14-P-150-1.27

: 0.12 g (typ.)

#### 3.5 IMPLE. MEDIANTE CIRCUITOS INTEGRADOS (XXXIV): EL INVERSOR 74HC04 (VII)

#### **Absolute Maximum Ratings (Note 1)**

| Characteristics                    | Symbol           | Rating                        | Unit |

|------------------------------------|------------------|-------------------------------|------|

| Supply voltage range               | Vcc              | -0.5 to 7                     | ٧    |

| DC input voltage                   | VIN              | -0.5 to V <sub>CC</sub> + 0.5 | ٧    |

| DC output voltage                  | Vout             | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Input diode current                | lik              | ±20                           | mA   |

| Output diode current               | lok              | ±20                           | mΔ   |

| DC output current                  | lout             | ±25                           | mA   |

| DC V <sub>CC</sub> /ground current | Icc              | ±50                           | mA   |

| Power dissipation                  | PD               | 500 (DIP) (Note 2)/180 (SOP)  | mW   |

| Storage temperature                | T <sub>stg</sub> | -65 to 150                    | °C   |

#### **Operating Ranges (Note)**

| Characteristics          | Symbol                          | Rating                              | Unit |

|--------------------------|---------------------------------|-------------------------------------|------|

| Supply voltage           | Vcc                             | 2 to 6                              | ٧    |

| Input voltage            | VIN                             | 0 to V <sub>CC</sub>                | V    |

| Output voltage           | Vout                            | 0 to VCC                            | V    |

| Operating temperature    | T <sub>opr</sub>                | -40 to 85                           | °C   |

|                          |                                 | 0 to 1000 (V <sub>CC</sub> = 2.0 V) |      |

| Input rise and fall time | t <sub>r</sub> , t <sub>f</sub> | 0 to 500 (V <sub>CC</sub> = 4.5 V)  | ns   |

|                          |                                 | 0 to 400 (V <sub>CC</sub> = 6.0 V)  |      |

M. Margarita Pérez Castellanos

81

# 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXXVI): EL INVERSOR 74HC04 (VIII)

#### **Electrical Characteristics**

#### **DC** Characteristics

| Characteristics              | Symbol          |                          | Test Condition            |                     |      | Га = 25°C |      |      | a =<br>o 85°C | Unit |

|------------------------------|-----------------|--------------------------|---------------------------|---------------------|------|-----------|------|------|---------------|------|

|                              | -               |                          |                           | V <sub>CC</sub> (V) | Min  | Тур.      | Max  | Min  | Max           |      |

|                              |                 |                          |                           | 2.0                 | 1.50 | _         | _    | 1.50 | _             |      |

| High-level input<br>voltage  | ViH             |                          | _                         | 4.5                 | 3.15 | _         | _    | 3.15 | _             | V    |

|                              |                 |                          |                           | 6.0                 | 4.20 | _         | _    | 4.20 | _             |      |

|                              |                 |                          |                           | 2.0                 | _    | _         | 0.50 | _    | 0.50          |      |

| Low-level input<br>voltage   | VIL             |                          | _                         | 4.5                 | _    | _         | 1.35 | _    | 1.35          | V    |

|                              |                 |                          |                           | 6.0                 | _    | _         | 1.80 | _    | 1.80          |      |

|                              |                 |                          |                           | 2.0                 | 1.9  | 2.0       | _    | 1.9  | _             |      |

|                              |                 |                          | I <sub>OH</sub> = -20 μA  | 4.5                 | 4.4  | 4.5       | _    | 4.4  | _             |      |

| High-level output<br>voltage | Voн             | VIN<br>= VIH or VIL      |                           | 6.0                 | 5.9  | 6.0       | _    | 5.9  | _             | V    |

| J J                          |                 |                          | I <sub>OH</sub> = -4 mA   | 4.5                 | 4.18 | 4.31      | _    | 4.13 | _             |      |

|                              |                 |                          | I <sub>OH</sub> = -5.2 mA | 6.0                 | 5.68 | 5.80      | _    | 5.63 | _             |      |

|                              |                 |                          |                           | 2.0                 | _    | 0.0       | 0.1  | _    | 0.1           |      |

|                              |                 |                          | I <sub>OL</sub> = 20 μA   | 4.5                 | _    | 0.0       | 0.1  | _    | 0.1           |      |

| Low-level output voltage     | VoL             | VIN<br>= VIH or VIL      |                           | 6.0                 | _    | 0.0       | 0.1  | _    | 0.1           | V    |

| , and g                      | 1112.12         | I <sub>OL</sub> = 4 mA   | 4.5                       | _                   | 0.17 | 0.26      | _    | 0.33 |               |      |

|                              |                 | I <sub>OL</sub> = 5.2 mA | 6.0                       | _                   | 0.18 | 0.26      | _    | 0.33 |               |      |

| Input leakage<br>current     | I <sub>IN</sub> | VIN = VCC O              | GND                       | 6.0                 | _    | _         | ±0.1 | _    | ±1.0          | μА   |

| Quiescent supply<br>current  | Icc             | VIN = ACC O              | GND                       | 6.0                 | _    | _         | 1.0  | _    | 10.0          | μА   |

# 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXXVII): EL INVERSOR 74HC04 (IX)

#### AC Characteristics ( $C_L = 50 \text{ pF}$ , input: $t_r = t_f = 6 \text{ ns}$ )

| Characteristics Symbol        |                           | Test Condition |         | -   | Га = 25°C |     |     | 1 =<br>o 85°C | Unit |

|-------------------------------|---------------------------|----------------|---------|-----|-----------|-----|-----|---------------|------|

|                               |                           |                | Vcc (V) | Min | Тур.      | Max | Min | Max           |      |

|                               | <b>t-</b>                 |                | 2.0     | _   | 30        | 75  | _   | 95            |      |

| Output transition time        | <sup>t</sup> TLH          | _              | 4.5     | _   | 8         | 15  | _   | 19            | ns   |

| t <sub>THL</sub>              |                           | 6.0            | _       | 7   | 13        | _   | 16  |               |      |

|                               | <b>.</b>                  |                | 2.0     | _   | 27        | 75  | _   | 95            |      |

| Propagation delay time        | <sup>t</sup> pLH          | _              | 4.5     | _   | 9         | 15  | _   | 19            | ns   |

| t <sub>pHL</sub>              |                           | 6.0            | _       | 8   | 13        | _   | 16  |               |      |

| Input capacitance             | CIN                       | _              |         | _   | 5         | 10  | _   | 10            | pF   |

| Power dissipation capacitance | C <sub>PD</sub><br>(Note) | _              |         | _   | 20        |     |     |               | pF   |

Note: C<sub>PD</sub> is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

$\triangleleft$

M. Margarita Pérez Castellanos

83

# 3.5 IMPLEMENTACIÓN MEDIANTE CIRCUITOS INTEGRADOS (XXXVIII) (X)

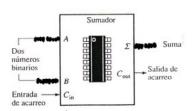

#### **FUNCIONES LÓGICAS BÁSICAS**

#### **FUNCIÓN DE COMPARACIÓN**

Ejemplo: A menor que B (2<5)

#### **FUNCIONES ARITMÉTICAS**

$\triangleleft$

# 3.5 IMPLEMENTACIÓN: ENTORNO DE CONSTRUCCIÓN Y SIMULACIÓN (XXXIX): EL INVERSOR CMOS (I)

Constructor Virtual y Simulador de Circuitos Digitales 0.9.7

M. Margarita Pérez Castellanos

# 4. ESTRUCTURAS COMBINACIONALES BÁSICAS (I)

- · Puertas lógicas básicas\*.

- Multiplexores y demultiplexores.

- · Codificadores y decodificadores.

- · Comparadores.

<sup>•</sup> ver transparencias 47 y 48

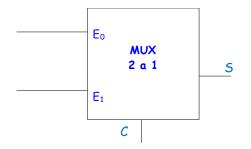

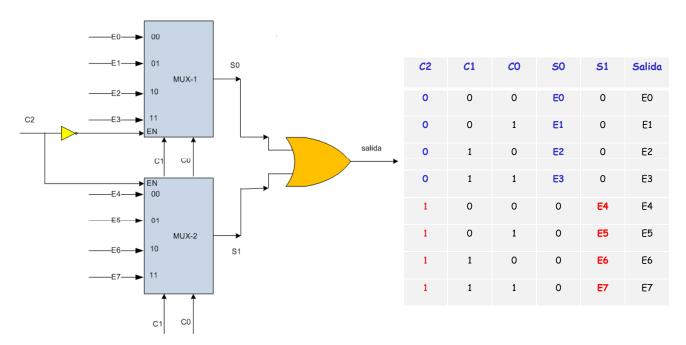

#### 4.2 MULTIPLEXORES (I)

Un multiplexor de información o selector de datos, es un circuito lógico combinacional que acepta varias entradas de datos y selecciona ("transmite") solamente una de ellas hasta su salida, dependiendo del valor de una señal de control.

Coloca en la salida la misma señal que haya en la entrada QUE SELECCIONAN las señales de control

ENTRADA DE DATOS. N° de entradas: n

ENTRADAS DE CONTROL. N° de entradas: p →2<sup>p</sup> ≥ n

2<sup>p</sup> = n (en el caso más simple)

SALIDA (O SALIDAS). N° de salidas: 1

$\triangleleft$

M. Margarita Pérez Castellanos

87

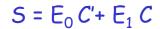

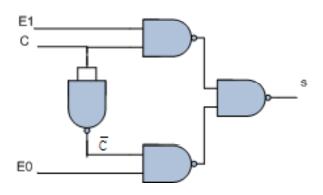

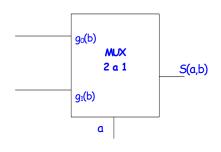

#### 4.2 MULTIPLEXORES (II)

#### EJEMPLO para 2 entradas

#### Bloque funcional

#### Tabla de verdad

| C | S              |

|---|----------------|

| 0 | Eo             |

| 1 | E <sub>1</sub> |

#### Función Lógica

$$S (MUX_2:1) = E_0 C' + E_1 C$$

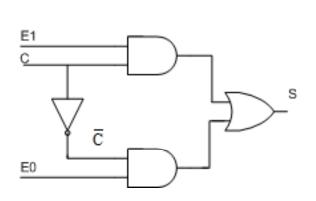

#### 4.2 MULTIPLEXORES (III)

#### EJEMPLO para 2 entradas

# Implementación con puertas lógicas

**◄** ▶

M. Margarita Pérez Castellanos

80

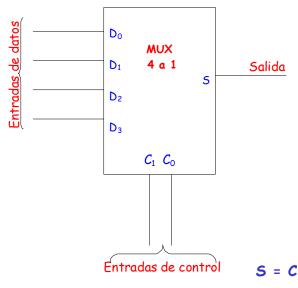

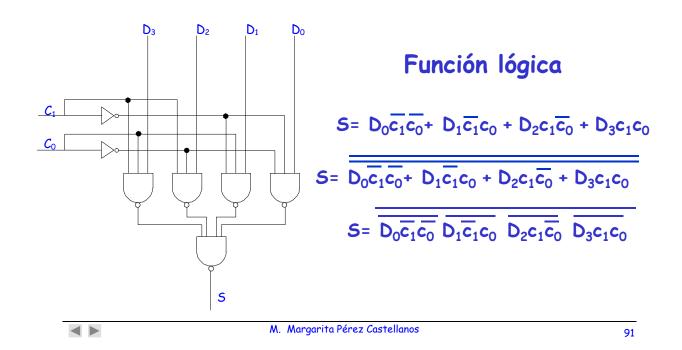

## 4.2 MULTIPLEXORES (IV)

#### EJEMPLO para 4 entradas

#### Bloque funcional

#### Tabla de verdad

| <b>C</b> <sub>1</sub> | <b>C</b> o | 5              |

|-----------------------|------------|----------------|

| 0                     | 0          | Do             |

| 0                     | 1          | D <sub>1</sub> |

| 1                     | 0          | D <sub>2</sub> |

| 1                     | 1          | D <sub>3</sub> |

## Función Lógica

$$S = C_1'C_0'(D_0) + C_1'C_0(D_1) + C_1C_0'(D_2) + C_1C_0(D_3)$$

#### 4.2 MULTIPLEXORES (V)

EJEMPLO para 4 entradas

#### Implementación con puertas lógicas (NAND)

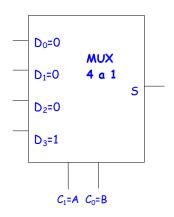

#### 4.2 MULTIPLEXORES (XI)

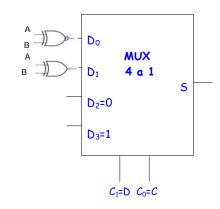

#### Aplicaciones: implementación de funciones lógicas

Implementación de la función S = A.B (puerta AND) con un MUX 4:1

$$S_{(MUX 4:1)} = D_0 (C_1' C_0') + D_1 (C_1' C_0) + D_2 (C_1 C_0') + D_3 (C_1 C_0)$$

$$S_{(MUX\ 4:1)} = A.B = (D_0 = 0)(C_1'\ C_0') + (D_1 = 0)(C_1'\ C_0) + (D_2 = 0)(C_1\ C_0') + (D_3 = 1)(C_1\ C_0) = (D_0 = 0)(A'\ B') + (D_1 = 0)(A'\ B) + (D_2 = 0)(A\ B') + (D_3 = 1)(A\ B) =$$

| $C_1(A)$ | C <sub>0</sub> (B) | 5 |

|----------|--------------------|---|

| 0        | 0                  | 0 |

| 0        | 1                  | 0 |

| 1        | 0                  | 0 |

| 1        | 1                  | 1 |

#### 4.2 MULTIPLEXORES (XII)

#### Aplicaciones: implementación de funciones lógicas

S = (B'A' + BA) D'C' + (B'A + BA')D'C + DC directamente con un MUX 4:1

Ecuación general:

$$\longrightarrow$$

S (MUX 4:1) = E<sub>0</sub> (C<sub>1</sub>' C<sub>0</sub>') + E<sub>1</sub> (C<sub>1</sub>' C<sub>0</sub>) + E<sub>2</sub> (C<sub>1</sub> C<sub>0</sub>') + E<sub>3</sub> (C<sub>1</sub> C<sub>0</sub>)

$$S_{\text{(MUX 4:1)}} = (D_0 \Rightarrow (A \varnothing B)')(D'C') + (D_1 \Rightarrow A \varnothing B)(D'C) + (D_2 \Rightarrow 0)(DC') + (D_3 \Rightarrow 1)(DC)$$

| C <sub>1</sub> (D) | C <sub>0</sub> (C) | 5      |

|--------------------|--------------------|--------|

| 0                  | 0                  | (AØB)' |

| 0                  | 1                  | (AØB)  |

| 1                  | 0                  | 0      |

| 1                  | 1                  | 1      |

$\triangleleft$

M. Margarita Pérez Castellanos

93

#### 4.2 MULTIPLEXORES (XIII)

# Aplicaciones: implementación de funciones lógicas

Implementación introduciendo en las entradas del MUX alguna de las variables de la función.

EJEMPLO: S = A.B (AND)

| $C_1(A)$ | <i>C</i> <sub>0</sub> (B) | 5 |

|----------|---------------------------|---|

| 0        | 0                         | 0 |

| 0        | 1                         | 0 |

| 1        | 0                         | 0 |

| 1        | 1                         | 1 |

$$S = 0 \text{ cuando } C_1 = 0$$

$$S = C_0 \text{ cuando } C_1 = 1$$

$$S = 0 \text{ cuando } A = 0$$

$$S = 0 \text{ cuando } A = 0$$

$$S = 0 \text{ cuando } A = 1$$

$$C_1$$

$$S_{(MUX\ 2:1)} = (E_0 = 0) C_1' + (E_1 = C_0) C_1 = (E_0 = 0) A' + (E_1 = B) A = AB$$

$\triangleleft$

#### 4.2 MULTIPLEXORES (XIV)

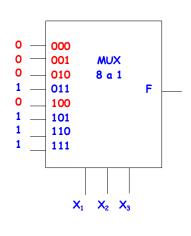

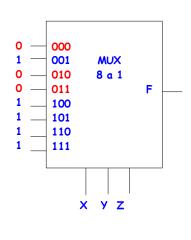

Sea la función F  $(x_1x_2x_3)$  dada por la tabla de verdad adjunta, se puede construir utilizando un multiplexor con entradas valores constantes (0, 1) y tomando como variables de control  $(x_1x_2x_3)$

| $x_1$ | X <sub>2</sub> | <b>X</b> <sub>3</sub> | F |

|-------|----------------|-----------------------|---|

| 0     | 0              | 0                     | 0 |

| 0     | 0              | 1                     | 0 |

| 0     | 1              | 0                     | 0 |

| 0     | 1              | 1                     | 1 |

| 1     | 0              | 0                     | 0 |

| 1     | 0              | 1                     | 1 |

| 1     | 1              | 0                     | 1 |

| 1     | 1              | 1                     | 1 |

**◄** ▶

M. Margarita Pérez Castellanos

95

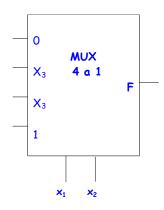

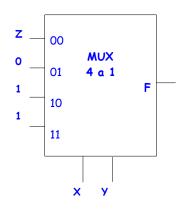

#### 4.2 MULTIPLEXORES (XV)

La misma función  $F(x_1x_2x_3)$ , se puede construir con entradas que dependan de una variable  $(x_3)$  y tomando como variables de control  $(x_1 x_2)$ :

| × <sub>1</sub> | × <sub>2</sub> | <b>x</b> <sub>3</sub> | F |

|----------------|----------------|-----------------------|---|

| 0              | 0              | 0                     | 0 |

| 0              | 0              | 1                     | 0 |

| 0              | 1              | 0                     | 0 |

| 0              | 1              | 1                     | 1 |

| 1              | 0              | 0                     | 0 |

| 1              | 0              | 1                     | 1 |

| 1              | 1              | 0                     | 1 |

| 1              | 1              | 1                     | 1 |

F = 0 cuando

$$x_1 = x_2 = 0$$

F =  $X_3$  cuando  $x_1 = 0$  y  $x_2 = 1$

F =  $X_3$  cuando  $x_1 = 1$  y  $x_2 = 0$

F= 1 cuando  $x_1 = x_2 = 1$

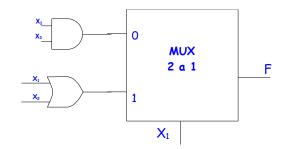

#### 4.2 MULTIPLEXORES (XVI)

La misma función  $F(x_1x_2x_3)$ , se puede construir con entradas que dependan de las 2 variables  $(x_2 \ x_3)$  y tomando como variable de control  $(x_1)$ :

| $x_1$ | X <sub>2</sub> | <b>X</b> <sub>3</sub> | F |

|-------|----------------|-----------------------|---|

| 0     | 0              | 0                     | 0 |

| 0     | 0              | 1                     | 0 |

| 0     | 1              | 0                     | 0 |

| 0     | 1              | 1                     | 1 |

| 1     | 0              | 0                     | 0 |

| 1     | 0              | 1                     | 1 |

| 1     | 1              | 0                     | 1 |

| 1     | 1              | 1                     | 1 |

F será función de  $x_2$  y de  $x_3$

$$F = x_2 x_3$$

cuando  $x_1 = 0$

$F = x_1 + x_2$  cuando  $x_1 = 1$

$\triangleleft$

M. Margarita Pérez Castellanos

07

# 4.2 MULTIPLEXORES (XVII): TEOREMA DE EXPANSIÓN DE SHANNON

o

$$F(A_1, A_2, ..., A_N) = \overline{A_1} \cdot F(0, A_2, ..., A_N) + A_1 \cdot F(1, A_2, ..., A_N)$$

o

$$F(A_1, A_2, ..., A_N) = (\overline{A_1} + F(0, A_2, ..., A_N)) \cdot (A_1 + F(1, A_2, ..., A_N))$$

Si se emplea repetidamente el teorema de expansión de *Shannon*, hasta agotar todas las variables, nos proporciona directamente el desarrollo de una función como:

SUMA DE TÉRMINOS PRODUCTO (MINTERMS) o como PRODUCTO DE TÉRMINOS SUMA (MAXTERMS).

## 4.2 MULTIPLEXORES (XVIII):

# TEOREMA DE EXPANSIÓN DE SHANNON Sabemos que:

$$F(A_1,A_2) = \overline{A_1} \cdot F(0,A_2) + A_1 \cdot F(1,A_2) =$$

$$= \overline{A_1} \cdot \overline{A_2} \cdot F(0,0) + \overline{A_1} \cdot A_2 \cdot F(0,1) + A_1 \cdot \overline{A_2} \cdot F(1,0) + A_1 \cdot A_2 \cdot F(1,1)$$

Hay que tener en cuenta que:

•

$$\overline{A}_1 \cdot F(0, A_2) = \overline{A}_1 \cdot \overline{A}_2 \cdot F(0, 0) + \overline{A}_1 \cdot A_2 \cdot F(0, 1)$$

•

$$A_1 \cdot F(1, A_2) = A_1 \cdot \overline{A_2} \cdot F(1, 0) + A_1 \cdot A_2 \cdot F(1, 1)$$

• F(0,0), F(0,1), F(1,0) y F(1,1) solamente podrán tomar los valores: '1' o '0'.

99

# 4.2 MULTIPLEXORES (XIX):

#### TEOREMA DE EXPANSIÓN DE SHANNON

#### Ejemplo:

Si para el caso anterior tenemos la siguiente tabla de verdad...

| $X_1$ | X <sub>2</sub> | <b>F</b> (X <sub>1</sub> , X <sub>2</sub> ) |

|-------|----------------|---------------------------------------------|

| 0     | 0              | 0                                           |

| 0     | 1              | 1                                           |

| 1     | 0              | 1                                           |

| 1     | 1              | 0                                           |

$$F(X_{1},X_{2}) = \overline{X}_{1} \cdot \overline{X}_{2} \cdot F(0,0) + \overline{X}_{1} \cdot X_{2} \cdot F(0,1) + X_{1} \cdot \overline{X}_{2} \cdot F(1,0) + X_{1} \cdot X_{2} \cdot F(1,1) = \overline{X}_{1} \cdot \overline{X}_{2} \cdot (0) + \overline{X}_{1} \cdot X_{2} \cdot (1) + \overline{X}_{1} \cdot \overline{X}_{2} \cdot (1) + \overline{X}_{1} \cdot \overline{X$$

#### 4.2 MULTIPLEXORES (XX)

#### o Generación de funciones lógicas

- □ Un multiplexor con N entradas de control permite generar cualquier función lógica de N+1 variables.

- □ Siguiendo el teorema de Shannon:

$$\begin{aligned} & \textbf{F}(\textbf{X}_{1}, \ \textbf{X}_{2}, \ \dots, \ \textbf{X}_{N}, \ \textbf{X}_{M}) = \overline{\textbf{X}}_{1} \ \textbf{F}(\textbf{0}, \ \textbf{X}_{2}, \ \dots, \ \textbf{X}_{M}) + \ \textbf{X}_{1} \ \textbf{F}(\textbf{1}, \ \textbf{X}_{2}, \ \dots, \ \textbf{X}_{M}) = \\ & = \overline{\textbf{X}}_{1} \overline{\textbf{X}}_{2} \ \dots \ \overline{\textbf{X}}_{N} \ \textbf{F}(\textbf{0}, \ \textbf{0}, \ \dots, \ \textbf{0}, \ \textbf{X}_{M}) + \ \textbf{X}_{1} \overline{\textbf{X}}_{2} \ \dots \ \overline{\textbf{X}}_{N} \ \textbf{F}(\textbf{1}, \ \textbf{0}, \ \dots, \ \textbf{0}, \ \textbf{X}_{M}) + \ \dots + \\ & + \ \textbf{X}_{1} \textbf{X}_{2} \ \dots \ \textbf{X}_{N} \ \textbf{F}(\textbf{1}, \ \textbf{1}, \ \dots, \ \textbf{1}, \ \textbf{X}_{M}) = \\ & = \overline{\textbf{X}}_{1} \overline{\textbf{X}}_{2} \ \dots \ \overline{\textbf{X}}_{N} \boldsymbol{G}_{0}(\textbf{X}_{M}) + \ \textbf{X}_{1} \overline{\textbf{X}}_{2} \ \dots \ \overline{\textbf{X}}_{N} \boldsymbol{G}_{1}(\textbf{X}_{M}) + \ \dots + \ \textbf{X}_{1} \textbf{X}_{2} \ \dots \ \textbf{X}_{N} \boldsymbol{G}_{2N-1}(\textbf{X}_{M}) \end{aligned}$$

□ Las funciones  $G_i(X_M)$  serán del tipo:  $\{1, 0, X_M, \overline{X_M}\}$  $F(a,b,c) = ab + \overline{b}c$

< ▶

M. Margarita Pérez Castellanos

101

# 4.2 MULTIPLEXORES (XXI):

# GENERADOR UNIVERSAL: EJEMPLO DE IMPLEMENTACIÓN PARA FUNCIONES DE DOS VARIABLES

| Función   | Puerta | Entr       | adas       |

|-----------|--------|------------|------------|

| S (a,b)   | Lógica | <b>9</b> 0 | <b>9</b> 1 |

| ab        | AND    | 0          | σ          |

| a + b     | OR     | Ь          | 1          |

| a'b'      | NOR    | b'         | 0          |

| a' + b'   | NAND   | 1          | b'         |

| ab´+ a´b  | X-OR   | Ь          | b'         |

| ab + a'b' | X-NOR  | b          | Ь          |

$$S(ab) = \bar{a} S(0 b) + a S(1 b)$$

=  $\bar{a} g_0 + a g_1$

## 4.2 MULTIPLEXORES (XXII):

Sea la función:  $F = X + \overline{Y}Z$ ,

- 1. Construimos la tabla de verdad que representa a esta función

- 2. Construimos una matriz que la implementa, tomando X, Y y Z como variables de control

| X | У | Z | F(XYZ) |

|---|---|---|--------|

| 0 | 0 | 0 | 0      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1      |

$\triangleleft$

M. Margarita Pérez Castellanos

103

# 4.2 MULTIPLEXORES (XXIII):

Sea la función:  $F = X + \overline{YZ}$

3. Desarrollamos por el teorema de Shannon en la variable Z; las entradas al multiplexor dependerán de la variable Z y se toman como variables de control X e Y

$$F(X Y Z) = \overline{X} \overline{Y} F(0 0 Z) + \overline{X} Y F(0 1 Z) + \overline{X} \overline{Y} F(1 0 Z) + \overline{X} Y F(1 1 Z) =$$

$$= \overline{X} \overline{Y} (Z) + \overline{X} Y (0) + \overline{X} \overline{Y} (1) + \overline{X} Y (1)$$

Siendo F(00Z) = z

F(01Z) = 0

F(10Z) = 1

F(11Z) = 1

#### 4.2 MULTIPLEXORES (XXIV):

#### Ejemplo:

Función F= X+  $\overline{YZ}$

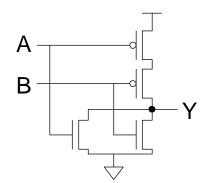

La negada de dicha función es:

$$F=\overline{X}(Y+\overline{Z})$$

- Cuando 2 puertas estén situadas en serie  $\rightarrow$  producto booleano.

- Cuando 2 puertas estén situadas en paralelo  $\rightarrow$  suma booleana.

- Casos con salida a "1" separados de casos con salida a "0".

#### Restricciones

- Un nodo no puede estar sometido simultáneamente a 2 tensiones diferentes. (no puede haber conducción por dos o más líneas simultáneamente)

- No puede haber ninguna combinación de las entradas para cual la salida no esté definida. (siempre ha de haber conducción al menos por una línea)

M. Margarita Pérez Castellanos

105

#### 4.2 MULTIPLEXORES (XXV)

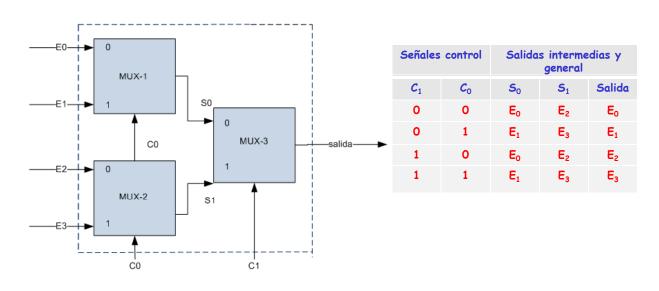

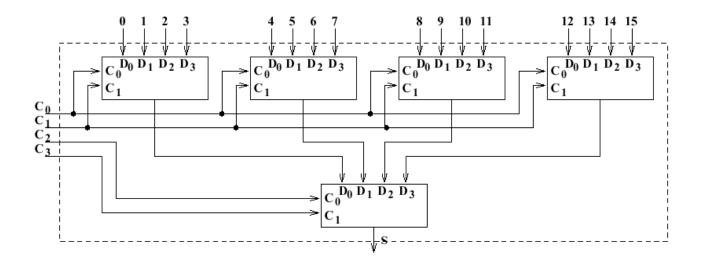

EXPANSIÓN DE MULTIPLEXORES: construcción de multiplexores de órdenes superiores, utilizando multiplexores de órdenes inferiores.

#### EJEMPLO: MUX 4:1 con multiplexores 2:1

# 4.2 MULTIPLEXORES (XXVI)

#### EJEMPLO: MUX 16:1 con multiplexores 4:1

< ▶

M. Margarita Pérez Castellanos

107

# 4.2 MULTIPLEXORES (XXVII)

#### EJEMPLO: MUX 8:1 con señal ENABLE y construido con multiplexores 4:1

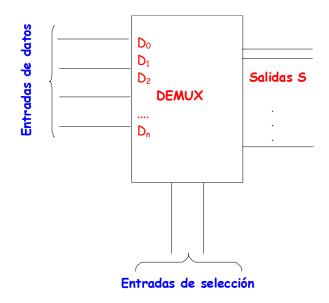

#### 4.2 DEMULTIPLEXORES (I)

Un demultiplexor realiza la operación inversa de la efectuada por un multiplexor.

Distribuye entre las salidas la señal que haya tomado de una entrada seleccionada por las señales de control

ENTRADA DE DATOS. N° de entradas: m ENTRADAS DE SELECCIÓN. N° de entradas: p  $\rightarrow 2^p \le n$ SALIDA (O SALIDAS). N° de salidas: n

Puede verse como un decodificador en el que la entrada de activación o *enable* (E) se utiliza como entrada de datos.

M. Margarita Pérez Castellanos

# 4.2 DEMULTIPLEXORES (II)

#### Bloque funcional

109

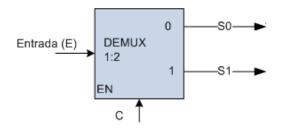

# 4.2 DEMULTIPLEXORES (III)

EJEMPLOS: DEMUX 1:2 y DEMUX 1:4

| Control | Salidas   |    |  |  |  |

|---------|-----------|----|--|--|--|

| C       | <b>51</b> | 50 |  |  |  |

| 0       | 0         | Е  |  |  |  |

| 1       | Е         | 0  |  |  |  |

|             |           | 00 | S0 <b>_</b>     |

|-------------|-----------|----|-----------------|

| Entrada (E) | DEMUX     | 01 | S1— <b>▶</b>    |

|             | 1:4<br>EN | 10 | ——\$2— <b>→</b> |

|             |           | 11 | S3 <b>►</b>     |

|             |           |    |                 |

|             | C1        | CO |                 |

| Con                   | trol       | Salidas   |           |           |            |  |

|-----------------------|------------|-----------|-----------|-----------|------------|--|

| <b>C</b> <sub>1</sub> | <b>C</b> 0 | <b>53</b> | <b>52</b> | <b>S1</b> | <b>5</b> 0 |  |

| 0                     | 0          | 0         | 0         | 0         | Е          |  |

| 0                     | 1          | 0         | 0         | Е         | 0          |  |

| 1                     | 0          | 0         | Е         | 0         | 0          |  |

| 1                     | 1          | Е         | 0         | 0         | 0          |  |

S0 = E C1' C0'

S1 = E C1'C0

52 = E C1 C0'

53 = E C1 C0

◀ ▶

M. Margarita Pérez Castellanos

111

# 4.2 DEMULTIPLEXORES (IV)

Demultiplexor 1:8, tabla de verdad

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | <b>O</b> <sub>7</sub> | <b>O</b> <sub>6</sub> | <b>O</b> <sub>5</sub> | <b>O</b> <sub>4</sub> | <b>O</b> <sub>3</sub> | <b>O</b> <sub>2</sub> | <b>O</b> <sub>1</sub> | <b>O</b> <sub>0</sub> |

|----------------|----------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0              | 0              | 0              | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |                       |

| 0              | 0              | 1              | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |                       | 0                     |

| 0              | 1              | 0              | 0                     | 0                     | 0                     | 0                     | 0                     |                       | 0                     | 0                     |

| 0              | 1              | 1              | 0                     | 0                     | 0                     | 0                     |                       | 0                     | 0                     | 0                     |

| 1              | 0              | 0              | 0                     | 0                     | 0                     |                       | 0                     | 0                     | 0                     | 0                     |

| 1              | 0              | 1              | 0                     | 0                     |                       | 0                     | 0                     | 0                     | 0                     | 0                     |

| 1              | 1              | 0              | 0                     |                       | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| 1              | 1              | 1              |                       | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |

$(0_7 \ 0_6 \ 0_5 \ 0_4 \ 0_3 \ 0_2 \ 0_1 \ 0_0) = > F \ (S_2 \ S_1 \ S_0)$

EJERCICIO DE APLICACIÓN: constrúyase con puertas AND

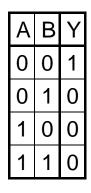

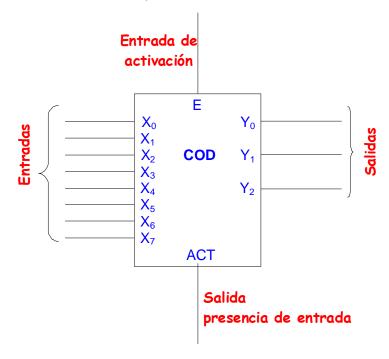

#### 4.3 CODIFICADORES Y DECODIFICADORES (I)

Un Codificador binario es un circuito lógico combinacional que para cada entrada activada, produce un código de salida (combinación lógica) de N bits

Para cada entrada activa un código de salida

ENTRADA DE DATOS. Nº de entradas: m

SALIDAS Nº de salidas: n

En el caso general:  $n y m \in \mathbb{Z} y$  se cumple  $2^n \ge m$

en el caso particular:  $m = 2^n$

$\triangleleft$

M. Margarita Pérez Castellanos

113

## 4.3 CODIFICADORES (II)

#### Bloque funcional

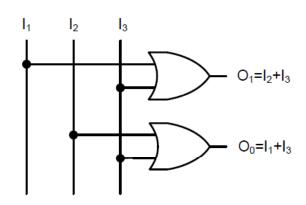

#### 4.3 CODIFICADORES (III)

Ejemplo de codificador

N° de entradas: 4

N° de salidas: 2

se cumple  $2^2 = 4$

| I <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> | O <sub>1</sub> O <sub>0</sub> |

|----------------|----------------|----------------|----------------|-------------------------------|

| 0              | 0              | 0              | I              | 0 0                           |

| 0              | 0              | I              | 0              | 0 1                           |

| 0              | 1              | 0              | 0              | 1 0                           |

| I              | 0              | 0              | 0              | 1 1                           |

**◄** ▶

M. Margarita Pérez Castellanos

115

#### 4.3 CODIFICADORES (IV)

#### Codificador de octal a binario. Tabla de verdad

| <b>A</b> <sub>7</sub> | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | <b>A</b> <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | <b>A</b> <sub>0</sub> | <b>O</b> <sub>2</sub> | <b>O</b> <sub>1</sub> | 00 |

|-----------------------|------------|------------|------------|-----------------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|----|

|                       |            |            |            |                       |                |                       |                       |                       |                       |    |

| 0                     | 0          | 0          | 0          | 0                     | 0              | 0                     | 1                     | 0                     | 0                     | 0  |

| 0                     | 0          | 0          | 0          | 0                     | 0              | 1                     | 0                     | 0                     | 0                     | 1  |

| 0                     | 0          | 0          | 0          | 0                     | 1              | 0                     | 0                     | 0                     | 1                     | 0  |

| 0                     | 0          | 0          | 0          | 1                     | 0              | 0                     | 0                     | 0                     | 1                     | 1  |

| 0                     | 0          | 0          | 1          | 0                     | 0              | 0                     | 0                     | 1                     | 0                     | 0  |

| 0                     | 0          | 1          | 0          | 0                     | 0              | 0                     | 0                     | 1                     | 0                     | 1  |

| 0                     | 1          | 0          | 0          | 0                     | 0              | 0                     | 0                     | 1                     | 1                     | 0  |

| 1                     | 0          | 0          | 0          | 0                     | 0              | 0                     | 0                     | 1                     | 1                     | 1  |

EJERCICIO DE APLICACIÓN: Impleméntese

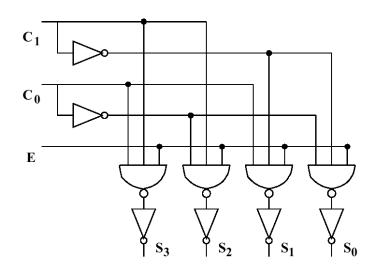

#### 4.3 DECODIFICADORES (I)

Un decodificador es un circuito lógico combinacional que para cada combinación lógica de los valores de sus entradas activa una y solamente una salida.

Para cada código de entrada se activa una salida

ENTRADA DE DATOS. Nº de entradas: n SALIDAS Nº de salidas: m

$n y m \in \mathbb{Z} y$  cumplen  $m \leq 2^n$

Las salidas de un decodificador generan todos los productos canónicos de las entradas

M. Margarita Pérez Castellanos

# 4.3 DECODIFICADORES (II)

#### Bloque funcional

# Entrada de activación (ENABLE) E DEC D<sub>1</sub> D<sub>2</sub> D<sub>3</sub> C<sub>1</sub> C<sub>0</sub>

Entradas de control

#### Tabla de verdad

| Ε | <b>C</b> <sub>1</sub> | C <sub>0</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|---|-----------------------|----------------|----------------|----------------|----------------|----------------|

| 0 | ×                     | ×              | 0              | 0              | 0              | 0              |

| 1 | 0                     | 0              | 0              | 0              | 0              | 1              |

| 1 | 0                     | 1              | 0              | 0              | 1              | 0              |

| 1 | 1                     | 0              | 0              | 1              | 0              | 0              |

| 1 | 1                     | 1              | 1              | 0              | 0              | 0              |

117

#### 4.3 DECODIFICADORES (III)

#### Estructura interna basada en puertas lógicas NAND

#### Funciones lógicas de salida

$$S_0 = E\overline{C_1}\overline{C_0}$$

$$S_1 = E\overline{C_1}C_0$$

$$S_2 = EC_1\overline{C_0}$$

$$S_3 = EC_1C_0$$

Ejemplo:

$$F(a,b,c) = ab + bc$$

$\triangleleft$

M. Margarita Pérez Castellanos

119

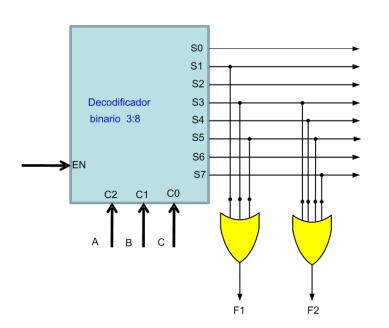

## 4.3 DECODIFICADORES (IV)

Ejemplo de utilización de decodificadores para la implementación de funciones lógicas

Sean las funciones de 3 variables

$$F1 = B'C + A'C \quad y$$

$$F2 = AB' + BC$$

$$F2 = AB' + BC$$

Transformación de las funciones a sus formas canónicas:

$$F1 = B'C + A'C =$$

$$= A'B'C+AB'C+A'B'C+A'BC=$$

$$= \Sigma (1, 3, 5)$$

$$F2 = AB' + BC =$$

$$= AB'C' + AB'C + A'BC + ABC =$$

$$= \Sigma (3, 4, 5, 7)$$

Al tener 3 variables se requiere un decoder de 3:8 (3 variables de control)

#### 4.3 DECODIFICADORES (V)

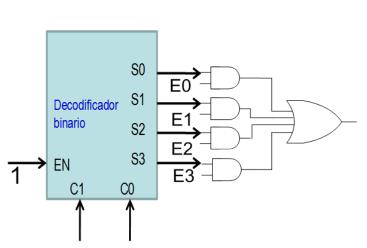

EJEMPLO: Construcción de un multiplexor 4:1, con un decodificador 2:4 y las puertas lógicas que se precisen

| EN | <b>C</b> <sub>1</sub> | C <sub>0</sub> | <b>5</b> <sub>3</sub> | <b>S</b> <sub>2</sub> | <b>S</b> <sub>1</sub> | <b>S</b> <sub>0</sub> |

|----|-----------------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0  | X                     | X              | 0                     | 0                     | 0                     | 0                     |

| 1  | 0                     | 0              | 0                     | 0                     | 0                     | 1                     |

| 1  | 0                     | 1              | 0                     | 0                     | 1                     | 0                     |

| 1  | 1                     | 0              | 0                     | 1                     | 0                     | 0                     |