| Preguntas Más Frecuentes Tema 2 |

|---------------------------------|

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

### Contenido

| CONVERTIDORES de                      | e CÓDIGO4                                                                                                                                                                                                                                                                            |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P.2.1: ¿Cómo so                       | e obtienen las expresiones del Convertidor de Código S-M a C-1 de la fig. 5.4 del texto? 4                                                                                                                                                                                           |

| en binario y desp<br>1. ¿Podemos obto | btener un nº representado en C-2 basta con complementar los números representados<br>ués sumarle 1, es decir, obtener su representación en C-1 y sumarle aritméticamente un<br>ener un convertidor de S-M a C-2 añadiéndole un sumador al convertidor de S-M a C-1<br>uemos un "1"?6 |

|                                       | explicar cómo usar en el simulador el circuito integrado SN74184, convertidor de código ra comprobar su funcionamiento?8                                                                                                                                                             |

| SUMADORES y REST                      | TADORES                                                                                                                                                                                                                                                                              |

| P.2.4: ¿Qué dife                      | erencia hay entre la suma lógica y la suma aritmética?10                                                                                                                                                                                                                             |

|                                       | e realiza la suma en el circuito de la figura 5.11 (página 276) del texto? No veo claro<br>el resultado S=11000 a partir de la suma de A=01011 y B=0110111                                                                                                                           |

| •                                     | ía describir de forma algorítmica el procedimiento usado para realizar la suma de dos<br>s en C-1?12                                                                                                                                                                                 |

| •                                     | , en el circuito sumador paralelo de 4 bits con lógica de acarreo adelantado de la figura<br>del texto, se ponen las puertas XOR para generar las salidas S0, S1, S2, S3?12                                                                                                          |

|                                       | el significado de las variables que aparecen en la cabecera de la tabla de la figura 5.14, exto?                                                                                                                                                                                     |

|                                       | ndo la expresión del rebose que aparece en la página 282 del texto: $S_1 + A_1 B_1 \overline{S}_{1?}13$                                                                                                                                                                              |

| P.2.10: ¿Qué se                       | entido tiene el diseño modular y en qué consiste?14                                                                                                                                                                                                                                  |

|                                       | s el circuito completo de la fig. 5.3.4, pag. 158, del ejercicio E.5.3 del texto de                                                                                                                                                                                                  |

| COMPARADORES                          | 17                                                                                                                                                                                                                                                                                   |

|                                       | é en el texto se usa para diseñar el comparador de palabras de 4 bits un razonamiento<br>usar la tabla de verdad?17                                                                                                                                                                  |

|                                       | n explicar de forma más detallada cómo se implementa el razonamiento seguido para esiones lógicas del comparador de 2 palabras de n bits?17                                                                                                                                          |

| comparador de d                       | ñado un comparador de dos bits (dos palabras de un bit cada una) y quiero diseñar un<br>os palabras de 2 bits usando el diseño anterior como bloque funcional básico. ¿Cómo<br>18                                                                                                    |

| puedo naceno!                         |                                                                                                                                                                                                                                                                                      |

|   |                      | Estudiando el comparador de la figura 5.17 me surge la duda acerca de las variables "E". En                                                                                      |     |

|---|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |                      | erta AND entra un bit de la palabra A, el bit correspondiente de la palabra B y una E. ¿Qué son las "Ei" y de dónde proceden?                                                    | .22 |

|   | P.2.16:              | No entiendo cómo funciona el circuito comparador de la figura 5.17                                                                                                               | .23 |

|   | P.2.17:<br>compara   | ¿Qué significan las variables de entrada que aparecen en la parte inferior del circuito<br>dor de la figura 5.17? La que están representadas como: C' (A'n > B'n) y E' (A'n=B'n) | .25 |

|   | P.2.18:<br>de expar  | ¿Cómo sería el circuito completo de un comparador de 2 palabras de 8 bits usando el circuito                                                                                     |     |

|   | P.2.19:              | ¿Qué diferencia hay entre la comparación lógica y la aritmética?                                                                                                                 | .26 |

|   | P.2.20:              | No entiendo la tabla de la figura 5.19                                                                                                                                           | .26 |

| D | ETECTOR              | DE PARIDAD                                                                                                                                                                       | .30 |

|   | P.2.21:              | ¿Qué función realiza un detector/generador de paridad?                                                                                                                           | .30 |

|   | P.2.22:              | ¿Cómo funciona el circuito detector de paridad de la figura 5.21, página 290 del texto?                                                                                          | .30 |

| U | NIDA ARI             | TMÉTICO-LÓGICA (ALU)                                                                                                                                                             | .34 |

|   | P.2.23:              | ¿Cómo podemos diseñar una Mini-ALU que realice 4 operaciones sobre palabras de 2 bits?                                                                                           | .34 |

|   | P.2.24:              | ¿Cómo puedo usar la ALU SN74181 y aprovechar todas las posibilidades que ofrece?                                                                                                 | .38 |

|   | P.2.25:              | ¿Qué significa el acarreo de salida Cn+4 en la ALU?                                                                                                                              | .39 |

|   | P.2.26:<br>F=cero d  | ¿Qué significa que la ALU se pone a 0 y qué diferencia hay entre la F=0 de la función lógica y<br>de la función aritmética de la ALU?                                            | .39 |

|   | P.2.27:<br>distintas | ¿Qué valor hay que poner en la entrada de acarreo, Cn, al programar la ALU para que realice funciones aritméticas con acarreo y sin acarreo?                                     |     |

|   | P.2.28:              | ¿Es necesario saberse la figura 5.22 (pag. 291)?                                                                                                                                 | .43 |

|   | P.2.29:<br>177 del l | ¿Son correctas las funciones de las dos primeras filas de la tabla de la figura 5.6.13 de la pag. ibro de problemas?                                                             |     |

| ^ | NEVO: HC             | NAS DE CARACTERÍSTICAS                                                                                                                                                           | 16  |

### **CONVERTIDORES de CÓDIGO**

## P.2.1: ¿Cómo se obtienen las expresiones del Convertidor de Código S-M a C-1 de la fig. 5.4 del texto?

**R.2.1:** El problema que nos planteamos es el de diseñar el convertidor de números positivos y negativos representados con palabras de tres bits en S-M a los mismos números representados en C-1 (*fig. 5.4, pag 269 del texto base*).

Para resolver el problema tenemos que calcular las expresiones lógicas de las salidas del circuito convertidor,  $y_2$ ,  $y_1$  e  $y_0$ , que representan en C-1 a los mismos números de entrada los cuales están representados en S-M mediante las variables de entrada  $x_2$ ,  $x_1$  y  $x_0$ . Es decir, tenemos que diseñar un circuito en el que, cuando en su entrada se le presente una palabra de tres bis que en S-M representa un determinado nº decimal, presente en su salida una palabra también de tres bits y que sea la correspondiente al mismo número decimal, pero ahora representado en C-1. Por ejemplo, si al circuito le entra la palabra 110 que en S-M representa al número -2 debe presentar en su salida la palabra 101 que también representa -2, pero ahora en C-1, Por tanto, el circuito debe convertir la palabra de entrada 110 en la de salida 101 y, de igual forma debe realizar la conversión para todas y cada una de las palabras de entrada.

Lo primero que tenemos que hacer es construir la tabla de verdad en la que figuren todos y cada uno de los números positivos y negativos que podemos representar con palabras de tres bits. En este caso, con 3 bits sólo tenemos 2³=8 configuraciones posibles, así que usaremos 4 para representar los números positivos y otras 4 para los números negativos, incluido el cero. Esto significa que, tanto en S-M como en C-1, con 3 bits sólo podemos representar los números decimales comprendidos entre -3 y +3. Por tanto, las tablas que aparecen en la *figura 5.4 del texto*, y que repetimos aquí unidas, presentan las equivalencias entre las tres formas de representar los correspondientes números positivos y negativos en DECIMAL, S-M y C-1.

Así, la tabla de verdad del convertidor a diseñar es:

| N° DECIMAL equivalente | Represen                                                       | NTRADA<br>tación e<br>DECIMA | n S-M del                     | Representa | ALIDAS<br>ación ei<br>DECIMA | n C-1 del |

|------------------------|----------------------------------------------------------------|------------------------------|-------------------------------|------------|------------------------------|-----------|

|                        | x <sub>2</sub> (MSB) x <sub>1</sub> x <sub>0</sub> (LSB) signo |                              | y <sub>2</sub> (MSB)<br>signo | <b>y</b> 1 | y <sub>0</sub> (LSB)         |           |

| +3                     | 0                                                              | 1                            | 1                             | 0          | 1                            | 1         |

| +2                     | 0                                                              | 1                            | 0                             | 0          | 1                            | 0         |

| +1                     | 0                                                              | 0                            | 1                             | 0          | 0                            | 1         |

| +0                     | 0                                                              | 0                            | 0                             | 0          | 0                            | 0         |

| -0                     | 1                                                              | 0                            | 0                             | 1          | 1                            | 1         |

| -1                     | 1                                                              | 0                            | 1                             | 1          | 1                            | 0         |

| -2                     | 1                                                              | 1                            | 0                             | 1          | 0                            | 1         |

| -3                     | 1                                                              | 1                            | 1                             | 1          | 0                            | 0         |

Como podemos observar, los números positivos coinciden en ambas representaciones, mientras que los números negativos en C-1 son los complementados de la representación en S-M (ver figura 5.1, 5.2 y 5.3 del texto).

Dado que tenemos que obtener las expresiones lógicas de  $y_2$ ,  $y_1$  e  $y_0$  en función de  $x_2$ ,  $x_1$  y  $x_0$ , lo que hacemos es sumar los términos mínimos correspondientes a las variables de entrada,  $x_2$ ,  $x_1$  y  $x_0$ , que hacen que cada una de las  $y_i$  tome el valor "1".

Si empezamos por el bit más significativo,  $y_2$ , observamos que coincide con el bit más significativo de la entrada,  $x_2$ . Por tanto, ya podemos poner que  $y_2 = x_2$  lo que supone que en el circuito debemos poner un hilo que una dichas variables (*ver circuito de la figura 5.4 del texto*).

A continuación vamos a calcular las expresiones de las otras dos variables. Así, si en la columna encabezada por  $y_1$  seleccionamos los unos que son los valores que hacen que se verifique  $y_1$ , y sumamos los correspondientes términos mínimos de las variables de entrada  $x_2$ ,  $x_1$  y  $x_0$  resulta:

$$y_1 = X_2 X_1 X_0 + X_2 X_1 X_0 + X_2 X_1 X_0 + X_2 X_1 X_0$$

Sacando factor común  $\bar{x}_2 x_1$  de los dos primeros términos mínimos y  $x_2 \bar{x}_1$  de los dos últimos, obtenemos:

$$y_1 = \overline{x_2} x_1 + x_2 \overline{x_1} = x_2 \oplus x_1$$

(Ver la función XOR en la pag 55).

De forma análoga se obtiene la expresión de  $y_0$ . Resultando:  $y_0 = x_2 \oplus x_0$

Resumiendo, las expresiones lógicas correspondientes a las variables de salida de un circuito que convierte un número representado con tres bits en S-M a C-1 son:

$$y_2 = x_2$$

,  $y_1 = x_2 \oplus x_1$ ,  $y_0 = x_2 \oplus x_0$

El circuito que las implementa es el que aparece en la parte inferior de la figura 5.4 del texto.

5/46

- P.2.2: Si para obtener un nº representado en C-2 basta con complementar los números representados en binario y después sumarle 1, es decir, obtener su representación en C-1 y sumarle aritméticamente un 1. ¿Podemos obtener un convertidor de S-M a C-2 añadiéndole un sumador al convertidor de S-M a C-1 con el que le sumemos un "1"?

- R.2.2: No, sobre todo si el número de bits de los números que vamos a manejar es reducido. Recordemos que la representación de los números positivos coinciden en las tres representaciones (S-M, C-1 y C-2) y que la afirmación de la cuestión sólo es válida para la representación de los números negativos. Esto implica que habría que diseñar un circuito que, además de sumarle un "1", detectara si el nº a convertir es positivo o negativo y le sumara el "1" sólo en este último caso. Por tanto, el circuito constaría de un convertidor de S-M a C-1, un sumador y un circuito encargado de detectar que el bit más significativo del número a convertir vale "1".

La solución planteada en la cuestión es válida cuando manejamos números muy grandes en los que, para su representación, hacen falta muchos bits y esto complica mucho el diseño.

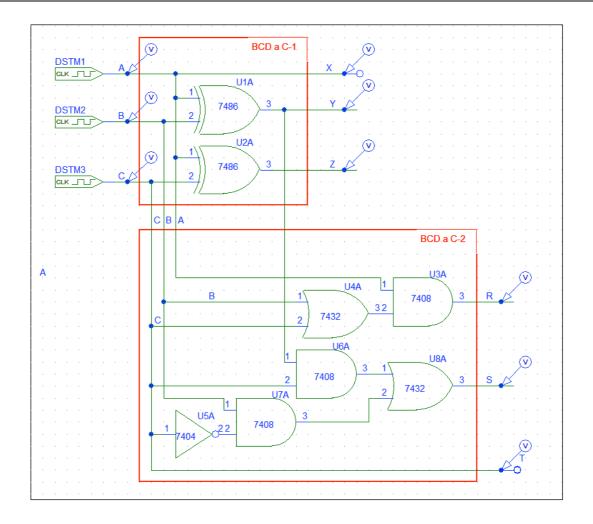

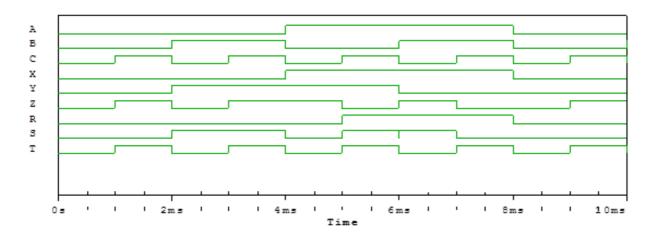

En la pregunta anterior hemos explicado paso a paso cómo diseñar un convertidor de números de 3 bits representados S-M a C-1. Veamos ahora de forma simplificada el diseño y la simulación de los convertidores de S-M a C-1 y a C-2. Así, la Tabla de verdad es:

| Decimal | S-M   |   |   | al S-M C-1 |   |   | C-2   |   |   |

|---------|-------|---|---|------------|---|---|-------|---|---|

|         | Α     | В | C | Х          | Υ | Z | R     | S | T |

|         | (MSB) |   |   | (MSB)      |   |   | (MSB) |   |   |

| +0      | 0     | 0 | 0 | 0          | 0 | 0 | 0     | 0 | 0 |

| +1      | 0     | 0 | 1 | 0          | 0 | 1 | 0     | 0 | 1 |

| +2      | 0     | 1 | 0 | 0          | 1 | 0 | 0     | 1 | 0 |

| +3      | 0     | 1 | 1 | 0          | 1 | 1 | 0     | 1 | 1 |

| -0      | 1     | 0 | 0 | 1          | 1 | 1 | 0     | 0 | 0 |

| -1      | 1     | 0 | 1 | 1          | 1 | 0 | 1     | 1 | 1 |

| -2      | 1     | 1 | 0 | 1          | 0 | 1 | 1     | 1 | 0 |

| -3      | 1     | 1 | 1 | 1          | 0 | 0 | 1     | 0 | 1 |

Obsérvese que en S-M y en C-1 existen el +0 y el -0 mientras que en C-2 no, por lo que en C-2 representamos ambos, +0 y -0, por la palabra 000.

Las expresiones de X, Y, Z (C-1) y R, S, T (C-2) en función de A, B, C (S-M) son, tras su minimización:

S-M a C-1

$$\begin{cases} X = \underline{A} \\ Y = \overline{A}B + A\overline{B} = A \oplus B \\ Z = \overline{A}C + A\overline{C} = A \oplus C \end{cases}$$

S-M a C-2

$$\begin{cases} R = A(B+C) \\ S = \overline{A}B + B \oplus C \\ T = C \end{cases}$$

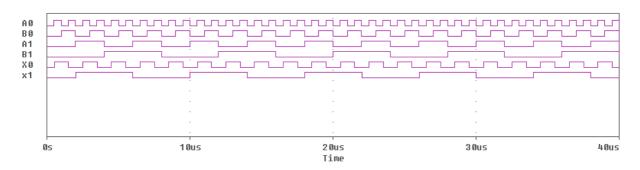

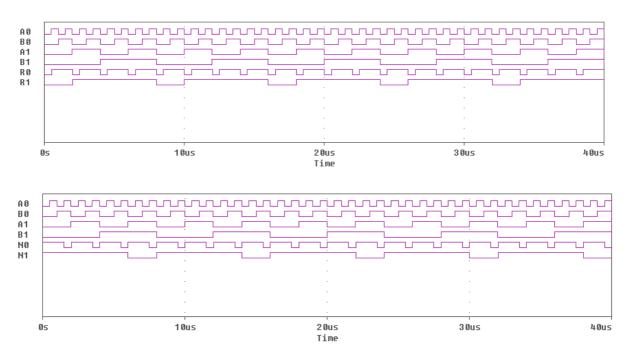

Para verificar que el diseño es correcto debemos construimos la tabla de verdad práctica a partir de este cronograma, leyendo las señales de arriba hacia abajo y viendo que ésta coincide con la tabla del inicio, punto de partida del diseño. No lo vamos a hacer, y lo dejmos como ejercicio para que lo hagáis vosotros.

$\phi \phi \phi$

- P.2.3: ¿Podría explicar cómo usar en el simulador el circuito integrado SN74184, convertidor de código BCD a Binario, para comprobar su funcionamiento?

- R.2.3: Cuando usamos un circuito integrado es importante ver previamente la información que en las hojas de características proporciona el fabricante. En estas hojas de características el fabricante da información que va desde, cómo están distribuidas las entradas, las salidas y la alimentación en el circuito integrado, hasta distintos tipo de aplicaciones, pasando por su descripción funcional, distintas formas de funcionamiento (si las tiene, como es este caso), tablas de verdad, características eléctricas, etc... Esta información es importante para que el diseñador seleccione el componente que más le interesa no sólo en términos de la función que realiza, sino de otras características que pueden ser de su interés.

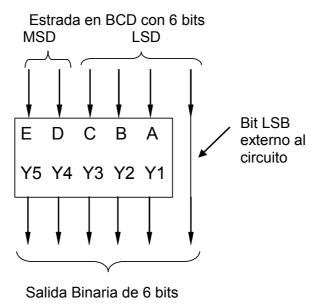

El circuito integrado SN74184 además de funcionar como un convertidor de BCD a Binario, también funciona como convertidor de BCD a Complemento a 9 y a 10, por eso tiene 8 salidas. Para la conversión de BCD a Binario sólo se usan las 5 menos significativas (y1 a y5) y las salidas y6, y7 e y8, junto con las 5 anteriores, se usan para la conversión a C-9 y C-10. Además tiene otra característica que hay que tener en cuenta y es que, como el bit menos significativo de todas las palabras en BCD coincide con el bit menos significativo de todas las palabras en binario, este bit no viene integrado en el circuito sino que es un hilo que se pone externamente y que pasa directamente de la entrada a la salida como se muestra en la figura.

Así, las palabras de salida son de 6 bits, y las de entrada también son de 6 bits, lo que nos lleva a considerar que en BCD podemos representar desde 0 (00 0000) hasta 39 (11 1001). Es decir, la tabla de verdad que es:

| Señal de |                |                   |

|----------|----------------|-------------------|

| Control  | Entrada en BCD | Salida en Binario |

| Número     |      |     | i<br>I | bit externo |                | bit externo |

|------------|------|-----|--------|-------------|----------------|-------------|

| en decimal | (nG) | E D | СВА    | LSB         | Y5 Y4 Y3 Y2 Y1 | LSB         |

| 0          | 0    | 0 0 | 000    | 0           | 0 0 0 0 0      | 0           |

| 1          | 0    | 0 0 | 000    | 1           | 0 0 0 0 0      | 1           |

| 2          | 0    | 0 0 | 0 0 1  | 0           | 0 0 0 0 1      | 0           |

| 3          | 0    | 0 0 | 0 0 1  | 1           | 0 0 0 0 1      | 1           |

|            |      |     |        |             |                |             |

| 9          | 0    | 0 0 | 100    | 1           | 0 0 1 0 0      | 1           |

| 10         | 0    | 0 1 | 000    | 0           | 0 0 1 0 1      | 0           |

| 11         | 0    | 0 1 | 000    | 1           | 0 0 1 0 1      | 1           |

|            |      |     |        |             |                |             |

| 19         | 0    | 0 1 | 1 0 0  | 1           | 0 1 0 0 1      | 1           |

| 20         | 0    | 1 0 | 000    | 0           | 0 1 0 1 0      | 0           |

| 21         | 0    | 1 0 | 000    | 1           | 0 1 0 1 0      | 1           |

|            |      |     |        |             |                |             |

| 29         |      | 1 0 | 100    | 1           | 0 1 1 1 0      | 1           |

| 30         | 0    | 1 1 | 000    | 0           | 0 1 1 1 1      | 0           |

| 31         | 0    | 1 1 | 000    | 1           | 0 1 1 1 1      | 1           |

|            |      |     |        |             |                |             |

| 38         | 0    | 1 1 | 100    | 0           | 1 0 0 1 1      | 0           |

| 39         | 0    | 1 1 | 100    | 1           | 1 0 0 1 1      | 1           |

| ninguno    | 1    | хх  | ххх    | Х           | 1 1 1 1 1      | х           |

Para interpretar los resultados debemos recordar que en BCD los 4 bits menos significativos representan las unidades y los 4 bits más representativos las decenas. En este caso, el conversor SN74184, sólo usa dos bits para las decenas y es por eso por lo que sólo se puede representar en BCD hasta el número decimal 39.

Todo lo dicho para el circuito SN74184 es válido para el SN74185.

**\* \* \***

#### **SUMADORES y RESTADORES**

#### P.2.4: ¿Qué diferencia hay entre la suma lógica y la suma aritmética?

R.2.4: La suma lógica de 2 números representados en binario es la función OR bit a bit sobre dichos números. Es decir, es la función OR entre las parejas de bits que tienen la misma significancia en cada una de las palabras que representan dichos números. Por ejemplo, dadas dos palabras, A y B, que toman los valores:

$$A = A_3 A_2 A_1 A_0 = 0010$$

$B = B_3 B_2 B_1 A_0 = 0110$

Su suma lógica es:

$$A + B = A OR B = (A_3 OR B_3), (A_2 OR B_2), (A_1 OR B_1), (A_0 OR B_0) = 0110$$

Donde hemos aplicado directamente a cada par de bit el valor correspondiente en la tabla de verdad de la función OR que aparece en la columna encabezada por  $(x_1 + x_2)$  de la fig. 1.3, del tema 1 del texto.

La *suma aritmética* es la suma que estamos acostumbrados a hacer cuando sumamos números en decimal, sólo que en vez de representar los números en base 10 (cada cifra puede tomar un valor de 0 a 9) los representamos en base 2 (cada cifra sólo puede tomar el valor 0 ó 1). Por tanto, al igual que hacemos al sumar en decimal, que cuando el resultado de sumar las unidades supera a la base menos 1, es decir, supera a 10-1=9, pasamos a las decenas (una cifra más por la izquierda) y nos llevamos uno, para sumar en base dos cuando superamos la base menos 1 (2-1=1) tenemos que usar un dígito más y también nos llevarnos "1". Así surgen las tablas de verdad del semisumador y del sumador completo en las que aparecen los acarreos, cosa que no ocurre con la función OR o suma lógica.

Resumiendo, en el caso de *suma aritmética* hacemos realmente una suma, como la hacemos cuando sumamos en decimal, y el resultado de esta suma tiene que coincidir con el de la suma de los sumandos equivales en decimal, lógicamente, teniendo en cuenta el tipo de representación que estamos usando.

Por ejemplo, si queremos hacer la suma aritmética de las mismas palabras anteriores,  $A = A_3A_2A_1A_0=0010$  y  $B = B_3B_2B_1B_0 = 0110$  deberemos ir sumando los bits desde la derecha hacia la izquierda, como hacemos cuando sumamos los números en base 10, y tener en cuenta que el acarreo que se produce cada vez que se suman dos bits hay que sumarlo a los siguiente bit hacia la izquierda. Así: si consideramos que las palabras representan números en binario puro y, por tanto, sin signo resulta:

Es importante tener en cuenta que al realizar la suma aritmética de números en las distintas representaciones (S-M, C-1, C-2, ...) el resultado de la suma en la

representación binaria usada se tiene que corresponder con el número decimal resultante de realizar la suma de los equivalentes en decimal de los sumandos correspondientes. Es decir, si los números a sumar están representados en C-1 y sus equivalentes en decimal son, por ejemplo, 011=+3 y 101=-2, al realizar la suma aritmética en C-1 debe darnos un número en C-1 cuyo valor en decimal es +1, o sea debe dar 001. Esto es válido para cualquier tipo de representación y nos sirve para comprobar que la operación es correcta.

En la ALU la **suma aritmética** se representa por la palabra **PLUS**, mientras que para la **suma lógica** se usa el signo **+** con independencia de que esté programada para realizar funciones lógicas o aritméticas.

+++

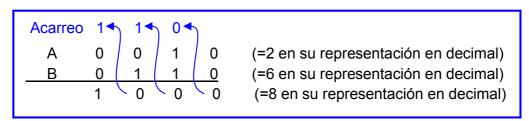

- P.2.5: ¿Cómo se realiza la suma en el circuito de la figura 5.11 (página 276) del texto? No veo claro cómo se obtiene el resultado S=11000 a partir de la suma de A=01011 y B=01101

- R.2.5: Al igual que cuando sumamos los números representados en decimal (en base 10), la suma se realiza desde la derecha hacia la izquierda y teniendo en cuenta el acarreo que se va produciendo conforme se van realizando las sumas parciales de los sucesivos dígitos (ver P2.2 de las P+F de este tema)

Así, inicialmente suponemos que  $C_n=0$  y, además, tenemos como entradas de datos a sumar en el sumador completo:  $A_0=1$ ,  $B_0=1$ . Esto genera a la salida  $S_0=0$  y  $C_{n+1}=C_1=1$ . Este valor de  $C_{n+1}$  se retarda un  $\Delta t$  (un pulso de reloj de sincronismos del circuito) y es el valor que toma  $C_n$  tras ese  $\Delta t$ , que es el tiempo que tarda la siguiente pareja de bits  $(A_1$  y  $B_1$ ) en presentarse en las entradas del sumador. Es decir, el acarreo actual que hay que sumar a cada pareja de bits coincide con el acarreo resultante de la suma de los dos bits anteriores,  $C_n(t) = C_{n+1}(t-\Delta t)$ .

El siguiente paso es la suma de  $A_1 = 1$  y  $B_1 = 0$  y el acarreo del bit anterior  $C_n = C_1 = 1$ , que da lugar a  $S_1 = A_1 + B_1 + C_1 = 1 + 0 + 1 = 0$  y  $C_{n+1} = C_2 = 1$  (que se sumará a los siguientes bits). Las siguientes entradas al sumador son  $A_2 = 0$  y  $B_2 = 1$  y el acarreo del bit anterior  $C_2 = 1$ , resultando  $S_2 = 0 + 1 + 1 = 0$  y  $C_{n+1} = C_3 = 1$  (que se sumará a los siguientes bits).

Análogamente, para  $A_3 = 1$ ,  $B_3 = 1$  y  $C_3 = 1$ , su suma es  $S_3 = 1 + 1 + 1 = 1$  y su acarreo es  $C_{n+1} = C_4 = 1$  y para  $A_4 = 0$ ,  $B_4 = 0$  y  $C_4 = 1$  su suma es  $S_4 = 0 + 0 + 1 = 1$  y  $C_{n+1} = C_5 = 0$ .

Por tanto:

$$A(01011) + B(01101) = S(11000) \text{ y } C_{n+1} = C_5 = 0$$

Una forma de comprobar que la suma es correcta es realizar la suma en decimal. Así, el número A=01011 representado en binario puro equivale al número 11 representado en decimal. Análogamente, B=01101 equivale a 13. Por tanto, A+B=11+13=24 que, representado en binario puro, es 11000. Como podemos comprobar coincide con el valor obtenido al realizar la suma en binario puro.

+++

- P.2.6: ¿Se podría describir de forma algorítmica el procedimiento usado para realizar la suma de dos palabras de n bits en C-1?

- R.2.6: Si que se puede describir mediante un algoritmo. Para ello vamos a usar la misma nomenclatura del texto. Se puede usar otra cualquiera, pero hay que definirla previamente de forma clara y precisa.

Una posible descripción algorítmica del procedimiento seguido en el texto para la suma en C-1 de palabras de n bits es:

1. Se suman bit a bit de las dos palabras A y B,  $\rightarrow$  S=A+B. Esta suma da lugar a la siguiente palabra de n+1 bits:

Siendo:

Cn = An-1+Bn-1+Cn-1. El acarreo resultante de la suma de los dos bits más significativos de las palabras A y B y del acarreo resultante de la suma del bit anterior.

Sn-1 Sn-2 ... S0 = Palabra de n bits resultante de la suma aritmética de A+B y, por tanto, teniendo en cuenta los acarreos intermedios.

- 2. Si Cn = 0

- 2.1. Si  $\overline{A_{n-1}} \overline{B_{n-1}} S_n + A_{n-1} B_{n-1} \overline{S_{n-1}} = 0 \rightarrow \text{RESULTADO: } S = Sn-1 Sn-2 \dots S0,$   $Rebose=0 \rightarrow FIN$

- 2.2. Si  $\overline{A_{n-1}} \overline{B_{n-1}} S_n + A_{n-1} B_{n-1} \overline{S_{n-1}} = 1 \rightarrow \text{RESULTADO: S= Sn-1 Sn-2} \dots S0,$ Rebose=1  $\rightarrow$  FIN

- 3. Si Cn =  $1 \rightarrow S=A+B+1$

- 3.1. Si  $\overline{A}_{n-1} \overline{B}_{n-1} S_n + A_{n-1} B_{n-1} \overline{S}_{n-1} = 0 \rightarrow \text{RESULTADO: S= Sn-1 Sn-2 ...S0,}$ Rebose=0  $\rightarrow$  FIN

- 3.2. Si  $\overline{A}_{n-1} \overline{B}_{n-1} S_n + A_{n-1} B_{n-1} \overline{S}_{n-1} = 1 \rightarrow \text{RESULTADO: S= Sn-1 Sn-2 ...S0,}$ Rebose=1  $\rightarrow$  FIN

- P.2.7: ¿Por qué, en el circuito sumador paralelo de 4 bits con lógica de acarreo adelantado de la figura 5.12, página 278 del texto, se ponen las puertas XOR para generar las salidas S0, S1, S2, S3?.

- R.2.7: El circuito es una réplica de las funciones obtenidas en el diseño (ecuaciones 5.9, 5.10 y 5.11). Así, en la expresión 5.10 del texto se obtiene la expresión general de la suma de cada bit. Es decir,

$$S_i = P_i \oplus C_i$$

siendo  $P_i = A_i \oplus B_i$

Como el sumador es de 4 bits, para obtener la suma de cada bit tenemos que particularizar y darle los valores 0, 1, 2, y 3 al subíndice "i" de las expresiones anteriores. Por tanto, obtenemos:

$$S_0 = P_0 \oplus C_0$$

$$S_1 = P_1 \oplus C1$$

$$S_2 = P_2 \oplus C_2$$

$$S_3 = P_3 \oplus C_3$$

Como en la salida de la parte recuadrada y matizada de la *figura 5.12 del texto* obtenemos las distintas  $P_i$  y  $C_i$ , tendremos que realizar la función XOR de cada una de las parejas  $P_i$  y  $C_i$  para obtener las  $S_i$  correspondientes.

- P.2.8: ¿Cuál es el significado de las variables que aparecen en la cabecera de la tabla de la figura 5.14, página 282, del texto?

- R.2.8: La nomenclatura que se sigue en esta tabla es la misma que se usa en la parte a) de la figura 5.6. Es decir, la suma de los bits menos significativos, A0 y B0, da lugar a la suma, S0, y al acarreo C1 (que se debe sumar a los siguientes bits más significativos). La suma de A1 y B1 y del acarreo C1 da lugar a S1 y al acarreo C2.

- P.2.9: No entiendo la expresión del rebose que aparece en la página 282 del texto:  $rebose = \overline{A}_1 \ \overline{B}_1 \ S_1 + A_1 \ B_1 \ \overline{S}_{12}$

- R.2.9: Recuerde que existe rebose siempre que para representar el resultado de la suma de dos números nos hace falta un bit más y no lo tenemos porque el número de bits con el que estamos trabajando es menor que el número de bits con el que tenemos que representar el resultado. Por tanto, debemos generar una señal para advertir que la solución no es la correcta.

Si tenemos sólo dos bits para representar números positivos y negativos en C-1 resulta que sólo podemos representar los siguientes números:

| C-1                    | 00 | 01 | 10 | 11 |

|------------------------|----|----|----|----|

| Equivalente en Decimal | +0 | +1 | -1 | -0 |

Si realizamos la suma de dos números positivos el resultado debe ser un número también positivo y si realizamos la suma de dos números negativos el resultado deberá ser también un número negativo.

Pues bien, veamos el rebose a través de un ejemplo. Supongamos que sumamos la palabra  $A=A_1(\text{signo})A_0=01$  (+1 en decimal) con la palabra  $B=B_1(\text{signo})B_0=01$  (+1 en decimal) el resultado es 010 (+2 en decimal). Este resultado es correcto si tuviéramos 3 bits para su representación, pero como sólo tenemos dos bits, el resultado obtenido,  $\P$ 10, queda truncado y sólo obtenemos como resultado de la suma la palabra 10. Si

\_\_\_

verificamos este resultado en la tabla vemos que no es correcto ya que 10 corresponde a -1 en decimal. Obsérvese que, además, hemos sumado dos números positivos (01+01) y hemos obtenido un número negativo (10), cosa que es imposible. Por tanto, la operación no es correcta, *hay rebose*.

En resumen, podemos decir que hay rebose cuando los bit de signo de los dos sumando son 0 (números positivos) y el bit de signo del resultado,  $S_1$ , es 1 (número negativo). Esto da lugar al sumando de la *expresión* [5.12]:  $\overline{A}_1 \ \overline{B}_1 \ S_1$

Análogamente, aplicando el mismo razonamiento nos encontramos que *también hay rebose* cuando sumamos dos números negativos y el resultado es un número positivo. Por ejemplo, si sumamos la palabra  $A=A_1(\text{signo})A_0=10$  (-1 en decimal) con la palabra  $B=B_1(\text{signo})B_0=10$  (-1 en decimal) el resultado es 100 (aquí, además existe el problema del resultado erróneo que se resuelve sumándole 1, por ser en C-1, explicado en la *página 280*). Por tanto, *también hay rebose* cuando los bits de signo de los sumandos son 1 (números negativos) y el bit de signo del resultado,  $S_1$ , es 0 (número positivo). Esto da lugar al otro sumando de la *expresión* [5.12]:  $A_1 B_1 \overline{S}_1$ .

Las sumas del resto de las posibles combinaciones de los cuatro números no presentan rebose.

Por tanto, la expresión del rebose de un sumador de 2 bits en C-1 es:

rebose =

$$\overline{A}_1 \overline{B}_1 S_1 + A_1 B_1 \overline{S}_1$$

#### P.2.10: ¿Qué sentido tiene el diseño modular y en qué consiste?

R.2.10: Como norma general, a la hora de realizar el diseño de un circuito electrónico se intenta que sea modular con el fin de que si hay necesidad de ampliar el diseño, por ejemplo, aumentando el número de bits o de palabras en el caso de que el diseño sea de un circuito digital, no haya necesidad de hacer un nuevo diseño sino que baste con unir dos o más módulos iguales.

Para ello, a la hora de realizar dicho diseño o de implementar el circuito hay que ver qué señales participan en dicho módulo, además de las señales de entrada y de control propias de la función a realizar, y cómo lo hacen con el fin de tenerlas en cuenta para que la operación resultante de la ampliación sea la correcta.

Un caso sencillo de diseño modular es el del sumador completo en el que tenemos en cuenta, a la hora de realizar su diseño, el arrastre de entrada procedente de la suma del bit anterior ( $C_i$  en la tabla de verdad del *apartado* (b) la figura 5.6 del texto). Así, una vez que hemos obtenido el circuito del sumador completo para dos bits (circuito del *apartado* (c) de la figura 5.6) podemos ampliarlo a más bits sin más que ir uniendo varios módulos en serie, tantos como bits tienen las palabras que queremos sumar, de forma que, el acarreo de salida del sumador del bit menos significativo se conecta a la entrada de acarreo del bit inmediato superior y así sucesivamente, como se muestra en la figura 5.7.

Una vez que se conectan los módulos para expandir la función a más bits es importante

que las entradas de conexión de los bloques correspondientes al *bit menos significativo* se pongan a los valores adecuados con el fin de que no afecten a la operación a realizar. Así, si nos centramos en la *figura 5.7*, todos los bloques tienen su entrada de acarreo conectada a la salida de acarreo del bloque anterior, *menos la entrada de acarreo del primer bloque*, el del bit menos significativo, que deberemos poner a "0" para que no se le sume a este bit un acarreo.

Esto que se ve bastante claro en el circuito sumador por ser el acarreo de la suma de un bit, también se hace con el resto de los circuitos en los que, a veces, no parece tan evidente y hay razonar acerca del valor adecuado (0 ó 1) para que no modifique la función a realizar por este primer bloque.

+++

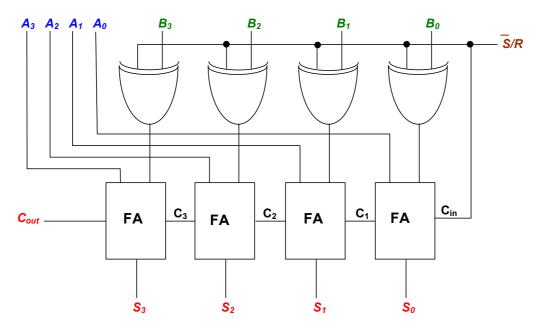

# P.2.11: ¿Cuál es el circuito completo de la fig. 5.3.4, pag. 158, del ejercicio E.5.3 del texto de problemas?.

R.2.11: El principio de funcionamiento de este circuito es que la resta la podemos reducir a una suma si cambiamos de signo al sustraendo, es decir A-B=A+ (- B ). Por tanto, para realizar la resta debemos complementar cada uno de los bits de B y sumarle 1 al bit menos significativo, para representar B en C-2 y así poder sumar directamente cada uno de los bits usando tantos sumadores completos de un bit como bits tienen las palabras sobre las que vamos a operar.

Para complementar cada uno de los bits de la palabra B usamos la función XOR entre la señal de control  $\overline{S}/R$ , que para la resta toma el valor "1", y cada uno de los bits de B, obtenida a partir de la tabla de verdad de la *figura 5.3.3*. Además, hay que sumarle "1" al bit menos significativo y esto lo hacemos a través del acarreo de entrada del sumador correspondiente al bit menos significativo, al que le introducimos también la misma señal  $\overline{S}/R$  que, como hemos visto anteriormente, toma el valor "1" para la resta.

Así el circuito completo es:

\_

Finalmente, comprobemos el funcionamiento del circuito.

- 1. Supongamos que queremos hacer una **suma**. En este caso, la señal de control será  $\overline{S}/R = 0$ , lo que supone que en las salidas de las puertas XOR se obtienen las expresiones  $0 \oplus B_i = B_i$  y que  $C_{in}=0$ . Por tanto, realiza la función A+B.

- 2. En el caso de que queramos hacer una **resta** la señal de control será  $\overline{S}/R = 1$ , lo que supone que en las salidas de las puertas XOR se obtienen las expresiones  $1 \oplus B_i = \overline{B}_i$  (si B=0,  $1 \oplus 0 = 1$  y si B=1,  $1 \oplus 1 = 0$ ) y que  $C_{in}=1$ . Por tanto, se complementan todos los bits de la palabra B y se la suma "1" a través del acarreo de entrada  $C_{in}$ . Es decir, se realiza la operación A-B mediante la suma en C-2 de A y -B.

+++

#### **COMPARADORES**

- P.2.12: ¿Por qué en el texto se usa para diseñar el comparador de palabras de 4 bits un razonamiento lógico en vez de usar la tabla de verdad?

- R.2.12: Por dos razones. La primera es porque la tabla de verdad es muy grande. Recuerde que la tabla de verdad es la descripción en extenso de la función, lo que supone que tienen que aparecer todas y cada una de las posibles combinaciones de las configuraciones de las variables de entrada. Por tanto, en este caso hay que comparar cada una de las palabras A con todas y cada una de las palabras B. Como tenemos palabras de 4 bits, el número de palabras posibles es de 24=16. Esto supone que la tabla de verdad tendrá 16x16 = 256 filas.

La segunda es porque, si hemos conseguido hacer la tabla de verdad, el siguiente paso es la minimización de la función que, como podemos comprobar está formada por términos mínimos de 8 bits (2<sup>8</sup>=256 términos mínimos), luego no podemos aplicar Karnaugh directamente. Hay que minimizarla aplicando directamente los teoremas y postulados del Algebra de Boole y operando, lo cual resulta bastante laborioso y, además la probabilidad de cometer algún error es alta.

\*\*

- P.2.13: ¿Podrían explicar de forma más detallada cómo se implementa el razonamiento seguido para obtener las expresiones lógicas del comparador de 2 palabras de n bits?

- R.2.13: Para hacerlo más sencillo y sin pérdida de generalidad, vamos a explicar la comparación entre 2 palabras de 3 bits. Al final generalizaremos las expresiones obtenidas y obtendremos las expresiones generales para n bits.

Partimos de la descripción en lenguaje natural de las condiciones que deben cumplirse para que una palabra de 3 bits  $(A=A_2A_1A_0)$  sea mayor que otra  $(B=B_2B_1B_0)$  teniendo en cuenta que  $A_2$  y  $B_2$  son los bits mas significativos y  $A_0$  y  $B_0$  los menos significativos: Para ello, vamos a analizar y a especificar todas las posibilidades que se nos pueden presentar.

A continuación transcribimos estas expresiones descritas en lenguajes natural a funciones lógicas. Para ello recordemos que las variables o condiciones unidas mediante la conectiva "y" pasan a ser variables o funciones unidas por la función lógica *AND* (una cosa y la otra es la *intersección* de ambas) y las unidas por "o" pasan a representarse mediante la función lógica *OR* (una cosa o la otra es la *unión*).

Así, decimos que A>B si se verifica que:

1: A<sub>2</sub> es mayor que B<sub>2</sub> (con independencia de lo que ocurra con el resto de los bits, puestos que son menos significativos). Por ejemplo, A=100 siempre será mayor que B=011. Observemos que esto es lo mismo que cuando comparamos números decimales. Por ejemplo, sabemos que 2xx es mayor 1zz porque 2>1.

Como las variables A y B sólo pueden tomar el valor 0 ó el 1, para que A sea mayor que B tiene que ser A=1 y B=0, de los contrario A nunca sería mayor que B.

Por tanto, esta condición la representamos por:

$$A_2 > B_2 = A_2 \overline{B}_2$$

También resulta A>B si se verifica que:

2:  $A_2$  es igual a  $B_2$  y  $A_1$  es mayor que  $B_1$  (por ejemplo, A=110 y B=101).

Esta condición tiene dos partes.  $A_2 = B_2 y A_1 > B_1$

$A_2 = B_2$  se cumple cuando ambas toman el valor "1" ( $A_2=1$   $\boldsymbol{y}$   $B_2=1$ )  $\boldsymbol{o}$  cuando ambas toman el valor "0" ( $A_2=0$   $\boldsymbol{y}$   $B_2=0$ ). Por lo que la representamos mediante  $A_2$   $B_2$  +  $\overline{A}_2$   $\overline{B}_2$ .

$A_1 > B_1$  se cumple cuando  $A_1=1$  **y**  $B_1=0$  y la representamos por  $A_1 \overline{B}_1$

Por tanto, esta condición la podemos expresar por:

$$(A_2 = B_2)$$

$\mathbf{y}$   $(A_1 > B_1) = (A_2 B_2 + \overline{A}_2 \overline{B}_2) + A_1 \overline{B}_1$

Finalmente, también se verifica que A> B si:

3:  $A_2$  es igual a  $B_2$  y  $A_1$  es igual a  $B_1$  y  $A_0$  es mayor que  $B_0$  (por ejemplo, A=111 y B=110).

Razonando de la misma forma que lo hemos hecho anteriormente podemos represntar esta condición mediante la expresión lógica

$$(A_2 = B_2) \mathbf{y} (A_1 = B_1) \mathbf{y} (A_0 > B_0) = (A_2 B_2 + \overline{A}_2 \overline{B}_2) (A_1 B_1 + \overline{A}_1 \overline{B}_1) (A_0 \overline{B}_0)$$

Por tanto podremos decir que la función que expresa que A > B es:

$$A > B = (A_2 > B_2) \mathbf{o} \left[ (A_2 = B_2) \mathbf{y} (A_1 > B_1) \right] \mathbf{o} \left[ (A_2 = B_2) \mathbf{y} (A_1 = B_1) \mathbf{y} (A_0 > B_0) \right] =$$

$$= A_2 \overline{B}_2 + (A_2 B_2 + \overline{A}_2 \overline{B}_2) (A_1 \overline{B}_1) + (A_2 B_2 + \overline{A}_2 \overline{B}_2) (A_1 B_1 + \overline{A}_1 \overline{B}_1) (A_0 \overline{B}_0)$$

Si simplificamos esta expresión sustituyendo las condiciones de igualdad por la variable E de forma que:  $E_i = (A_i = B_i) = (A_i B_i + \overline{A}_i \overline{B}_i)$  resulta:

$$A > B = A_2 \ \overline{B}{}_2 + E_2 \ A_1 \ \overline{B}{}_1 + E_2 \ E_1 \ A_0 \ \overline{B}{}_0$$

Si generalizamos esta expresión a palabras de n bits, obtenemos la de la comparación de 2 palabras de n bits. Así,

$$A > B = A_{n-1} \overline{B}_{n-1} + E_{n-1} A_{n-2} \overline{B}_{n-2} + E_{n-1} E_{n-2} A_{n-3} \overline{B}_{n-3} + \cdots + E_{n-1} E_{n-2} E_{n-3} \cdots E_2 E_1 A_0 \overline{B}_0 \cdots$$

Si particularizamos para palabras de 4 bits podemos ver que coincide con la que se obtiene en la salida C del circuito de la *figura 5.17 del texto*.

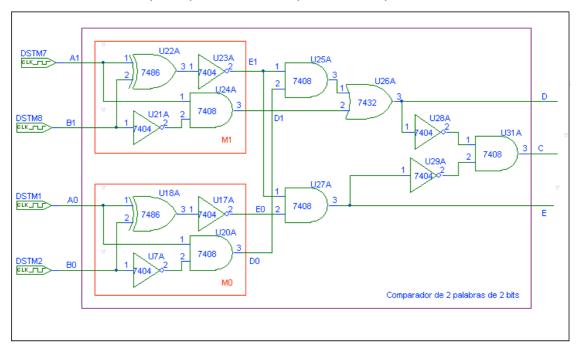

- P.2.14: He diseñado un comparador de dos bits (dos palabras de un bit cada una) y quiero diseñar un comparador de dos palabras de 2 bits usando el diseño anterior como bloque funcional básico. ¿Cómo puedo hacerlo?

- R.2.14: Este problema está resuelto de forma recursiva en el ejercicio E.5.4 del Libro de Problemas. Sin embargo, si no queremos hacer un diseño recursivo, el diseño resulta más sencillo.

Así, partimos de 2 bloques como el de la *figura 5.16* que vamos a usar como bloque funcional básico de diseño. Al primer bloque lo vamos a llamar  $M_0$ . Sus entradas son las correspondientes a los dos bits menos significativos,  $A_0$  y  $B_0$ , y sus salidas son los resultados de la comparación de dichos bits de entrada,  $D_0$  ( $A_0 > B_0$ ),  $E_0$  ( $A_0 = B_0$ ) y  $C_0$  ( $A_0 < B_0$ ). Análogamente, las entradas y salidas del bloque  $M_1$  correspondiente a los bits más significativos son  $A_1$ ,  $B_1$ ,  $D_1$  ( $A_1 > B_1$ ),  $E_1$  ( $A_1 = B_1$ ) y  $C_1$  ( $A_1 < B_1$ ). Por tanto, las entradas del circuito resultante de la unión de ambos serán  $A_0$ ,  $B_0$ ,  $A_1$ ,  $B_1$  y las salidas las llamaremos D (A > B), E (A = B) y C (A < B).

Veamos la forma de realizar el diseño mediante el razonamiento lógico:

Uno de los puntos más importante a tener en cuenta es el significado de las variables de salida de cada uno de los bloques. Este es el motivo de ponerlas entre paréntesis. Así, para el bloque correspondiente a la comparación de los bits más significativos tenemos:

$$D_1(A_1>B_1)$$

,  $E_1(A_1=B_1)$  y  $C_1(A_1.$

Y para el bloque correspondiente a la comparación de los bits menos significativos:

$$D_0 (A_0 > B_0), E_0 (A_0 = B_0) y C_0 (A_0 < B_0).$$

El otro punto a tener en cuenta es que, para cada bloque, estas salidas son *mutuamente* exclusivas. Es decir, si una de las salidas de un bloque toma el valor "1" las otras dos tienen que valer "0", no pueden tomar el valor "1". Esto supone que podemos trabajar con la igualdad y una de las desigualdades, pues la otra desigualdad es una consecuencia inmediata.

El razonamiento lógico a seguir es análogo al que se realiza en el texto para comparar palabras de 4 bits, pero adaptándolo a las salidas de los dos bloques. Así, la palabra A es mayor que la palabra B si el bit más significativo de la palabra A ( $A_1$ ) es mayor que el bit más significativo de la palabra B ( $B_1$ ) o bien, los dos bits más significativos de ambas palabras son iguales y el bit menos significativo de la palabra A ( $A_0$ ) es mayor que bit menos significativo de la palabra B ( $B_0$ ). Si traducimos esto a las variables lógicas de salida de los bloques resulta:

$$D(A>B)=1$$

**si**  $D_1(A_1>B_1)=1$  **ó**  $E_1(A_1=B_1)=1$  **y**  $D_0(A_0>B_0)=1$

Para pasar de la descripción en *lenguaje natural* a la descripción en *lenguaje formal* tenemos que sustituir las conjunciones del lenguaje natural "ó" e "y" por las expresiones del lenguaje formal **OR** (unión) y **AND** (intersección) respectivamente, y la palabra "si" por el "=".

$$D(A>B) = D_1(A_1>B_1) \text{ OR } E_1(A_1=B_1) \text{ AND } D_0(A_0>B_0)$$

$D=D_1+E_1\cdot D_0$

Por tanto:

Actuando de forma análoga para la variable E, obtenemos:

$$E(A=B)=1$$

si  $E_1(A_1=B_1)=1$  y  $E_0(A_0=B_0)=1$

Es decir:

$E = E_1 \cdot E_0$

19/46

La expresión de C(A < B) = 1 la obtenemos de forma inmediata ya que, al ser las variables de salida mutuamente exclusivas, podemos razonar que A es menor que B cuando no es ni mayor ni igual. Por tanto,

$$C(A < B) = 1$$

si  $D(A > B) = 0$  y  $E(A = B) = 0$ .

O sea:

$$C = \overline{D} \cdot \overline{E}$$

Por tanto, el circuito que implementa al comparador de 2 palabras de 2 bits es:

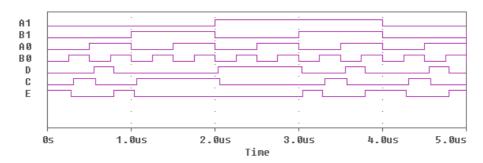

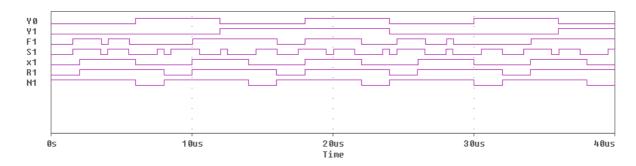

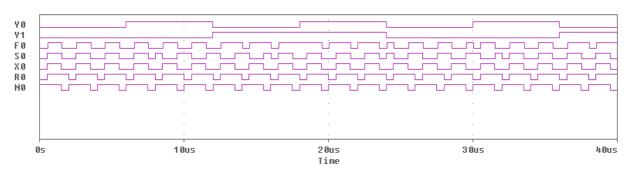

Y el cronograma resultante de su simulación es:

Como podemos ver en el cronograma, no hay ninguna respuesta en la que dos de las salidas tomen el valor 1 a la vez, con lo que verificamos que estas señales son mutuamente exclusivas. Además, se verifica que la variable de salida D(A>B) toma el valor 1 ante las siguientes configuraciones de entrada:

$$(A=01, B=00), (A=10, B=00), (A=10, B=01), (A=11, B=00), (A=11, B=01) y (A=11, B=10)$$

Como podemos comprobar, estas configuraciones son todas las configuraciones de dos bits en las que se verifica que A>B.

Análogamente, E(A=B) toma el valor 1 ante las 4 configuraciones de entrada en las que ambas palabras son iguales, Es decir:

Finalmente, C(A<B) toma el valor 1 ante el resto de las configuraciones de entrada que son aquellas en las que, como podemos comprobar, A es menor que B y son:

Otra forma de realizar el mismo diseño es mediante la tabla de verdad de los bloques previamente diseñados. Partimos de las mismas señales:

$$D_1 (A_1 > B_1), E_1 (A_1 = B_1) y C_1 (A_1 < B_1)$$

$D_0 (A_0 > B_0), E_0 (A_0 = B_0) y C_0 (A_0 < B_0).$

Al ser las salidas de los bloques mutuamente exclusivas nos encontramos con bastantes términos mínimos que no se van a presentar nunca, por lo que obtenemos una tabla de verdad con muchos *términos mínimos indiferente* que nos van a facilitar la minimización. Así, la tabla de verdad es:

| Salidas de  | los bloques                   | Salida del circuito |

|-------------|-------------------------------|---------------------|

| $D_0$ $E_0$ | D <sub>1</sub> E <sub>1</sub> | DEC                 |

| 0 0         | 0 0                           | 0 0 1               |

| "           | 0 1                           | 0 0 <b>1</b>        |

| "           | 1 0                           | 100                 |

| "           | 1 1                           | XXX                 |

| 0 1         | 0 0                           | 0 0 <b>1</b>        |

| "           | 0 1                           | 0 1 0               |

| "           | 1 0                           | 100                 |

| "           | 1 1                           | ххх                 |

| 1 0         | 0 0                           | 0 0 <b>1</b>        |

| "           | 0 1                           | 100                 |

| "           | 1 0                           | 100                 |

| "           | 1 1                           | ххх                 |

| 1 1         | 0 0                           | ххх                 |

| "           | 0 1                           | ххх                 |

| "           | 1 0                           | ххх                 |

| "           | 1 1                           | ххх                 |

El diagrama de Karnaugh para la minimización de la variable de salida *D* es:

| D <sub>1</sub> E <sub>1</sub> | 00 | 01 | 11 | 10 |

|-------------------------------|----|----|----|----|

| $D_0E_0$                      |    |    |    |    |

| 00                            |    |    | X  | 1  |

| 01                            |    | _  | Х  | 1  |

| 11                            | X  | X  | x  | X  |

| 10                            |    | 1  | X  | 1  |

21/46

Así, la expresión minimizada de D es: D = D1 + E1 D0

Análogamente para E obtenemos:

| D <sub>1</sub> E <sub>1</sub> | 00 | 01 | 11 | 10 |

|-------------------------------|----|----|----|----|

| $D_0E_0$                      |    |    |    |    |

| 00                            |    |    | X  |    |

| 01                            |    | 1  | х  |    |

| 11                            | X  | x  | X  | X  |

| 10                            |    |    | X  |    |

Por tanto,  $E = E_1 E_0$

Finalmente, para C obtenemos:

| D <sub>1</sub> E <sub>1</sub> | 00 | 01 | 11 | 10 |

|-------------------------------|----|----|----|----|

| $D_0E_0$                      |    |    |    |    |

| 00                            |    | 1  | X  |    |

| 01                            | 1  |    | X  |    |

| 11                            | X  | X  | X  | X  |

| 10                            | 4  |    | X  |    |

$$C = \overline{D}_1 \ \overline{E}_1 + \overline{D}_0 \ \overline{E}_0 \ E_1 = \overline{D} \ \overline{E}$$

En resumen las expresiones de salida del comparador de 2 palabras de 2 bits son:

$$D = D1 + E1 D0$$

$$E = E_1 E_0$$

$$C = \overline{D} \overline{E}$$

Que, como podemos comprobar, coinciden con las calculadas previamente.

- P.2.15: Estudiando el comparador de la figura 5.17 me surge la duda acerca de las variables "E". En cada puerta AND entra un bit de la palabra A, el bit correspondiente de la palabra B y una E. ¿Qué señales son las "Ei" y de dónde proceden?

- **R.2.15**: Usando la misma nomenclatura del comparador de un bit de la *figura 5.16*, la "E" significa que ambos bits son iguales. Es decir, *E=1* si los correspondientes bits de las dos palabras

toman el mismo valor y E=0 si toman diferentes valores. Por tanto, E procede de la salida de una puerta XNOR cuyas entradas son los bits a comparar.

El circuito de la fig.5.17 es sólo el circuito de extensión del circuito comparador a palabras de 4 bits, como se indica en su pie de figura. Por lo tanto, a este circuito hay que anteponerle los detectores de igualdad entre cada pareja de bits de las palabras A y B, así como los inversores de la palabra B. Es decir, a este circuito hay que anteponerle 4 puertas XNOR y cuatro inversores. A cada una de las puertas XNOR le entra un bit de la palabra A y el equivalente de la B dando lugar a las correspondientes  $E_i$  como consecuencia de que  $A_i$  es igual a  $B_i$ . Así, a la primera XNOR le debe entrar  $A_3$  y  $B_3$  y a su salida generará  $E_3$ , que uniremos a la entrada  $E_3$  del circuito de la figura 5.17. De igual forma ocurre con el resto de los bits de las palabras A y B, generando así las entradas  $E_2$ ,  $E_1$  y  $E_0$ .

De esta forma tenemos un comparador de 2 palabras de 4 bits y, como el diseño es modular, lo podemos ampliar a palabras de 8 bits con sólo unir en serie dos circuitos iguales a este, de forma que las salidas C y E del comparador correspondiente a las palabras de los 4 bits menos significativos las conectamos a las entradas C' y E' del comparador correspondiente a las palabras de los 4 bits más significativos.

#### P.2.16: No entiendo cómo funciona el circuito comparador de la figura 5.17.

**R.2.16:** Si observamos la parte superior correspondiente a las 4 primeras puertas AND del circuito de la *figura 5.17*, vemos que el número de entradas de las puertas AND se va incrementando de forma que, en cada una van entrando todas las "E" de los bits superiores. Así, en la AND superior sólo entran los bits más significativos,  $A_3$  y  $\overline{B}_3$ . En la siguiente puerta entra  $A_2$ ,  $\overline{B}_2$  y  $E_3$ . En la siguiente  $A_1$ ,  $\overline{B}_1$   $E_3$  y  $E_2$  y en la cuarta entran los bits menos significativos y las señales correspondientes a la igualdad del resto de los bits, es decir,  $A_0$ ,  $\overline{B}_0$ ,  $E_3$ ,  $E_2$ . y  $E_1$ . Esto supone que en la salida de cada una de estas puertas AND obtenemos un sumando de la expresión de la función que cumple con la condición de que A es mayor que B (*expresión* [5.15], pag 286 del texto). El resultado de estas puertas AND se suma en la puerta OR de salida obteniéndose a partir de estas cuatro puertas AND la expresión:

$$A_3 \ \overline{B}_3 + A_2 \ \overline{B}_2 E_3 + A_1 \ \overline{B}_1 E_3 E_2 + A_0 \ \overline{B}_0 E_3 E_2 E_1$$

En la parte inferior de la figura vemos que hay otras dos puertas AND de 5 entradas.

La salida de primera de estas puertas AND también se suma con las salidas de las puertas anteriores y sus entradas son todas las  $E_i$  y una entrada adicional correspondiente a  $C'\left(A_n'>B_n'\right)$ . Por tanto, su salida es:  $E_3E_2E_1E_0C'\left(A_n'>B_n'\right)$  cuyo significado es que todos los bits de las dos palabras que compara este comparador coinciden pero, además, el resultado de la comparación de los bits de la palabra anterior ha sido  $A_n>B_n$ . Así, la salida del circuito,  $C\left(A_n>B_n\right)$  corresponde a que la palabra A que entra en este bloque es mayor que la palabra B o que, siendo ambas palabras iguales, en

23/46

la comparación de las palabras del bloque anterior el resultado fue que A era mayor que B. Por tanto:

$$C(A_n > B_n) = A_3 \overline{B}_3 + A_2 \overline{B}_2 E_3 + A_1 \overline{B}_1 E_3 E_2 + A_0 \overline{B}_0 E_3 E_2 E_1 + C' E_3 E_2 E_1 E_0$$

Veamos el significado físico.

Esta expresión, C, consta de cinco sumandos, de forma que basta con que uno de ellos tome el valor "1" para que la función sea "1". Así, el primer sumando  $A_3$   $\overline{B}_3$  es igual a "1" cuando  $A_3 = 1$  y  $B_3 = 0$  ( $A_3$   $\overline{B}_3 = 1$ ), o sea, cuando el bit más significativo de la palabra A de 4 bits es mayor que el más significativo de la palabra B, por lo tanto, en este caso ya podemos afirmar que la palabra A es mayor que la B. El segundo sumando es  $A_2$   $\overline{B}_2$   $E_3$  que toma el valor de 1 cuando  $A_2 = 1$ ,  $B_2 = 0$  y  $E_3 = 1$ , o sea, cuando los bits más significativos de ambas palabras son iguales ( $E_3 = 1$ ) y el segundo bit de la palabra A,  $A_2$ , es mayor que el correspondiente de la palabra B,  $B_2$ , por lo tanto, ahora también podemos afirmar que la palabra A es mayor que la B. De igual forma operan los otros dos sumandos. Es decir, con esto queda implementado el razonamiento lógico que se presenta en el texto (página 286). Finalmente, el último sumando toma el valor uno cuando todos los bits de la palabra A son iguales que los de la palabra B, o sea, que la palabra A y la B coinciden, pero el bit de entrada C' que procede de la comparación del bloque anterior, en el caso de diseño modular y expansión de la comparación a más bits, toma el valor "1".

Por último, existe una última puerta AND en la que le entran todas las E, incluida la del resultado de la comparación del supuesto bloque anterior,  $E'\left(A_n' = B_n'\right)$ , por lo que en su salida tenemos la expresión correspondiente a  $E\left(A_n = B_n\right)$ . Es decir:

$$E(A_n = B_n) = E'E_3E_2E_1E_0$$

Así, a expresión E(A=B) de la salida del comparador se hace "1" cuando los bits de las palabras A y B son iguales dos a dos y, además, en el caso de usar el bloque para la expansión de dicha función, el resultado de la comparación de los bits menos significativos también es "1", es decir, los bits menos significativos también coinciden dos a dos.

En resumen, este es un módulo comparador de palabras de 4 bits que tiene la posibilidad de expandirse para comparar palabras de más bits sin más que conectar varios módulos como este en serie de forma que las salidas D y E de un módulo se conectan a las entradas D' y E' del siguiente.

En el caso de que usemos este módulo como bloque único porque las palabras a comparar sean sólo de 4 bits o si lo usamos para expandir la comparación a palabras de más de 4 bits y este bloque es el correspondiente a los 4 bits menos significativos, la entrada C' la debemos poner a "0" para hacer que el sumando  $C'E_3E_2E_1E_0$  tome el valor "0" y no afecte al resultado de la comparación. Obsérvese que si C'=1 y A=B, la salida del

comparador es C=1, que significa que A>B, lo cual es falso. Así mismo, la entrada E' la debemos poner a "1".

+++

- P.2.17: ¿Qué significan las variables de entrada que aparecen en la parte inferior del circuito comparador de la figura 5.17? La que están representadas como: C' (A'n > B'n) y E' (A'n=B'n)

- R.2.17: De acuerdo con la explicación dada en la pregunta anterior estas señales corresponden a las entradas que hacen que el circuito comparador de palabras de 4 bits se pueda expandir a palabras de más bits (8, 12, 16, ...). Es decir, son las líneas con las que vamos a enlazar en serie los distintos bloques en el proceso de expansión.

**\* \* \***

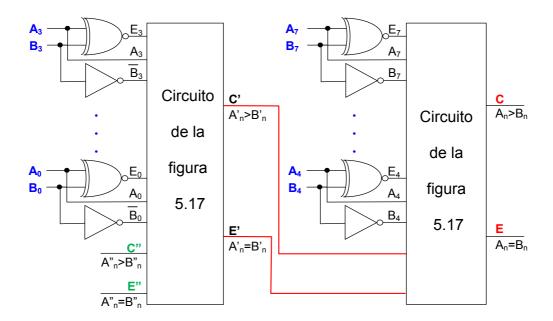

- P.2.18: ¿Cómo sería el circuito completo de un comparador de 2 palabras de 8 bits usando el circuito de expansión de la figura 5.17?

- R.2.18: Generalmente, en Electrónica Digital se intenta que los diseño de los bloque funcionales sean modulares, lo que supone que hay que ver la forma de que determinadas salidas de un módulo se puedan unir a determinadas entradas de otro módulo igual, con el fin de que se pueda ampliar la función a palabras de más bits y sin necesidad de hacer un diseño propósito especial cada vez que se cambia el número de bits. Así, por ejemplo, con el modulo del sumador completo hemos construido un sumador de n bits (ver figura 5.7 pag 273) sin más que conectar el acarreo de salida de un módulo con la entrada del acarreo del módulo del bit inmediato superior. Pues bien, en este módulo del comparador la conexión entre dos módulos se hace a través de las entradas C'(A'<sub>n</sub>>B'<sub>n</sub>) y E'(A'<sub>n</sub>=B'<sub>n</sub>).

Si queremos pasar de un comparador de dos palabras de 4 bits a un comparador de dos palabras de 8 bits usamos dos módulos de este tipo, de forma que el resultado de la comparación de los cuatro bits menos significativos  $(A'_n > B'_n \text{ y } A'_n = B'_n)$  se introduce en las entradas C' y E' del módulo correspondiente a los 4 bits más significativos. Así, si los cuatro bits son todos iguales, pero el resultado de los cuatro bits menos significativos es que A > B entonces el comparador de 8 bits debe producir un "1" en la salida  $A_n > B_n$ , por eso se suma en la puerta OR de salida donde se suman de forma lógica todas las expresiones que hacen que la palabra A sea mayor que la B.

Análogamente, si el resultado de la comparación de la palabra de 4 bits menos significativos es que  $A'_n = B'_n$  y todos los bits de la palabra de los 4 bits más significativos también son iguales, entonces ambas palabras de 8 bits son iguales y aparece un "1" en la salida  $E(A_n=B_n)$ .

Por tanto, el circuito para palabras de 8 bits es:

Lógicamente, las entradas de *C"* y *E"* de la palabra menos significativa hay que ponerlas a valores que no modifiquen la función a realizar, es decir, que no modifiquen *C'* y *E'* (salidas del primer módulo en la figura anterior). Por tanto, habrá que poner *C"* a "0", ya que así la salida de la segunda puerta AND empezando por abajo de la *figura 5.17*, *pag.* 285 es: *E3 E2 E1 E0 C"=0* y no modifica el resultado de la puerta OR que genera las salida *C'* del primer módulo. Por el contrario, hay que poner *E"* a "1" para que tampoco afecte al resultado de la última puerta AND que genera la salida *E'*.

+++

#### P.2.19: ¿Qué diferencia hay entre la comparación lógica y la aritmética?

R.2.19: La diferencia está en que la comparación lógica tiene lugar entre dos palabras cuya representación es en binario puro (sin signo). Por tanto, la comparación se realiza bit a bit. Así, por ejemplo, si comparamos las palabras A= 101 y B= 011, el resultado es A>B. En efecto, el equivalente en decimal de estas dos palabras en binario puro es: A=9 y B=3.

Sin embargo, la comparación aritmética tiene lugar entre números positivos y negativos cuyo valor equivalente en decimal depende de que el tipo de representación binaria sea en S-M, C-1 ó C-2. Como en estas representaciones el bit más significativo toma el valor "1" para los números negativos y "0" para los positivos, la comparación no se puede hacer bit a bit, ya que nos daría como resultado que los números negativos son mayores que los positivos, cosa que no es cierta. Por ejemplo, si suponemos que las palabras A y B anteriores corresponden a números representados en S-M, el resultado correcto es que B>A ya que, A=101 representa en S-M al número decimal -1 y B=011 representa al +3. Por tanto, el algoritmo de comparación es distinto y depende del tipo de representación que estemos considerando.

\*\*

#### P.2.20: No entiendo la tabla de la figura 5.19.

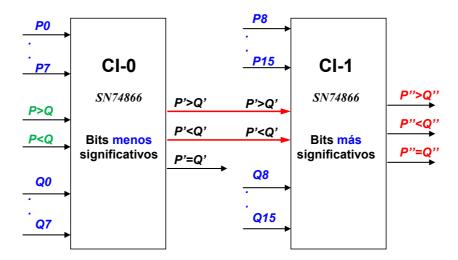

R.2.20: La figura 5.19 es la tabla de verdad que da el fabricante del circuito SN74866.

El significado de las distintas columnas de la tabla de verdad es el siguiente:

**Primera columna,** encabezada con "Comparación". Especifica el tipo de comparación que realiza y que puede ser lógica (entre 2 palabras binarias de 8 bits) o aritmética (2 palabras de 8 bits en complemento a 2).

**Segunda columna**, encabezada con "L/noA". Esta entrada es la señal que controla el tipo de operación que realiza, de forma que, si la ponemos a "1" (H) el circuito realiza la comparación lógica entre las dos palabras de entrada, P y Q. Si por el contrario la ponemos a "0" (L) realiza la comparación aritmética de dichas palabras. Si miramos el símbolo lógico de la *figura 5.18* vemos que es la primera línea de entrada de la izquierda (terminal 2 del dispositivo), que está también nombrada como "L/noA" y que se desdobla en dos, una con el epígrafe M(logic) y la otra M(arith, 2s comp). Esta última está negada (esto se pone de manifiesto con el triángulo que aparece en esta entrada del símbolo lógico<sup>1</sup>). Es decir, cada una está nombrada con la función que realiza.

**Tercera columna**, encabezada con "Datos de entrada. P0-P7, Q0-Q7". En esta columna se especifican todas las posibilidades que existen en la comparación de las dos palabras de entrada, P y Q. En la figura 5.18 se corresponden con las 8 líneas de entrada, P0(terminal 18) a P7(terminal 25), una línea para cada bit de la palabra P y P0(terminal 12) a P1(terminal 15) una para cada bit de la palabra P1. A continuación justificaremos la repetición de P2.

**Cuarta columna**, encabezada con "Entradas. P>Q, P<Q". En esta columna se especifican los posibles valores de las entradas procedentes de la comparación realizada por un comparador previo al que estamos considerando. Estas entradas nos permiten ampliar el circuito comparador a palabras de más bits, por ejemplo, podemos comparar palabras de 16 bits (P0-P15 y Q0-Q15, siendo P15 y Q15 los bits más significativos), sin más que conectar los dos circuitos en cascada, o sea, conectando las salidas del primer comparador a estas entradas del segundo, como se muestra en la siguiente figura.

<sup>&</sup>lt;sup>1</sup> Ver Apéndice B: Símbolos Lógicos de texto base, pags. 725-734

En este caso, los bits de las palabras del primer comparador serán menos significativos que los de las palabras del segundo comparador.

Analicemos los valores que van tomando las filas de estas columnas. En las dos primeras filas aparece "x". Esto significa que es indiferente el valor que toma. O sea, que P'>Q' puede tomar el valor "1" (quiere decir que P' es mayor que Q') ó "0" (quiere decir que P' no es mayor que Q') porque no modifica el resultado de la comparación entre P8-P15 y Q9-Q15. Observe que en estos casos, si la palabra formada por P8-P15 es mayor que Q8-Q15 podemos afirmar que P>Q con independencia de si P0-P7 es mayor o menor que Q0-Q7. El razonamiento es análogo para Q>P.

Siguiendo con los valores de esta columna, vemos que aparece repetido 4 veces P=Q, pero en las siguientes columnas, las encabezadas con P>Q y P<Q como entradas, aparecen las cuatro posibilidades que se pueden presentar en la comparación de la palabra previa (los bits menos significativos). Es decir, que no sea ni mayor ni menor, o sea, que sea igual, que sea P'<Q', que sea P'>Q' o que sea P'>Q' y P'<Q' a la vez. Esta última situación, es incoherente ya que una cosa no puede ser, a la vez, mayor y menor que otra. Pero como en el circuito existen las entradas P>Q y P<Q que se pueden poner fijas a valores "0" ó "1", está claro que se pueden poner ambas señales a 1, es una posibilidad física que tiene el circuito y, por tanto la tiene que contemplar, aunque no tenga sentido al interpretarla, dando como resultado la misma salida P'>Q' y P'<Q' para el primer comparador y P''>Q'' y P''<Q'' para el segundo. Además, estas señales que no tienen sentido físico, pero que se pueden presentar y se presentan, se pueden usar, por ejemplo, como señales de detección de error o como señales de control de otro circuito que forme parte de un sistema más complejo y del que también forme parte el comparador.

**Quinta columna**, encabezada con "Salidas. P>Q, P<Q, P=Q". Son las tres salidas del circuito en las que aparecerá un "0" ó un "1" dependiendo del resultado de la comparación.

En el símbolo lógico del circuito aparecen otras señales de control que actúan facilitando los biestables D de entrada y de salida de datos, pero que no vamos a explicar porque queda fuera del alcance de este tema. Lo estudiaremos más adelante, en la lógica secuencial.

Para el que tenga interés en saber más acerca de este circuito integrado, adjuntamos como anexo al final de este documento las hojas de características del dispositivo fabricado por Texas Instruments. Es interesante ver el circuito interno que proporciona dicho fabricante.

Características del comparador integrado SN74AS866A de Texas Instruments

#### **DETECTOR DE PARIDAD**

P.2.21: ¿Qué función realiza un detector/generador de paridad?

R.2.21: Un detector/generador de paridad/imparidad es un circuito que presenta en su salida un "1" cuando la suma de los "1" de los bits de la palabra de entrada es par/impar. Es decir, si tenemos palabras de 2 bits, las palabras que tienen un número de "1" par son: 00 y 11. El resto, 01 y 10, tiene un número de "1" impar. Por tanto, el circuito detector de paridad debe producir un "1" ante las entradas 00 y 11 y producir un "0" ante las entradas 01 y 10. Recordemos que la función lógica anticoincidencia la implementamos con una puerta XNOR y que, inversamente, la función coincidencia la implementamos con la puerta XOR. Por tanto, el circuito que detecta la paridad en una palabra de 2 bits es una puerta XNOR de 2 entradas, una para cada bit, y el que detecta la imparidad es la puerta XOR.

Comprobémoslo a través de las Tablas de verdad:

| En | tradas | Salida                  | as                        |

|----|--------|-------------------------|---------------------------|

| A  | В      | F <sub>P</sub><br>(par) | F <sub>I</sub><br>(impar) |

| 0  | 0      | 1                       | 0                         |

| 0  | 1      | 0                       | 1                         |

| 1  | 0      | 0                       | 1                         |

| 1  | 1      | 1                       | 0                         |

A partir de la Tabla de verdad obtenemos:

$$F_{P} = \overline{A} \overline{B} + A B = \overline{A \oplus B}$$

$$F_{I} = \overline{A} B + A \overline{B} = A \oplus B$$

P.2.22: ¿Cómo funciona el circuito detector de paridad de la figura 5.21, página 290 del texto?

R.2.22: Para ver el funcionamiento del circuito detector de paridad vamos a analizar los distintos valores y los significados de las señales en los distintos puntos del circuito.

Está claro que la función XOR es la función *anticoincidancia*. Por lo tanto, a su salida presenta un 1 cuando A es distinto de B, es decir, presenta a la salida un "1" cuando A=1 y B=0 y cuando A=0 y B=1. Dicho de otra forma, cuando a su salida presenta un "1" es porque el número de unos en sus entradas es impar. Luego podemos decir que *la puerta XOR detecta la imparidad*. Por el contrario, presenta "0" cuando ambas entradas coinciden. Es decir, cuando A=B=0 y cuando A=B=1

Si llamamos X a la salida de (A XOR B) e Y a la salida de (C XOR D), tendremos:

X = A XOR B = 1 significa que el número de unos es IMPAR

X = A XOR B = 0 significa que el número de unos es PAR

Lo mismo ocurre con C y D:

Y= C XOR D =1 significa que el número de unos es IMPAR

Y= C XOR D =0 significa que el número de unos es PAR

Veamos lo que ocurre a la salida de la XOR marcada como Z.

Hay que tener en cuenta que, si unimos una palabra cuyo número de unos es PAR (o IMPAR) con otra cuyo número de unos también es PAR (o IMPAR) el resultado es una palabra cuyo número de unos PAR. Mientras que, si unimos una palabra cuyo número de unos es PAR (o IMPAR) con otra cuyo número de unos es IMPAR (o PAR) el resultado es una palabra cuyo número de unos es IMPAR. Es decir, podemos construir la tabla siguiente:

| Palabra-1 | Palabra-2 | Palabra-resultante |

|-----------|-----------|--------------------|

| PAR       | PAR       | PAR                |

| IMPAR     | PAR       | IMPAR              |

| PAR       | IMPAR     | IMPAR              |

| IMPAR     | IMPAR     | PAR                |

La señal Z, de nuevo, es la función XOR de sus entradas (que hemos llamado X e Y). Así, los valores de la columna encabezada con Z será la que indicamos en la siguiente tabla y el significado que tiene que tener, en función de la paridad de sus entradas, es el que aparece en la última columna:

| X=A XOR B | Y= C XOR D | Z=X XOR Y | significado |

|-----------|------------|-----------|-------------|

| 0 (par)   | 0 (par)    | 0         | PAR         |

| 0 (par)   | 1 (impar)  | 1         | IMPAR       |

| 1 (impar) | 0 (par)    | 1         | IMPAR       |

| 1 (impar) | 1 (impar)  | 0         | PAR         |

Luego,

*Z*=0 significa que la palabra de entrada tiene un número PAR de unos.

*Z*=1 significa que la palabra de entrada tiene un número IMPAR de unos.

Hasta aquí todo es coherente y lo que tenemos es un detector de paridad de palabras de 4 bits de tal forma que a su salida presenta un 1 cuando el número de unos es IMPAR y presenta un 0 cuando es PAR. Por tanto, si consideramos que el "1" hace referencia a la función que realiza podemos decir que lo que tenemos es un detector de imparidad (pero esto no tiene gran importancia) si los conceptos están claros.

Pasemos ahora a construir un módulo para que podamos usarlo en el diseño modular, de forma que podamos ampliar el número de bits sin necesidad de hacer un nuevo diseño "ad hoc".

Para ello, de nuevo, usamos una función XOR (la que genera a su salida P).

Vamos a hacer el diseño. Partimos de una señal Z que arrastra un significado, que es:

Z=0 significa PAR

Z=1 significa IMPAR

Queremos que el circuito detecte la PARIDAD, luego la salida deberá ser:

P=1 significa PAR

P=0 significa IMPAR

Veamos los valores que debe tomar P', teniendo en cuenta que P = Z XOR P'. Es decir, vamos a calcular qué valores debe tomar P' para que al realizarse la operación XOR, entre ella (P') y la entrada Z, produzca la P de salida. Así:

| Z         | Р         | P' tal que: P=Z XOR P' |

|-----------|-----------|------------------------|

| 0 (par)   | 0 (impar) | 0                      |

| 0 (par)   | 1 (par)   | 1                      |

| 1 (impar) | 0 (impar) | 1                      |

| 1 (impar) | 1 (par)   | 0                      |

Ahora ya tenemos los valores de P', pero no conocemos su significado aunque a partir de la tabla los podemos determinar. En efecto,

- Si la función XOR de Z=0(PAR) y de P'=0 tiene que dar como resultado P=0(IMPAR), deberemos interpretar que P'=0 significa IMPAR, ya que para que la salida sea IMPAR las entradas tiene que ser (PAR, IMPAR).

- Si la función XOR de Z=0(PAR) y de P'=1 tiene que dar como resultado P=1(PAR), deberemos interpretar P'=1 como PAR.

- Si la función XOR de Z=1(IMPAR) y de P'=1 tiene que dar como resultado P=0(IMPAR), deberemos interpretar P'=1 como PAR.

- Si la función XOR de Z=1 (IMPAR) y de P'=0 tiene que dar como resultado P=1(PAR), deberemos interpretar **P'=0** como **IMPAR**.

#### Luego:

P'=1 (PAR)

P'=0 (IMPAR)

Por último, si comparamos los valores y los significados de *P'* y *P* vemos que ambas tiene el mismo significado para los mismos valores, luego podemos unir dos módulos como el de la figura 5.21 sin necesidad de añadirle ningún circuito adicional.

### **UNIDA ARITMÉTICO-LÓGICA (ALU)**

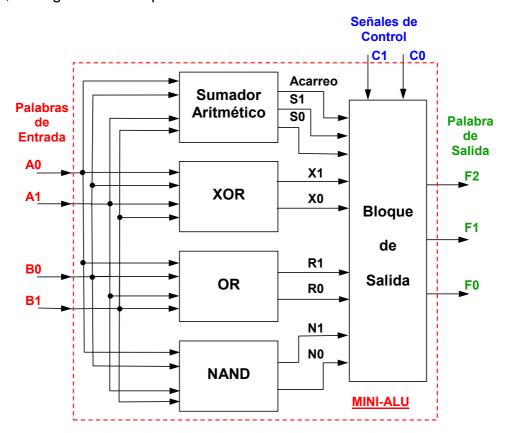

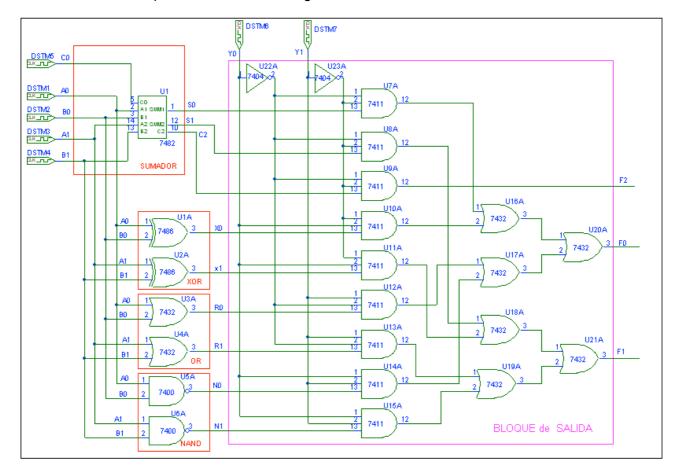

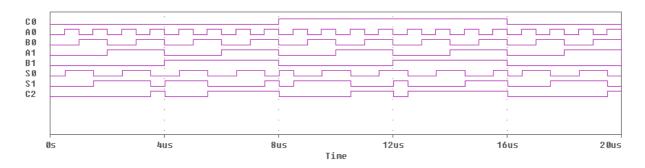

## P.2.23: ¿Cómo podemos diseñar una Mini-ALU que realice 4 operaciones sobre palabras de 2 bits?

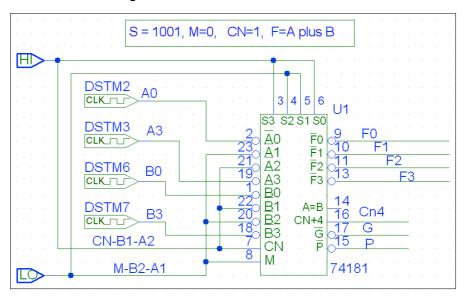

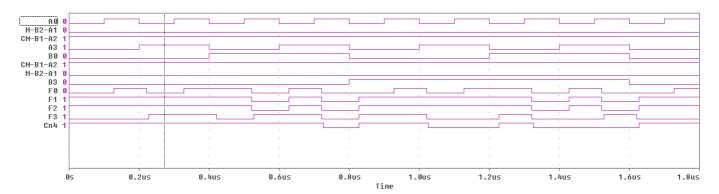

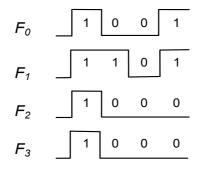

R.2.23: Vamos a responder a esta cuestión realizando el diseño de una Mini-ALU que realice 4 operaciones sobre palabras de 2 bits. Hemos seleccionado una operación aritmética, la SUMA, y tres operaciones lógicas XOR, NOR y NAND,