# Hardware Dinámicamente Reconfigurable

Julio Septien del Castillo Hortensia Mecha López

Curso 3er Ciclo Abril 2003

Departamento de Arquitectura de Computadores y Automática Universidad Complutense de Madrid

1

### Temario

- Tema 1. Introducción al Hw reconfigurable

- Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- Tema 3. Arquitecturas académicas

- Tema 4. Arquitecturas grano grueso

- Tema 5. Problemas de gestión de recursos hw dinámicamente reconfigurables

- Sesiones prácticas

- Presentación de trabajos

## Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx

- 6200

- Virtex

- Virtex II

- 2. Arquitecturas de Altera

- Flex 6000

- Flex 10K

- 3. Arquitecturas de Atmel

- AT 6000

- AT 40K

- 4. Método de configuración de las Virtex

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

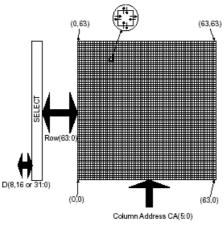

### Arquitecturas de Xilinx. Xilinx 6200

Se trata de una arquitectura de grano fino, de estilo mar de celdas que permite reconfiguración parcial a nivel de celda

| Device                   | XC6209†    | XC6216      | XC6236†     | XC6264†      |

|--------------------------|------------|-------------|-------------|--------------|

| Typical Gate Count Range | 9000-13000 | 16000-24000 | 36000-55000 | 64000-100000 |

| Number of Cells          | 2304       | 4096        | 9216        | 16384        |

| Max. No. Registers       | 2304       | 4096        | 9216        | 16384        |

| Number IOB's             | 192        | 256         | 384         | 512          |

| Cell Rows x Columns      | 48x48      | 64x64       | 96x96       | 128x128      |

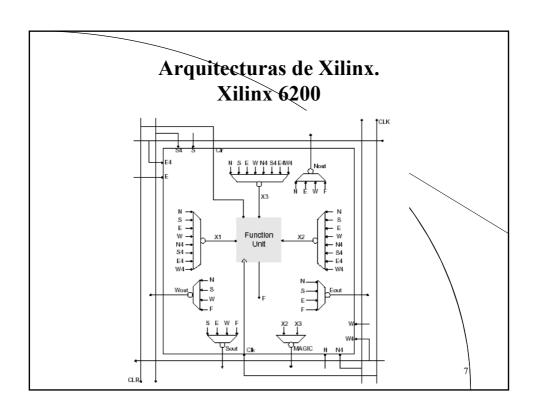

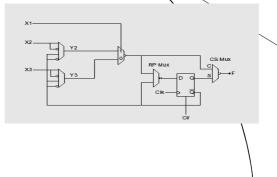

Cada celda básica puede implementar un conjunto de funciones de nivel lógico y dispone de una área de interconexionado para la comunicación entre celdas

Bloque básico Xilinx 6200

Estructura simple, simétrica, jerárquica y regular

La configuración se realiza mediante celdas de SRAM de 6 transistores direccionables desde el exterior

J

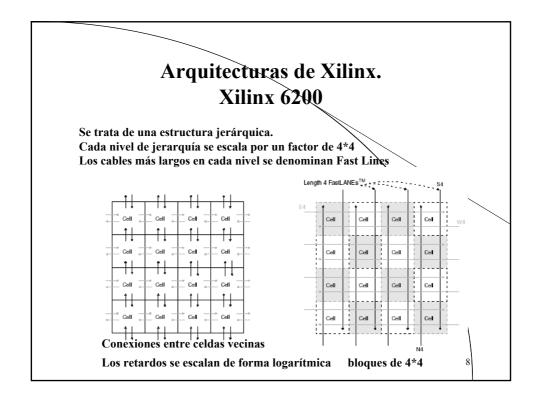

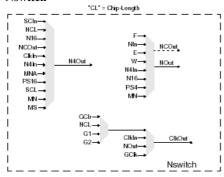

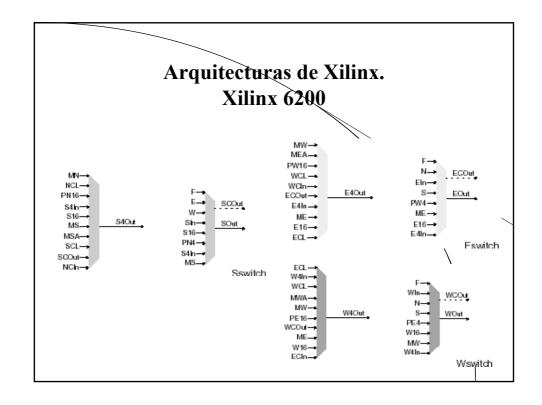

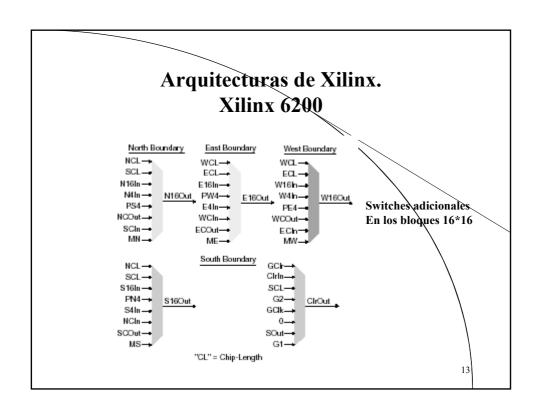

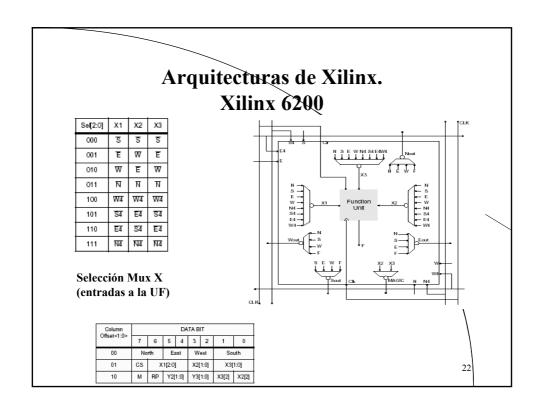

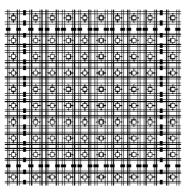

#### Arquitecturas de Xilinx. Xilinx 6200

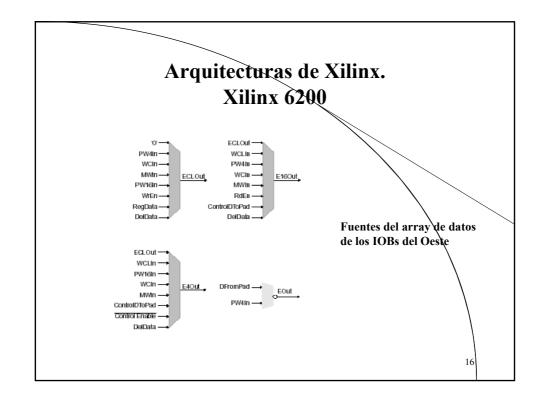

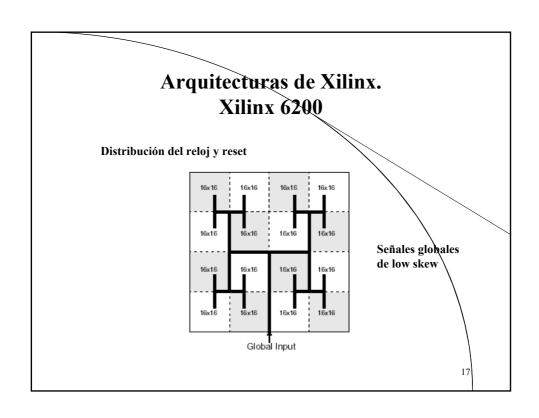

Además hay 4 líneas globales de bajo skew para reset y relojes Magic es para interconexionado Existen interconexiones entre celdas adyacentes, interconexiones de longitud 4 celdas (N4,S4,W4,E4), 16 celdas (N16,S16,W16,E16) y de longitud igual a la del chip

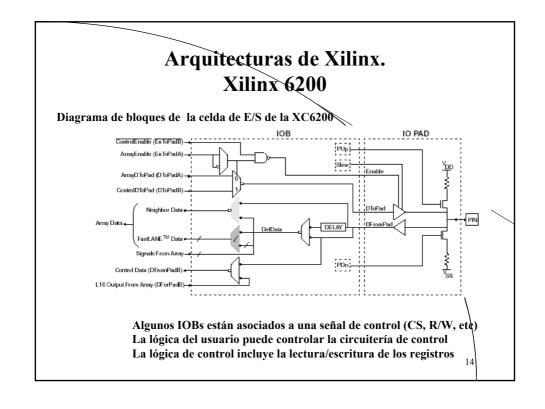

Las salidas de las UFs y los registros pueden leerse desde el exterior

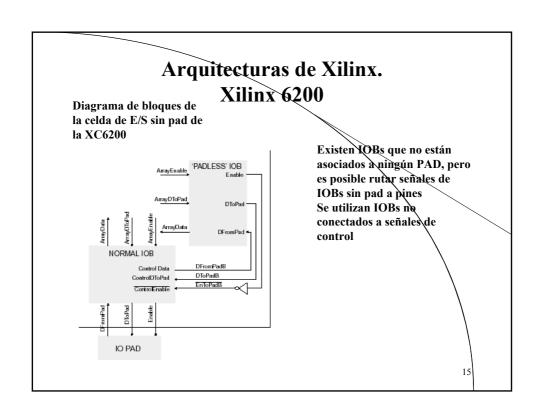

**IOBs**

64 User IOB's (1 per border cell)

bloques de 16\*16

En la XC6216, los bloques de 64\*64 proporcionan las Chip-Length En arquitecturas de mayor tamaño se sigue este proceso con más niveles

> Arquitecturas de Xilinx. Xilinx 6200

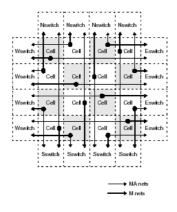

- •En cada bloque existen una serie de switches distribuidos por el borde, que proporcionan las conexiones entre los distintos niveles en la misma posición del array.

- En la figura se muestran los syitches para interconexionado en los alrededores del bloque de 4\*4

- •Cada celda tiene una salida Magic que proporciona conexión directa a dos switches del bloque 4\*4 (M y MA)

#### Nswitch

NCOut: conexión de vecindad si no se tratara de una celda límite (sirve de E al mux 8 a 1)

SCIn: conexión de la celda superior si no hubiera sido celda límite Las conexiones son direccionales, y se etiquetan según\a dirección de la señal

F: salida de la celda N,S,E,W: conexiones de celdas vecinas

N4In, S4In, W4in, E4in: entrada de las interconexiones de longitud 4 NCL,SCL.ECL,WCL: conexiones de longitud igual al chip PS4: conexión dirección S que entra al SSwitch del bloque 4\*4 superior (con. U)

PS16: conexión dirección S del bloque 16\*16 superior ClkIn: entrada de reloj

MN, MS, MNA: entradas Magic 11

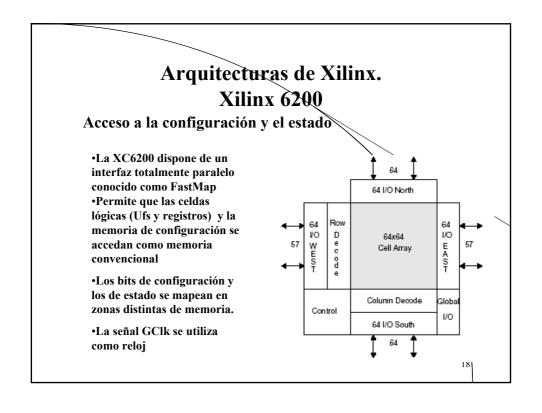

- •El acceso a los bits de estado permite sacar y meter tareas restaurando su estado

- •También es un mecanismo para entrada/salida de datos

- •Cuando se accede al estado, todos los bits que se leen son de estado

- •También existen una serie de recursos para minimizar el número de ciclos para reconfiguración (compresión)

- •Cuando se configura se usa todo el bus de direcciones. Se puede acceder de 8 en 8 bits o bien de 32-bits, en cuyo caso se ignoran los dos bits de direcciones menos significativos

19

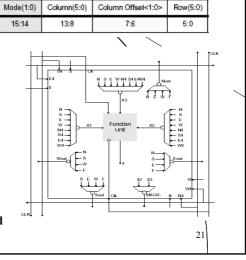

#### Arquitecturas de Xilinx. Xilinx 6200

Acceso a bits de configuración, estado y registros de control

| ٨ | Mode(1:0) | Column(5:0) | Column Offset<1:0> | Row(5:0) |

|---|-----------|-------------|--------------------|----------|

|   | 15:14     | 13:8        | 7:6                | 5:0      |

Formato de dirección de la XC6209 y la XC6216

| Mode(1:0) | Column(6:0) | Column Offset<1:0> | Row(6:0) |

|-----------|-------------|--------------------|----------|

| 17:16     | 15:9        | 8:7                | 6:0      |

Formato de dirección de la XC6236 y la XC6264

| Mode1 | Mode0 | Area Selected                |

|-------|-------|------------------------------|

| 0     | 0     | Cell Configuration and State |

| 0     | 1     | East/West Switch or IOB      |

| 1     | 0     | North/South Switch or IOB    |

| 1     | 1     | Device Control Registers     |

#### Mode 00

| Column<br>Offset<1:0> | DATA BIT |     |         |      |         |      |         |       |

|-----------------------|----------|-----|---------|------|---------|------|---------|-------|

| Oliset<1.0>           | 7        | 6   | 5       | 4    | 3       | 2    | 1       | 0     |

| 00                    | No       | rth | East    |      | West    |      | South   |       |

| 01                    | CS       | Х   | X1[2:0] |      | X2[1:0] |      | X3[1:0] |       |

| 10                    | М        | RP  | Y2[     | 1:0] | Y3[     | 1:0] | X3[2]   | X2[2] |

#### Interconexionado de la celda

| Sel[1:0] | North | South | East | West |

|----------|-------|-------|------|------|

| 00       | F     | F     | F    | F    |

| 01       | И     | Ē     | N    | W    |

| 10       | Έ     | w     | E    | 1/1  |

| 11       | W     | ত     | 8    | 8    |

Selección del multiplexor de vecindad North-East-West-South

| Column<br>Offset<1:0> | DATA BIT |         |      |      |      |      |       |       |

|-----------------------|----------|---------|------|------|------|------|-------|-------|

| Oliset<1.0>           | 7        | 6       | 5    | 4    | 3    | 2    | 1     | 0     |

| 00                    | No       | rth     | East |      | West |      | South |       |

| 01                    | CS       | X1[2:0] |      | X2[  | 1:0] | X3[  | 1:0]  |       |

| 10                    | М        | RP      | Y2[  | 1:0] | Y3[  | 1:0] | X3[2] | X2[2] |

| Sel[1:0] | Y2 | Υ3 |

|----------|----|----|

| 00       | X2 | Х3 |

| 01       | ā  | X3 |

| 10       | X2 | σ  |

| 11       | g  | Ø  |

Configuración de la UF

### Arquitecturas de Xilinx. Xilinx 6200

#### Acceso al estado

Column Offset=11 se usa para acceder al estado.

| Column<br>Offset<1:0> | DATA BIT |         |     |         |     |         |       |       |

|-----------------------|----------|---------|-----|---------|-----|---------|-------|-------|

| Oliset<1.0>           | 7        | 6       | 5   | 4       | 3   | 2       | 1     | 0     |

| 00                    | No       | North   |     | East    |     | est     | South |       |

| 01                    | CS       | X1[2:0] |     | X2[1:0] |     | X3[1:0] |       |       |

| 10                    | М        | RP      | Y2[ | 1:0]    | Y3[ | 1:0]    | X3[2] | X2[2] |

En este caso se lee o escribe 1 bit por celda y los bits de fila de la dirección se ignoran

Todos los bits de estado a los que se accede pertenecen a la misma columna

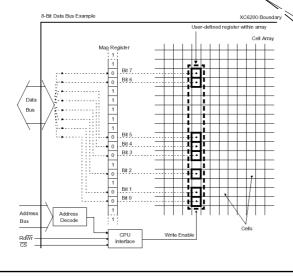

Los datos del bus de datos se determinan por el registro Map Existen un registro Wilcard de columna para escribir simultáneamente en varias celdas de la misma fila

- •Las transferencias de datos pueden ser de 8, 16 o 32 bits, incluso cuando los bits están distribuidos sobre una columna de celdas.

- •Mediante los bits de columna puede acceder a todas las celdas de una columna

- •Las L/E se pueden hacer de hasta 32 bits de una misma columna (en orden correlativo, no necesariamente consecutivas)

Espacio de direcciones

25

### Arquitecturas de Xilinx. Xilinx 6200

El registro Map mapea las celdas de una columna sobre el bús externo (de 8, 16 ó 32 bits)

Un bit a 0 indiça que debe

Un bit a 0 indica que debe accederse a la celda de dicha fila Si hay más 0's que bits

Si hay más 0's que bits válidos, el patrón del bus se repite

Puede escribirse una columna completa con un patrón de 8 bits

#### Mecanismos para comprimir configuraciones:

Registro de máscara Registro de "wildcard"

#### Registro de máscara

Un "1" en un bit de este registro indica que el bit correspondiente del bus de datos no es relevante (ni se lee ni se escribe)

Este registro se ignora durante las lecturas y escrituras de los registros de control

27

### Arquitecturas de Xilinx. Xilinx 6200

#### Registro de Wildcard

- •Permite acceder a varias filas simultáneamente

- •Un 1 en un bit de este registro indica que el bit de dirección correspondiente es irrelevante

- •Se desactiva en las escrituras a los registros de control y cuando se lee el estado

00010 00110 Registro especial de wildcard 00100

#### Muy útil en diseños regulares

Existe otro registro de wildcard para columnas (también activo en escrituras de estado) Sirve para escribir en varios bancos simultáneamente

#### Registro de configuración del dispositivo

| Bit:      | 7 | 6               | 5 | 4        | 3        | 2 | 1        | 0           |

|-----------|---|-----------------|---|----------|----------|---|----------|-------------|

| Function: | - | Clock<br>Enable |   | TTL/CMOS | Bi<br>Wi |   | Co<br>Sp | nfig<br>eed |

| 06- D M-0         | Data Dara Michie |

|-------------------|------------------|

| Config. Reg [3:2] | Data Bus Width   |

| 00                | 8                |

| 01                | 16               |

| 10                | 32               |

| 11                | Illegal          |

Ancho de bus

| Config. Reg [1:0] | Config Speed |

|-------------------|--------------|

| 00                | GClk/16      |

| 01                | GClk/8       |

| 10                | GClk/4       |

| 11                | GClk/2       |

Velocidad de configuración

29

### Arquitecturas de Xilinx. Xilinx 6200

| A[15:0] | Register          | A[15:0] | Register            |

|---------|-------------------|---------|---------------------|

| C000    | Device Config     | C031    | ID (Byte1) (='i')   |

| C004    | Row Wildcard      | C032    | ID (Byte2) (='I')   |

| C005    | Column Wildcard   | C033    | ID (Byte3) (='i')   |

| C008    | Mask (Byte0)      | C034    | ID (Byte4) (='n')   |

| C009    | Mask (Byte1)      | C035    | ID (Byte5) (='x')   |

| C00A    | Mask (Byte2)      | C036    | ID (Byte6) (=' ')   |

| C00B    | Mask (Byte3)      | C037    | ID (Byte7) (='X')   |

| C010    | Map (Byte0)       | C038    | ID (Byte8) (='C')   |

| C011    | Map (Byte1)       | C039    | ID (Byte9) (='6')   |

| C012    | Map (Byte2)       | C03A    | ID (Byte10) (='0')  |

| C013    | Map (Byte3)       | C03B    | ID (Byte11) (='0')  |

| C014    | Map (Byte4)       | C03C    | ID (Byte12) (='0')  |

| C015    | Map (Byte5)       | C03D    | ID (Byte13) (=' ')  |

| C016    | Map (Byte6)*      | C03E    | ID (Byte14) (=' ')  |

| C017    | Map (Byte7)*      | C03F    | ID (Byte15) (=ID #) |

| C030    | ID (Byte0) (='X') |         |                     |

Mapeo en memoria de los Registros de control de programación

Además de la configuración a través del FastMap permite reconfiguración serie

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx

- 6200

- Virtex

- Virtex II

- 2. Arquitecturas de Altera

- Flex 6000

- Flex 10K

- 3. Arquitecturas de Atmel

- AT 6000

- AT 40K

- 4. Método de configuración de las Virtex

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

31

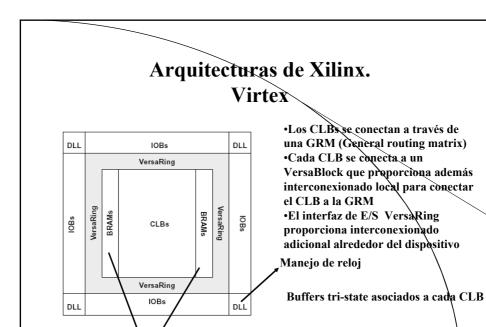

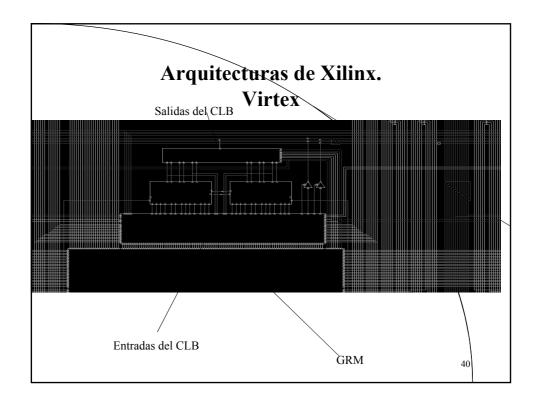

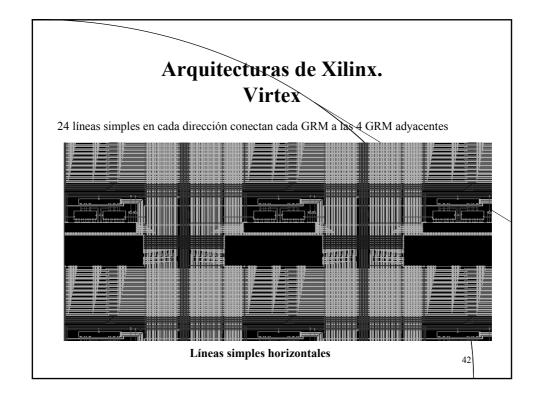

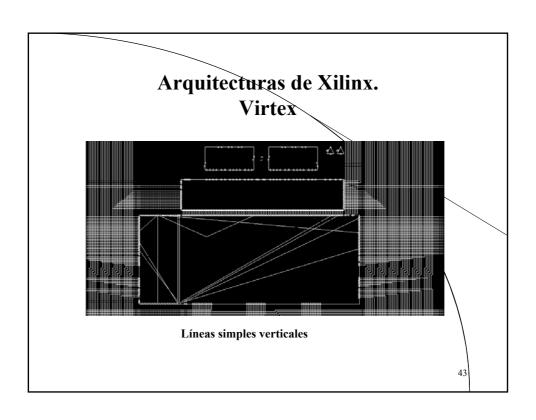

### Arquitecturas de Xilinx.

#### Virtex

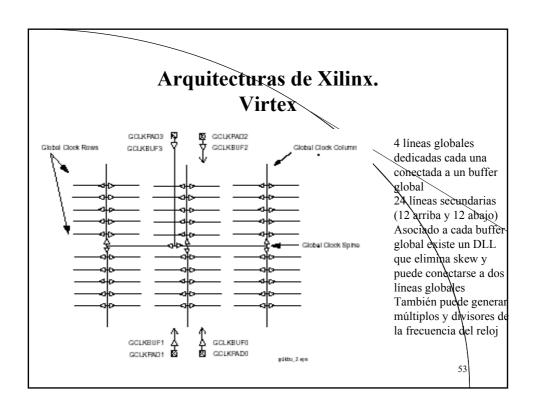

Densidades desde 50K puertas hasta 1Millón de puertas Circuitería para gesión de relojes:

4 DLLs

4 líneas principales para distribución de reloj

24 líneas locales secundarias

#### Table 1: Virtex Field-Programmable Gate Array Family Members.

| Device  | System Gates | CLB Array | Logic Cells | Maximum<br>Available I/O | Block RAM<br>Bits | Maximum<br>SelectRAM+™ Bits |  |  |

|---------|--------------|-----------|-------------|--------------------------|-------------------|-----------------------------|--|--|

| XCV50   | 57,906       | 16x24     | 1,728       | 180                      | 32,768            | 24,576                      |  |  |

| XCV100  | 108,904      | 20x30     | 2,700       | 180                      | 40,960            | 38,400                      |  |  |

| XCV150  | 164,674      | 24x36     | 3,888       | 260                      | 49,152            | 55,296                      |  |  |

| XCV200  | 236,666      | 28x42     | 5,292       | 284                      | 57,344            | 75,264                      |  |  |

| XCV300  | 322,970      | 32x48     | 6,912       | 316                      | 65,536            | 98,304                      |  |  |

| XCV400  | 468,252      | 40x60     | 10,800      | 404                      | 81,920            | 153,600                     |  |  |

| XCV600  | 661,111      | 48x72     | 15,552      | 512                      | 98,304            | 221,184                     |  |  |

| XCV800  | 888,439      | 56x84     | 21,168      | 512                      | 114,688           | 301,056                     |  |  |

| XCV1000 | 1,124,022    | 64x96     | 27,648      | 512                      | 131,072           | 393,216                     |  |  |

Sistema jerárquico de memoria:

de memor 1.- LUTs

2.-Block RAM

•Lógica especial para:

1.acarreo

2.multiplicadores

3.encadenamiento

de funciones

2 columnas de bloques de memoria de 4096 bit/bloque

33

Arquitecturas de Xilinx. Virtex Soporta una gran variedad de estándares de señalización ·Los 3 elementos de almacenamiento pueden funcionar como reloj o como latches •Comparten el reloi •Señales de capacitación individuales •Señal de Set/Reset compartida y configurable Bank0 V V Bank1 Figure 2: Virtex Input/Output Block (IOB Como algunos estándares Virtex necesitan Vcco v Vref existen restricciones sobre la combinación de dichos estándares en cada banco 34

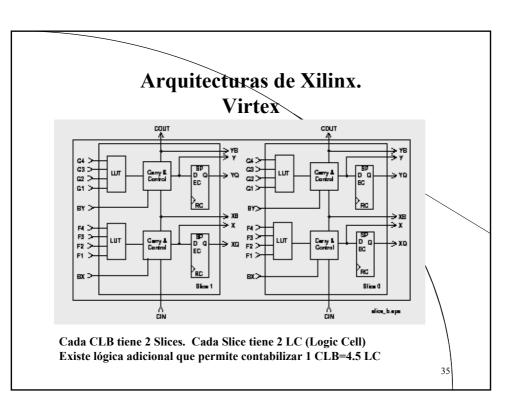

#### Arquitecturas de Xilinx. Virtex

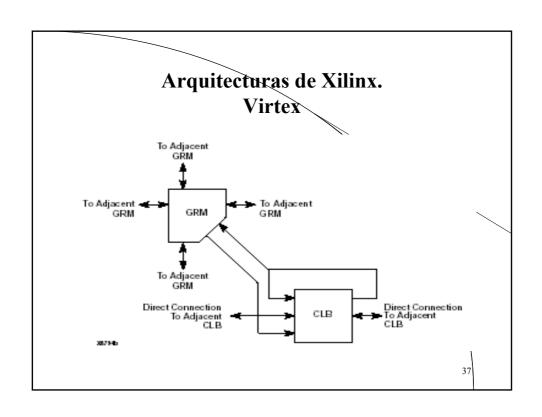

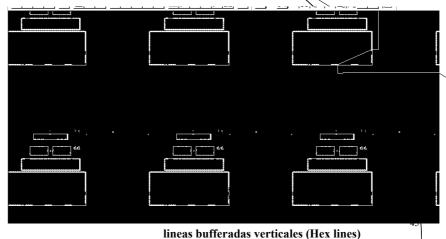

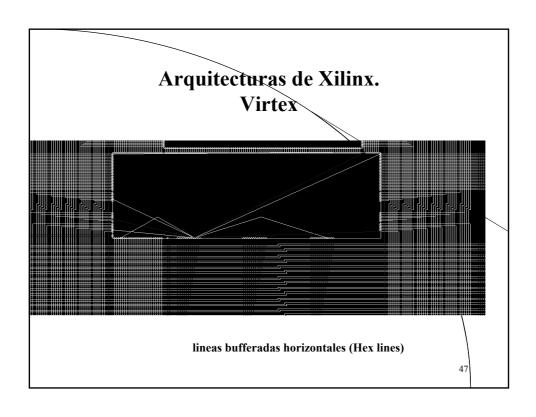

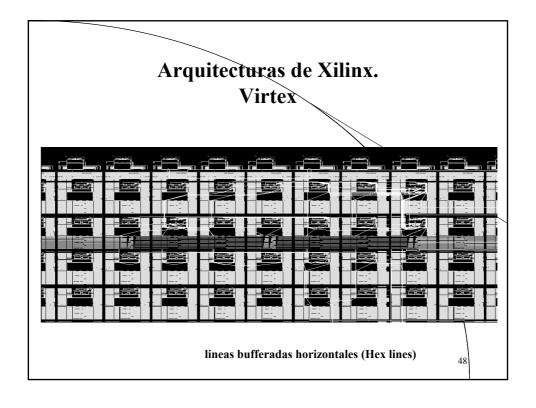

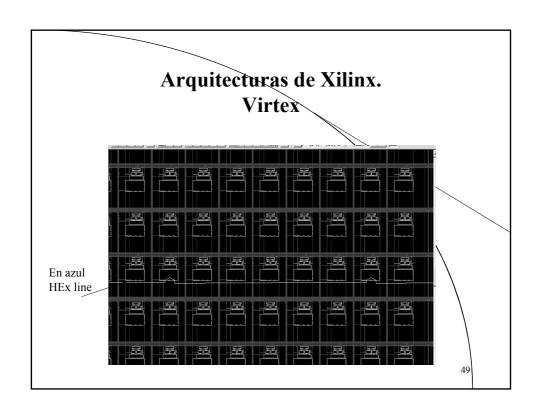

96 lineas bufferadas (Hex lines) en cada dirección conectan cada GRM con otra GRM separada 6 bloques. Se pueden acceder en los extremos y en el punto medio.

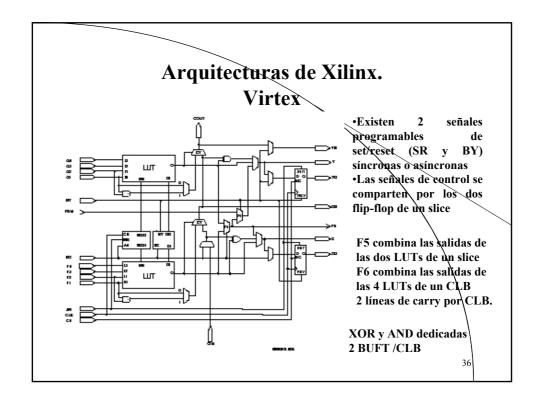

#### Arquitecturas de Xilinx. Virtex

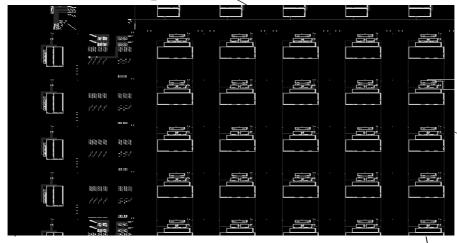

#### Arquitecturas de Xilinx. Virtex **Block Select Ram** Total Block Virtex Device # of Blocks SelectRAM Bits XCV50 10 XCV150 XCV200 14 57.344 XCV300 16 65,536 XCV400 81,920 20 XCV600 24 98,304 Además de la LUT Select RAM 114,688 XCA800 28 existen dos columnas de RAM en XCV1000 131,072 cada Virtex Las columnas de distribuyen en RAMB4\_S#\_S# WEA ENA RSTA bloques síncronos de 4096bits DOA[#:0] (Block SelectRAM) y doble > CLKA ADDRA[#:0] puerto WEB ENB DOB[#:0] RSTB > CLKB 54 300\_da\_008

### Arquitecturas de Xilinx.

Cada bloque de 4096Kbits de memoria ocupa lo que 4 CLBs La cantidad de memoria de este tipo depende del número de filas de CLBs

### Arquitecturas de Xilinx. Virtex

#### • Configuración

| Configuration Mode | M2 | M1 | MO | CCLK Direction | Data Width | Serial D <sub>out</sub> | Configuration Pull-ups |

|--------------------|----|----|----|----------------|------------|-------------------------|------------------------|

| Master-serial mode | 0  | 0  | 0  | Out            | 1          | Yes                     | No                     |

| Boundary-scan mode | 1  | 0  | 1  | N/A            | 1          | No                      | No                     |

| SelectMAP mode     | 1  | 1  | 0  | ln .           | 8          | No                      | No                     |

| Slave-serial mode  | 1  | 1  | 1  | ln .           | 1          | Yes                     | No                     |

| Master-serial mode | 1  | 0  | 0  | Out            | 1          | Yes                     | Yes                    |

| Boundary-scan mode | 0  | 0  | 1  | N/A            | 1          | No                      | Yes                    |

| SelectMAP mode     | 0  | 1  | 0  | In             | 8          | No                      | Yes                    |

| Slave-serial mode  | 0  | -  | 1  | ln .           | 1          | Yes                     | Yes                    |

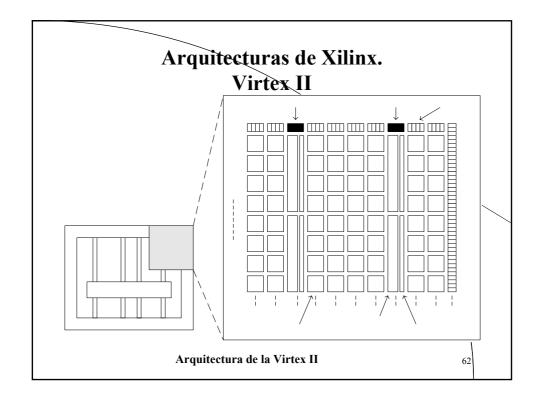

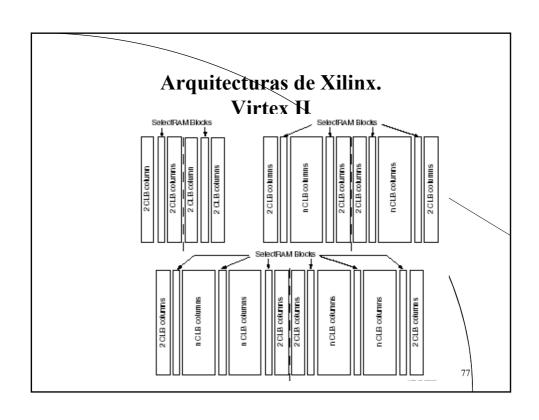

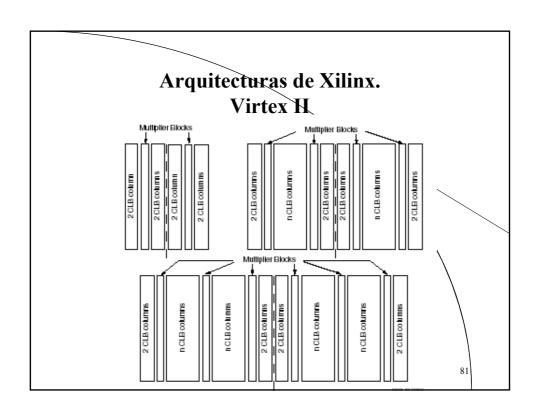

### Arquitecturas de Xilinx. Virtex II

|          |                 | (1 CLB = 4          | CLB<br>slices = N | lax 128 bits)                       |                      | SelectF           | SelectRAM Blocks   |      |                    |

|----------|-----------------|---------------------|-------------------|-------------------------------------|----------------------|-------------------|--------------------|------|--------------------|

| Device   | System<br>Gates | Array<br>Row x Col. | Silces            | Maximum<br>Distributed<br>RAM Kbits | Multiplier<br>Blocks | 18-Kbit<br>Blocks | Max RAM<br>(Kbits) | DCMs | Max I/O<br>Pads(1) |

| XC2V40   | 40K             | 8 x 8               | 256               | 8                                   | 4                    | 4                 | 72                 | 4    | 88                 |

| XC2V80   | 80K             | 16 x 8              | 512               | 16                                  | 8                    | 8                 | 144                | 4    | 120                |

| XC2V250  | 250K            | 24 x 16             | 1,536             | 48                                  | 24                   | 24                | 432                | 8    | 200                |

| XC2V500  | 500K            | 32 x 24             | 3,072             | 96                                  | 32                   | 32                | 576                | 8    | 264                |

| XG2V1000 | 1M              | 40 x 32             | 5,120             | 160                                 | 40                   | 40                | 720                | 8    | 432                |

| XC2V1500 | 1.5M            | 48 x 40             | 7,680             | 240                                 | 48                   | 48                | 864                | 8    | 528                |

| XC2V2000 | 2M              | 56 x 48             | 10,752            | 336                                 | 56                   | 56                | 1,008              | 8    | 624                |

| XC2V3000 | 3M              | 64 x 56             | 14,336            | 448                                 | 96                   | 96                | 1,728              | 12   | 720                |

| XC2V4000 | 4M              | 80 x 72             | 23,040            | 720                                 | 120                  | 120               | 2,160              | 12   | 912                |

| XC2V6000 | 6M              | 96 x 88             | 33,792            | 1,056                               | 144                  | 144               | 2,592              | 12   | 1,104              |

| XC2V8000 | 8M              | 112 x 104           | 46,592            | 1,456                               | 168                  | 168               | 3,024              | 12   | 1,108              |

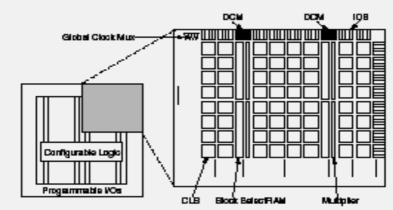

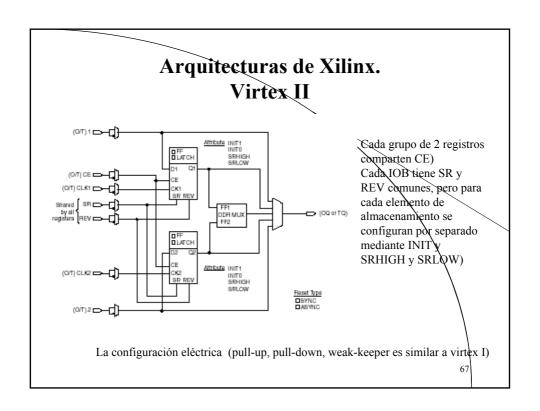

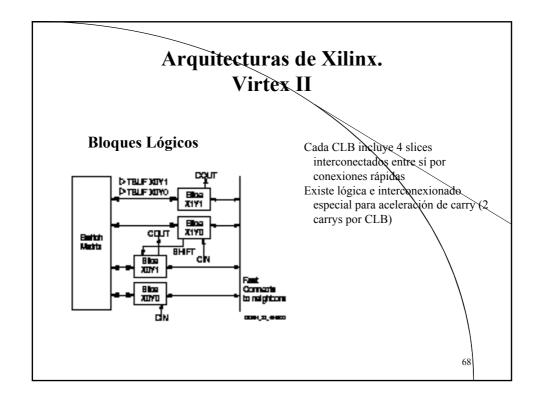

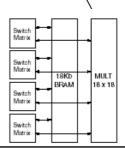

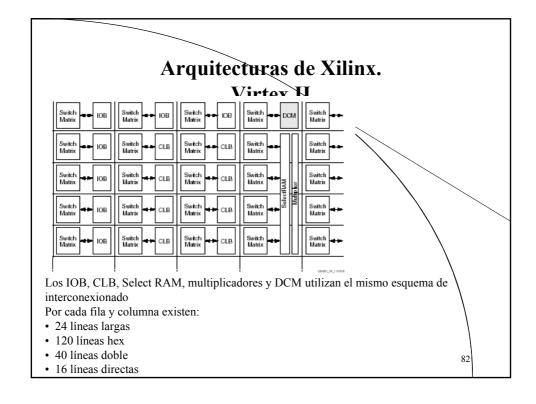

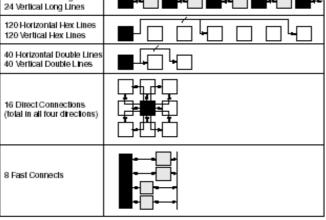

#### Arquitecturas de Xilinx. Virtex II

Block Select RAM como en Virtex I pero en bloques de 18Kbit Dual-Port

Sistema de interconexionado jerárquico: Active Interconnect Technology

Aparecen multiplicadores explícitamente asociados a cada bloque de RAM

Hasta 12 DCM

Arquitecturas de Xilinx. Virtex II

Bank 5

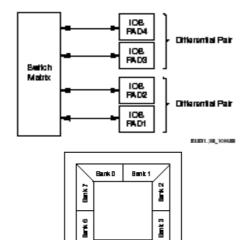

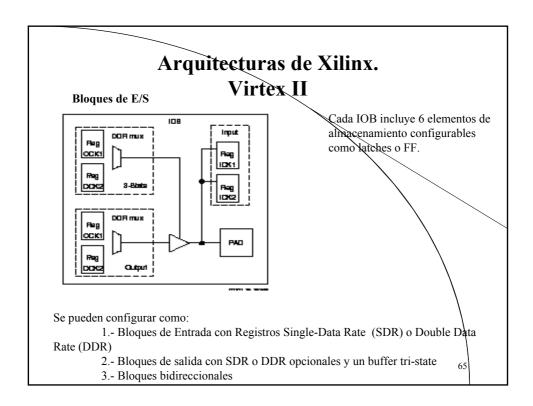

Soporta una amplia variedad de estándares de E/S

Los pares diferenciales se conectan siempre a la misma matriz de conmutación

Se clasifican en bancos, y todos los elementos de un banco están conectados a un determinado VREF y VCCO

Como algunos estándares necesitan VREF y VCCO existen restricciones sobre que estándares pueden combinarse dentro de un mismo banco

# Arquitecturas de Xilinx. Virtex H

| Device   | CLB Array:<br>Row x<br>Column | Number<br>of<br>Silces | Number<br>of<br>LUTs | Max Distributed<br>SelectRAM or Shift<br>Register (bits) | Number<br>of<br>Filp-Flops | Number<br>of<br>Carry-Chains <sup>(1)</sup> | Number<br>of SOP<br>Chains <sup>(1)</sup> |  |

|----------|-------------------------------|------------------------|----------------------|----------------------------------------------------------|----------------------------|---------------------------------------------|-------------------------------------------|--|

| XG2V40   | 8 x 8                         | 256                    | 516                  | 8,192                                                    | 516                        | 16                                          | 16                                        |  |

| XC2V80   | 16 x 8                        | 512                    | 1,024                | 16,384                                                   | 1,024                      | 16                                          | 32                                        |  |

| XG2V250  | 24 x 16                       | 1,536                  | 3,072                | 49,152                                                   | 3,072                      | 32                                          | 48                                        |  |

| XC2V500  | 32 x 24                       | 3,072                  | 6,144                | 98,304                                                   | 6,144                      | 48                                          | 64                                        |  |

| XC2V1000 | 40 x 32                       | 5,120                  | 10,240               | 163,840                                                  | 10,240                     | 64                                          | 90                                        |  |

| XC2V1500 | 48 x 40                       | 7,680                  | 15,360               | 245,760                                                  | 15,360                     | 80                                          | 96                                        |  |

| XC2V2000 | 56 x 48                       | 10,752                 | 21,504               | 344,064                                                  | 21,504                     | 96                                          | 112                                       |  |

| XC2V3000 | 64 x 56                       | 14,336                 | 28,672               | 458,752                                                  | 28,672                     | 112                                         | 128                                       |  |

| XC2V4000 | 80 x 72                       | 23,040                 | 46,080               | 737,280                                                  | 46,080                     | 144                                         | 160                                       |  |

| XC2V6000 | 96 x 88                       | 33,792                 | 67,584               | 1,081,344                                                | 67,584                     | 176                                         | 192                                       |  |

| XC2V9000 | 112 x 104                     | 46,592                 | 93,184               | 1,490,944                                                | 93,184                     | 208                                         | 224                                       |  |

75

# Arquitecturas de Xilinx. Virtex H

### **Block Select RAM**

|          |         | SelectRAM  | Blocks |

|----------|---------|------------|--------|

| Device   | Columns | Per Column | Total  |

| XC2V40   | 2       | 2          | 4      |

| XC2V90   | 2       | 4          | 8      |

| XC2V250  | 4       | 6          | 24     |

| XC2V500  | 4       | 8          | 32     |

| XC2V1000 | 4       | 10         | 40     |

| XC2V1500 | 4       | 12         | 48     |

| XC2V2000 | 4       | 14         | 56     |

| XC2V3000 | 6       | 16         | 96     |

| XC2V4000 | 6       | 20         | 120    |

| XC2V6000 | 6       | 24         | 144    |

| XC2V8000 | 6       | 28         | 168    |

#

| Device   | DIOCKS | III PADICS | III Bits  |

|----------|--------|------------|-----------|

| XG2V40   | 4      | 72         | 73,728    |

| XC2V80   | 8      | 144        | 147,456   |

| XC2V250  | 24     | 432        | 442,368   |

| XC2V500  | 32     | 576        | 589,824   |

| XC2V1000 | 40     | 720        | 737,290   |

| XC2V1500 | 48     | 964        | 884,736   |

| XC2V2000 | 56     | 1,008      | 1,032,192 |

| XC2V3000 | 96     | 1,728      | 1,769,472 |

| XC2V4000 | 120    | 2,160      | 2,211,840 |

| XC2V6000 | 144    | 2,592      | 2,654,208 |

| XC2V9000 | 168    | 3,024      | 3,096,576 |

|          |        |            |           |

# Arquitecturas de Xilinx. Virtex H

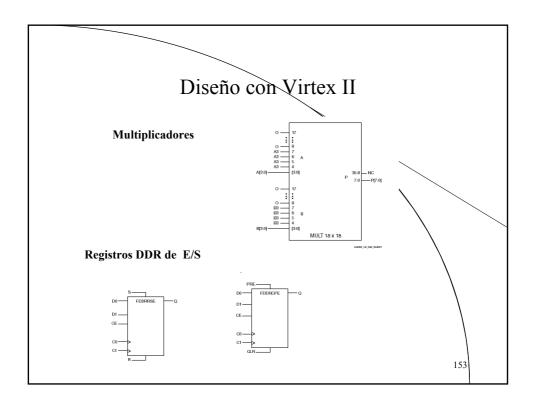

### Multiplicadores

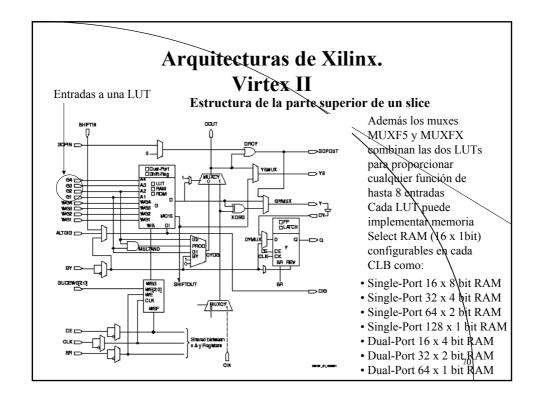

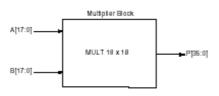

Existe un bloque de SelectRam que puede usarse como entrada al multiplicador, permitiendo la implementación de DSP Cada bloque et un multiplicador es de 18\*18 en C2

El multiplicador y la memoria SelectRAM pueden usarse simultán amente, aunque comparten parte del interconexionado. Existen restricciones de hasta 18 bits de ancho en el uso de la memoria cuando se usa el multiplicador

80

# Arquitecturas de Xilinx. Virtex H

|          |         | Multipl    | lers  |

|----------|---------|------------|-------|

| Device   | Columns | Per Column | Total |

| XC2V40   | 2       | 2          | 4     |

| XC2V90   | 2       | 4          | 8     |

| XC2V250  | 4       | 6          | 24    |

| XC2V500  | 4       | 8          | 32    |

| XC2V1000 | 4       | 10         | 40    |

| XC2V1500 | 4       | 12         | 48    |

| XC2V2000 | 4       | 14         | 56    |

| XC2V3000 | 6       | 16         | 96    |

| XC2V4000 | 6       | 20         | 120   |

| XC2V6000 | 6       | 24         | 144   |

| XC2V8000 | 6       | 28         | 168   |

# Arquitecturas de Xilinx. Virtex H

DEST OF THE

83

# Arquitecturas de Xilinx. Virtex H

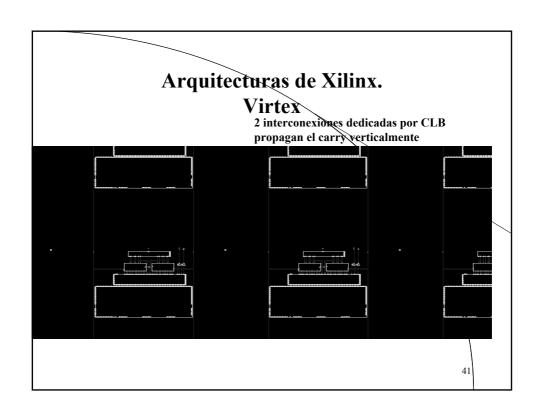

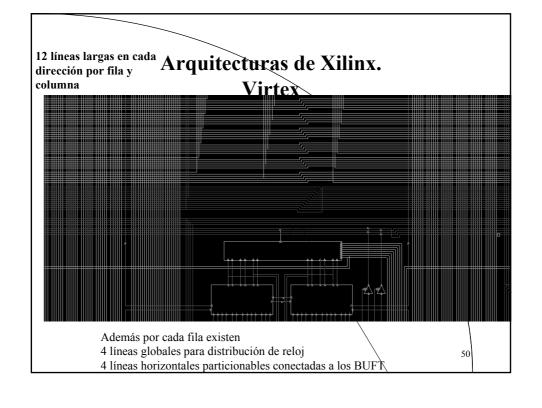

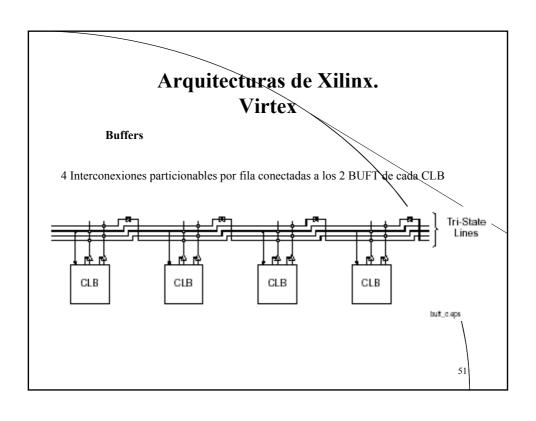

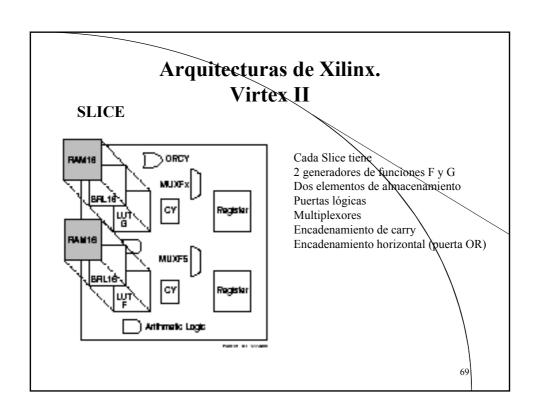

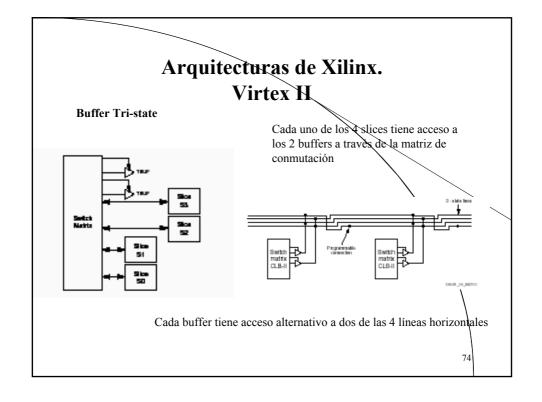

Además tiene el siguiente interconexionado dedicado:

- 1.- 8 líneas de reloj globales por cuadrante

- 2.- 4 líneas horizontales por fila de CLBs conectadas a los buffers 3-state

- 3.- 2 líneas especiales por columna para propagación de carry

- 4.- 2 líneas dedicadas por fila para propagar las salida de la OR con el slice adyacente

- 5.- 1 línea vertical para conectar los registros de desplazamiento de LUT a LUT

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx

- 6200

- Virtex

- Virtex II

- 2. Arquitecturas de Altera

- Flex 6000

- Flex 10K

- 3. Arquitecturas de Atmel

- AT 6000

- AT 40K

- 4. Método de configuración de las Virtex

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

85

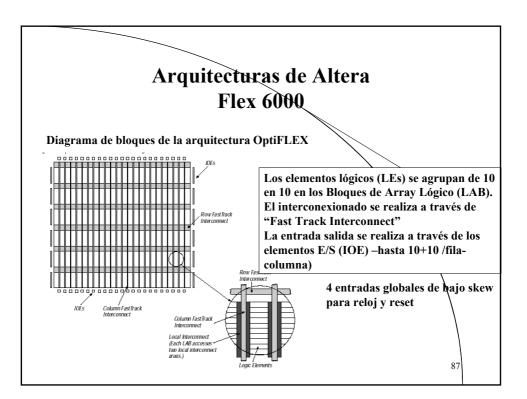

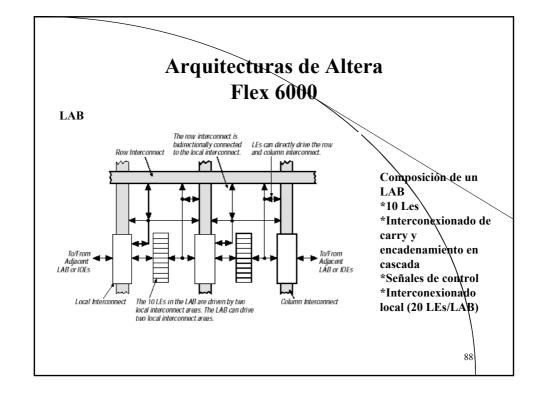

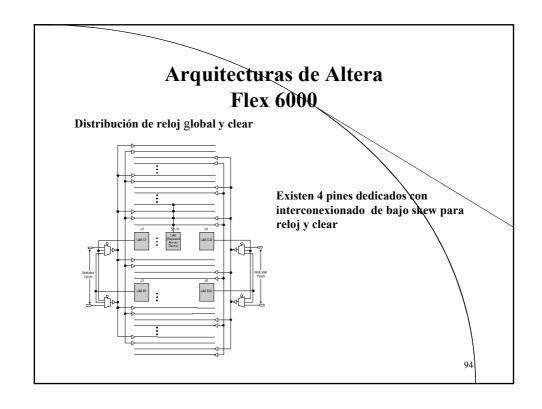

# Arquitecturas de Altera Flex 6000

| Table 1. FLEX 6000 Device Features   |          |         |          |          |  |  |  |  |  |  |  |  |

|--------------------------------------|----------|---------|----------|----------|--|--|--|--|--|--|--|--|

| Feature                              | EPF6010A | EPF6016 | EPF6016A | EPF6024A |  |  |  |  |  |  |  |  |

| Typical gates (1)                    | 10,000   | 16,000  | 16,000   | 24,000   |  |  |  |  |  |  |  |  |

| Logic elements (LEs)                 | 880      | 1,320   | 1,320    | 1,960    |  |  |  |  |  |  |  |  |

| Maximum I/O pins                     | 102      | 204     | 171      | 218      |  |  |  |  |  |  |  |  |

| Supply voltage (V <sub>CCINT</sub> ) | 3.3 V    | 5.0 V   | 3.3 V    | 3.3 V    |  |  |  |  |  |  |  |  |

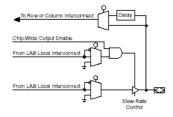

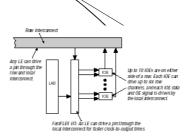

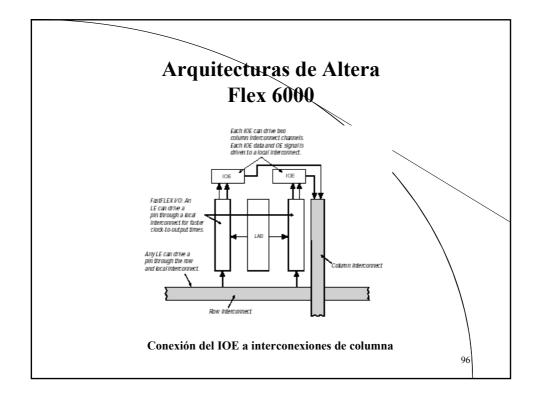

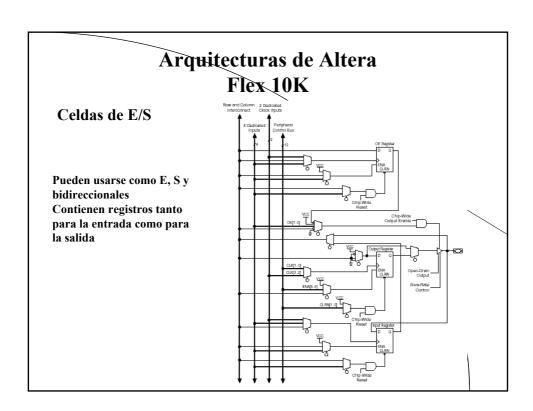

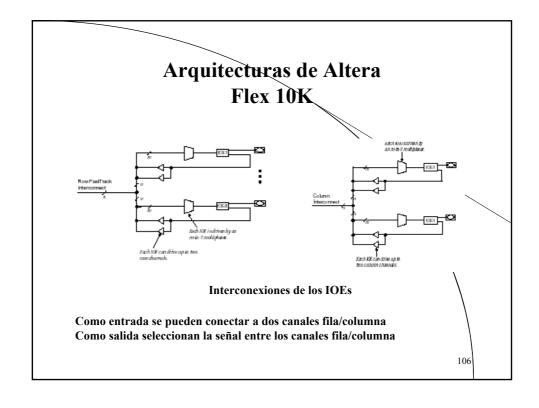

# Arquitecturas de Altera Flex 6000

### Bloques de Entrada /salida

Los IOEs pueden configurarse como entrada, salida o bidireccionales Cada IOE recibe los datos de las interconexiones locales adyacentes Si funciona como entrada se conecta a las interconexiones de fila o columna (hasta 6 filas y 2 columnas por IOE)

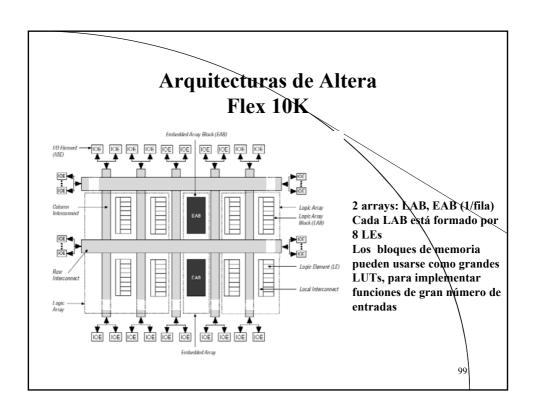

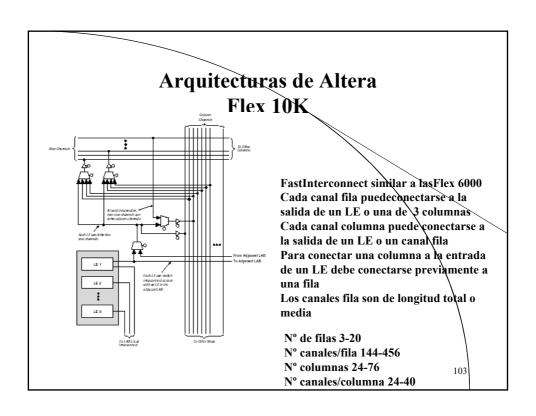

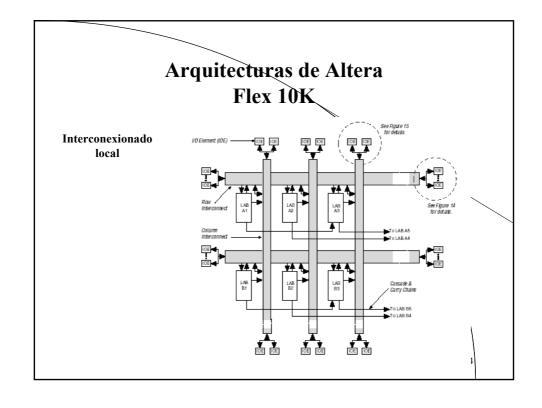

# Arquitecturas de Altera Flex 10K

| Table 1. FLEX 10K Device Featur   | res                   |          |                       |          |                       |

|-----------------------------------|-----------------------|----------|-----------------------|----------|-----------------------|

| Feature                           | EPF10K10<br>EPF10K10A | EPF10K20 | EPF10K30<br>EPF10K30A | EPF10K40 | EPF10K50<br>EPF10K50V |

| Typical gates (logic and RAM) (1) | 10,000                | 20,000   | 30,000                | 40,000   | 50,000                |

| Maximum system gates              | 31,000                | 63,000   | 69,000                | 93,000   | 116,000               |

| Logic elements (LEs)              | 576                   | 1,152    | 1,728                 | 2,304    | 2,880                 |

| Logic array blocks (LABs)         | 72                    | 144      | 216                   | 288      | 360                   |

| Embedded array blocks (EABs)      | 3                     | 6        | 6                     | 8        | 10                    |

| Total RAM bits                    | 6,144                 | 12,288   | 12,288                | 16,384   | 20,480                |

| Maximum user I/O pins             | 150                   | 189      | 246                   | 189      | 310                   |

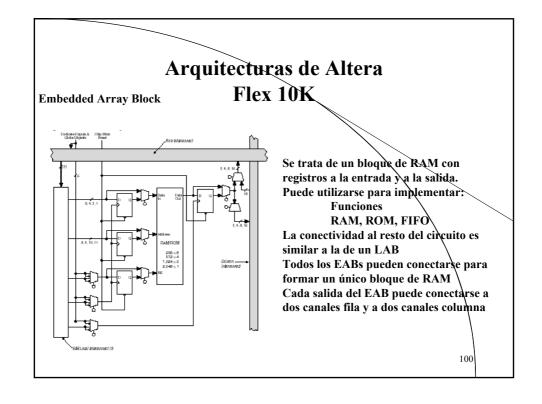

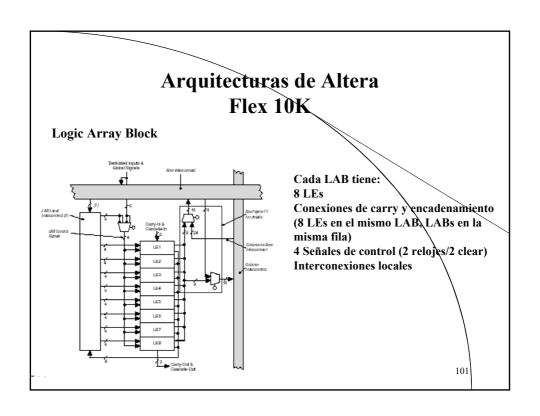

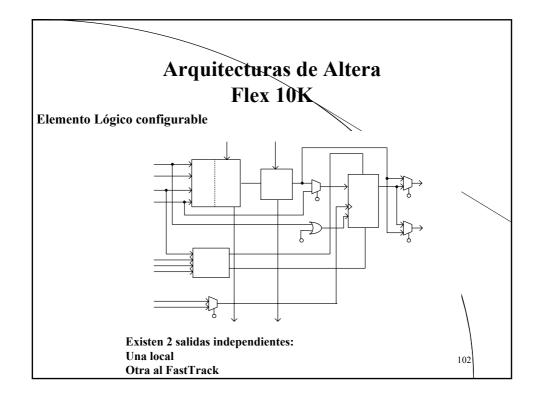

Embedded Array Block (EAB): 2048 bits de RAM/bloque

97

# Arquitecturas de Altera Flex 10K

| Feature                           | EPF10K70 | EPF10K100<br>EPF10K100A | EPF10K130V | EPF10K250A |

|-----------------------------------|----------|-------------------------|------------|------------|

| Typical gates (logic and RAM) (1) | 70,000   | 100,000                 | 130,000    | 250,000    |

| Maximum system gates              | 118,000  | 158,000                 | 211,000    | 310,000    |

| LEs                               | 3,744    | 4,992                   | 6,656      | 12,160     |

| LABs                              | 468      | 624                     | 832        | 1,520      |

| EABs                              | 9        | 12                      | 16         | 20         |

| Total RAM bits                    | 18,432   | 24,576                  | 32,768     | 40,960     |

| Maximum user I/O pins             | 358      | 406                     | 470        | 470        |

Hasta 6 señales de reloj global y 4 clear

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx

- 6200

- Virtex

- Virtex II

- 2. Arquitecturas de Altera

- Flex 6000

- Flex 10K

- 3. Arquitecturas de Atmel

- AT 6000

- AT 40K

- 4. Método de configuración de las Virtex

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

107

# Arquitecturas de Atmel AT6000

# AT6000 Series Field Programmable Gate Arrays

| Device                      | AT6002  | AT6003  | AT6005  | AT6010   |

|-----------------------------|---------|---------|---------|----------|

| Usable Gates                | 6,000   | 9,000   | 15,000  | 30,000   |

| Cells                       | 1,024   | 1,600   | 3,136   | 6,400    |

| Registers (maximum)         | 1,024   | 1,600   | 3,136   | 6,400    |

| I/O (maximum)               | 96      | 120     | 108     | 204      |

| Typ. Operating Current (mA) | 15 - 30 | 25 - 45 | 40 - 80 | 85 - 170 |

| Cell Rows x Columns         | 32 x 32 | 40 x 40 | 56 x 56 | 80 x 80  |

Reconfiguración parcial dinámica

# Arquitecturas de Atmel AT6000

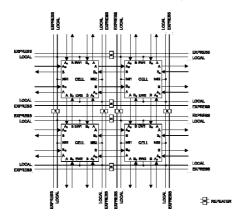

Se trata de una arquitectura basada en una red de celdas sencillas conectadas a una red de buses Alrededor del array existen una serie de celdas de E/S

Cada 8 celdas se colocan unos repetidores de bus Las celdas se pueden utilizar también para conexionado

109

# Arquitecturas de Atmel AT6000

Dos clases de buses:

\*Locales: conectan el array de celdas con la red de buses

\*Express: no se conectan directamente a las celdas y proporcionan grandes velocidades Existen 2 buses Express por fila

y 2 por columna

Los repetidores dividen los buses en segmentos. Permiten las siguientes funciones

1. Aislar segmentos de bus

- 3. Conectar dos segmentos de bus express

- 2. Conectar dos segmentos de bus local

- 4. Transferencia entre bus local y express

# Arquitecturas de Atmel AT6000

Interconexiones de celda a celda y de bus a bus

Existen 2 buses locales para cada columna de celdas NS1 y NS2 Existen 2 buses locales para cada fila de celdas EWL y EW2

En cada sector de 8\*8 los buses locales se conectan a todas las celdas de la fila o columna correspondiente Cada celda puede rutar una señal en 90° (NS1 con EW1 y NS2 con EW2)

111

# Arquitecturas de Atmel AT6000

Estructura de la celda básica

Cada celda recibe 4 conexiones de los buses locales, y 2 entradas (A y B) de cada celda adyacente (N, S, E, W) Una salida A (B) siempre se conecta a una entrada A (B)

Los dos multiplexores de sañ da tienen las mismas señales de control Para escribir un bus local la puerta de paso del bus y la puerta de paso del driver triestado se abren Para conectar LNS1 y LEW1 o LNS2 con LEW2 se abren las dos puertas de paso asociadas

# Arquitecturas de Atmel AT6000

### Distribución de reloj

La distribución se realiza por columnas y permite que diferentes columnas utilicen relojes distintos

Para cada columna se selecciona entre

- \* Reloj global

- \* Bus express

- \* Salida de la primera celda de la columna

- \* Un 1 (columnas combinacionales)

El reloj global se distribuye en una red de bajo skew

La distribución del reset es similar en la parte inferior de cada columna

# Arquitecturas de Atmel AT6000

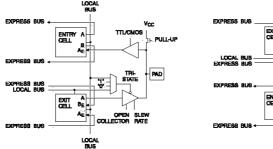

### Entrada/Salida

EXPRESS BUS

LOCAL BUS

EXPRESS BUS

EXPRESS

Hay dos tipos de celdas de E/S:

Tipo A: la salida tipo A de la celda exit se conecta a un driver de salida el buffer de entrada se conecta a la entrada A

Tipo B: la salida tipo B de la celda exit se conecta a un driver de salida el buffer de entrada se conecta a la entrada B

# Arquitecturas de Atmel AT40K

| Device         | AT40K05<br>AT40K05LV | AT40K10<br>AT40K10LV | AT40K20<br>AT40K20LV | AT40K40<br>AT40K40LV |  |  |  |  |  |

|----------------|----------------------|----------------------|----------------------|----------------------|--|--|--|--|--|

| Usable Gates   | 5K - 10K             | 10K - 20K            | 20K - 30K 40K -      |                      |  |  |  |  |  |

| Rows x Columns | 16 x 16              | 24 x 24              | 32 x 32              | 48 x 48              |  |  |  |  |  |

| Cells          | 256                  | 576                  | 1,024                | 2,304                |  |  |  |  |  |

| Registers      | 256 <sup>(1)</sup>   | 576 <sup>(1)</sup>   | 1,024 <sup>(1)</sup> | 2,304 <sup>(1)</sup> |  |  |  |  |  |

| RAM Bits       | 2,048                | 4,608                | 8,192                | 18,432               |  |  |  |  |  |

| I/O (Maximum)  | 128                  | 192                  | 256                  | 384                  |  |  |  |  |  |

Memoria RAM en bloques de 32\*4 bits 8 relojes globales Cache Logic (Reconfiguración Parcial/total dinámica)

115

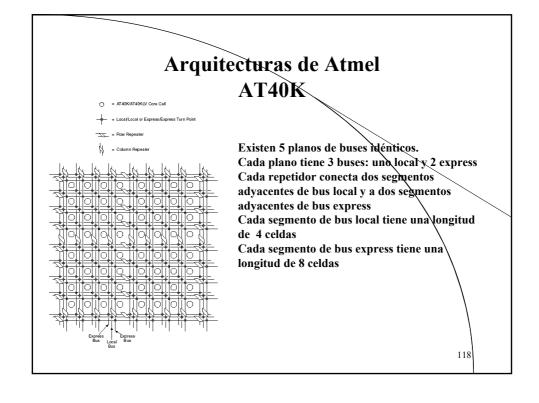

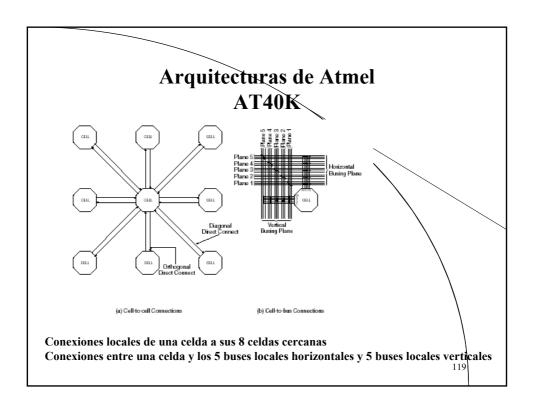

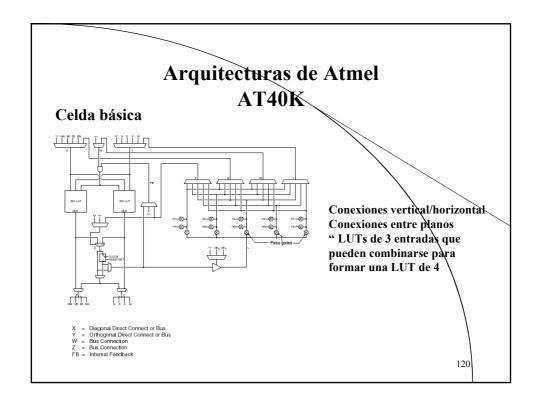

# Arquitecturas de Atmel AT40K

Se trata de un array simétrico de celdas idénticas, separadas cada 4 celdas por repetidores de bus

Las celdas de RAM se colocan en las intersecciones de los repetidores de fila y columna

### Arquitecturas de Atmel AT40K = Horizontal Repeate = Core Cell **BOOOBOOOBOOO** Los repetidores sirven para regenerar las señales y para ■0000■0000■0000■ conectar buses locales y express **-0000-0000-0000** [BAR] [RV ] [RV ] [RV ] [RW ] [RW ] [RV ] [RV ] [RV ] [RW ] [RV ] **-0000-0000-0000-**■0000■0000■ $[M] \ [M] \ [M]$ 117

# Arquitecturas de Atmel AT40K

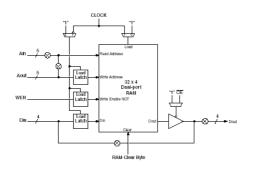

Conexiones de los bloques de RAM

Din<sub>3-0</sub> se conecta a 4 bases locales horizontales distribuidos sobre cuatro filas

Dout<sub>3-0</sub> se conecta a 4 buses locales horizontales distribuidos sobre cuatro filas de la misma columna Ain<sub>4-0</sub> se conecta a 5 buses express horizontales en la misma columna Las lecturas y escrituras se realizan de forma independiente

121

# Arquitecturas de Atmel AT40K

La lectura es asíncrona La escritura puede ser síncrona o asíncrona

# Arquitecturas de Atmel AT40K

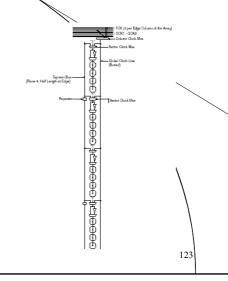

### Distribución de reloj

Existen 8 buses de reloj globales (cada uno conectado a un pin de reloj)

En cada columna existe un mux de reloj de columna. Se encuentra en la parte superior y selecciona uno entre los 8 relojes globales

Cada 4 celdas hay un mux de reloj de sector. Permite seleccionar entre el reloj de columna, el bus express del plano 4 o cte 1. Este reloj puede invertirse

La distribución del reset es similar: Sólo hay un reset global Puede optarse por el bus express del plano 5

# Arquitecturas de Atmel AT40K Celdas de entrada/Salida Existe 3 tipos: primarias, secundarias y de esquina. Se diferencian en la conexión al resto del circuito

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex, Virtex IX

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. Método de configuración de las Virtex

- Organización, estructura y direccionamiento

- Registros de configuración

- Modos de configuración: serie maestro / esclavo, paralelo (SelectMAP)

- Proceso de configuración

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

125

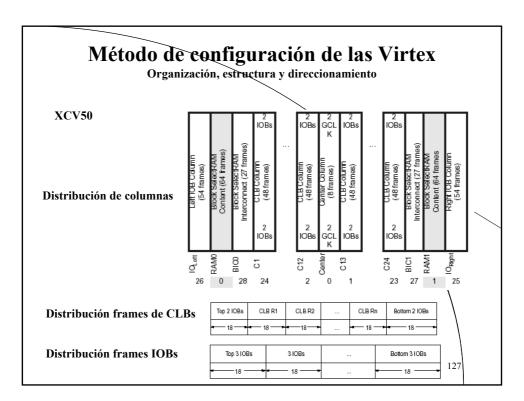

### Método de configuración de las Virtex

Organización, estructura y direccionamiento

- Estructura memoria de configuración como matriz bidimensional.

- División lógica en columnas y frames.

- Una columna está compuesta por distintos frames.

- Frame es la unidad mínima de configuración.

- Dos espacios de direcciones :

- Espacio CLB : Reloj, CLBs, IOBs, interconexión SelectRAM.

- Espacio RAM :bloques de memoria SelectRAM.

|        | . 1    |                   |                    |

|--------|--------|-------------------|--------------------|

| Device | Frames | Bits per<br>Frame | Configuration Bits |

| V50    | 1453   | 384               | 559,232            |

| V100   | 1741   | 448               | 781,248            |

| V150   | 2029   | 512               | 1,040,128          |

| V200   | 2317   | 576               | 1,335,872          |

| V300   | 2605   | 672               | 1,751,840          |

| V400   | 3181   | 800               | 2,546,080          |

| V600   | 3757   | 960               | 3,608,000          |

| V800   | 4333   | 1088              | 4,715,584          |

| V1000  | 4909   | 1248              | 6,127,712          |

# Método de configuración de las Virtex

Organización, estructura y direccionamiento

• Dirección dividida en tres partes : tipo (CLB o RAM), dirección mayor (columna) y dirección menor (nº de frame dentro de la columna).

|                              | # of   |                              |

|------------------------------|--------|------------------------------|

| Column Type                  | Frames | # per Device                 |

| Center                       | 8      | 1                            |

| CLB                          | 48     | # of CLB columns             |

| IOB                          | 54     | 2                            |

| Block SelectRAM Interconnect | 27     | # of Block SelectRAM columns |

| Block SelectRAM Content      | 64     | # of Block SelectRAM columns |

### Método de configuración de las Virtex

Organización, estructura y direccionamiento

Configuración Virtex a través de un "bitstream" compuesto por secuencia de comandos y datos.

### CMD 1 data CMD 2 data CMD 3 data CMD 1

- Dato : en palabras de 32 bits. Relleno con ceros si es preciso.

- Comando: operación de lectura / escritura a un registro de configuración (una o dos palabras).

| Г | Т | уре | 9  | С  | P  |    | Register Address                |   |   |   |   |    |    |    | R  | ŝ۷ |    |   |   | . 1 | Mor | d C | oun | t |   |   |   |   |   |   |   |   |

|---|---|-----|----|----|----|----|---------------------------------|---|---|---|---|----|----|----|----|----|----|---|---|-----|-----|-----|-----|---|---|---|---|---|---|---|---|---|

| 3 | 1 | 30  | 29 | 28 | 27 | 26 | 25 24 23 22 21 20 19 18 17 16 1 |   |   |   |   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |   |   |   |   |   |

| Г | 0 | 0   | 1  | х  | х  | 0  | 0                               | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | Х  | Х  | х | Х | 0   | 0   | х   | х   | х | х | х | х | х | х | х | х | х |

|    | Ţ | уре | 9  | О  | Р  |    |    |    |    |    |    |    |    |    |    |    | ١. | Nor | d Co | oun | t  |    |   |   |   |   |   |   |   |   |   | _ |

|----|---|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|------|-----|----|----|---|---|---|---|---|---|---|---|---|---|

| 31 | 1 | 30  | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14  | 13   | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  |   | 1   | 0  | х  | х  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | х  | х  | х  | Х  | х  | х   | Х    | х   | х  | Х  | х | Х | х | х | Х | х | Х | х | х | х |

129

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex, Virtex IX

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. <u>Método de configuración de las Virtex</u>

- Organización, estructura y direccionamiento de configuración

- Registros de configuración

- Modos de configuración: serie maestro / esclavo, paralelo (SelèctMAP)

- Proceso de configuración completo:

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

## Método de configuración de las Virtex Registros de configuración

| Register Name     | Mnemonic | R/W | Binary Address |

|-------------------|----------|-----|----------------|

| CRC               | CRC      | R/W | 0000           |

| Frame Address     | FAR      | R/W | 0001           |

| Frame Data Input  | FDRI     | W   | 0010           |

| Frame Data Output | FDRO     | R   | 0011           |

| Command           | CMD      | R/W | 0100           |

| Control           | CTL      | R/W | 0101           |

| Control Mask      | MASK     | R/W | 0110           |

| Status            | STAT     | R   | 0111           |

| Legacy Output     | LOUT     | W   | 1000           |

| Register Name        | Mnemonic | R/W | Binary Address |

|----------------------|----------|-----|----------------|

| Configuration Option | COR      | R/W | 1001           |

| Reserved             | _        | _   | 1010           |

| Frame Length         | FLR      | R/W | 1011           |

| Reserved             | -        | _   | 1100           |

| Reserved             | _        | _   | 1101           |

| Reserved             | -        | _   | 1110           |

| Reserved             | _        | _   | 1111           |

| Γ | T | уре | 9  | (  | P  | Τ |    |    |    |    | R  | egi: | ster | Ade | dres | ss |    |    |    |    | R  | ŝ۷ |    |   |   | _ | Nor | d C | oun | t |   |   | _ |

|---|---|-----|----|----|----|---|----|----|----|----|----|------|------|-----|------|----|----|----|----|----|----|----|----|---|---|---|-----|-----|-----|---|---|---|---|

| 3 | 1 | 30  | 29 | 28 | 27 | 2 | 26 | 25 | 24 | 23 | 22 | 21   | 20   | 19  | 18   | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

| Г | ) | 0   | 1  | Х  | х  | ( | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0   | 0    | 0  | х  | х  | х  | х  | 0  | 0  | х  | х | Х | х | х   | х   | Х   | х | Х | х | Х |

131

# Método de configuración de las Virtex Registros de configuración

- Registro de comandos (CMD): controla la lógica de configuración. Operaciones que controla.

- Escribir / Leer en memoria, inicio secuencia de arranque, reseteo registro CRC, cambio frecuencia de reloj, etc ...

| Symbol | Command                  | Binary Code |

|--------|--------------------------|-------------|

| RCRC   | Reset CRC Register       | 0111b       |

| SWITCH | Change CCLK Frequency    | 1001b       |

| WCFG   | Write Configuration Data | 0001b       |

| RCFG   | Read Configuration Data  | 0100b       |

| LFRM   | Last Frame Write         | 0011b       |

| START  | Begin Start-Up Sequence  | 0101b       |

# Método de configuración de las Virtex Registros de configuración

Registro de opciones de configuración (COR): selección de las distintas opciones de configuración.

| - | _            | _     | _     | _      | _  |    |        |       |    |    | _        |    | _  |           |     |    |          |    |            |    |    |           | _ | _ |           |   | _ |           |   | ` |           | _ | ٠. |

|---|--------------|-------|-------|--------|----|----|--------|-------|----|----|----------|----|----|-----------|-----|----|----------|----|------------|----|----|-----------|---|---|-----------|---|---|-----------|---|---|-----------|---|----|

|   | Total Prince | NE PI | ) E D | SINGLE |    |    | OSCERE | 30.00 |    |    | JOSAIJSS |    |    | TOCK WAIT | No. |    | SHUTDOWN |    | DONE_CYCLE |    |    | LCK_CYCLE |   |   | GTS_CYCLE |   |   | GWE_CYCLE |   |   | GSR_CYCLE |   |    |

| 3 | 1            | 30    | 29    | 28     | 27 | 26 | 25     | 24    | 23 | 22 | 21       | 20 | 19 | 18        | 17  | 16 | 15       | 14 | 13         | 12 | 11 | 10        | 9 | 8 | 7         | 6 | 5 | 4         | 3 | 2 | 1         | 0 |    |

| П | )            | х     | х     | х      | х  | х  | х      | Х     | х  | х  | х        | х  | х  | х         | Х   | Х  | х        | х  | х          | х  | х  | х         | х | х | х         | х | х | х         | х | х | х         | х |    |

DONE\_PIPE: 1 se añade un estado de pipeline a DONEIN en el startup

DRIVE\_DONE: 1 se conecta DONE a Vdd SINGLE: Captura del Readback es one-shot

OSCFSEL: selecciona la frecuencia de CCLK en Master Slave

SSCLKSRC: fuente de reloj de la secuencia de startup

LOCK WAIT: DLL que hace esperar al startup hasta que se bloquee

SHUTDOWN: si se realiza Start-Up o Shutdown

DONE CYCLE, LCK CYCLE, GTS CYCLE, GWE CYCLE, GSR CYCLE

fase del startup donde se desactivan estas señales

133

# Método de configuración de las Virtex Registros de configuración

- Registro de control (CTL): controla proceso de configuración.

SBITS: nivel de seguridad (R/W, sólo escritura, ninguno de los dos)

PERSIST: interfaz de configuración permanece después de ésta

GTS-USR\_B: señal de 3-state global

- Registro de máscara del registro de control (MASK): Determina qué bits del COR pueden modificarse

- Registro de chequeo CRC: permite realizar chequeos en la configuración del dispositivo.

# Método de configuración de las Virtex Registros de configuración

Registro de dirección de frame (FAR): guarda la dirección del "frame" sobre el que se va realizar una operación de lectura / escritura de configuración. Esta dirección va incrementándose a medida que se escriben las frames

|                  | Block<br>Type | Major Address<br>(Column Address) | Minor Address<br>(Frame Address) |                   |

|------------------|---------------|-----------------------------------|----------------------------------|-------------------|

| 31 30 29 28 27 2 | 26 25 2       | 24   23 22 21 20   19 18 17       | 16 15 14 13 12 11 10 9           | 8 7 6 5 4 3 2 1 0 |

| 0 0 0 0 0        | х х :         | * * * * * * * * *                 | x x x x x x x x                  | 0 0 0 0 0 0 0 0 0 |

| Туре | Codes |

|------|-------|

| CLB  | 00    |

| RAM  | 01    |

- Registro de datos de entrada frame (FDRI): guarda los datos de configuración que serán escritos en la memoria del dispositivo.

- Registro de datos de salida frame (FDRO): guarda los datos de configuración que son leídos de la memoria del dispositivo.

135

# Método de configuración de las Virtex Registros de configuración

- Registro de longitud de frame (FLR): guarda la longitud de un frame en palabras de 32 bits, en función del tamaño de la Virtex.

- Registro de salida de herencia (LOUT): utilizado para configuraciones daisy-chaining.

- Registro de estado (STAT) : con información de señales de control.

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | DONE | INIT |    |    | MODE | GHIGH B | GSR_B | GWE B | GTS_CFG | IN ERROR |   |   | LOCK | כסכב בסטטם | CENTO |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|------|----|----|------|---------|-------|-------|---------|----------|---|---|------|------------|-------|

| 3 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14   | 13   | 12 | 11 | 10   | 9       | 8     | 7     | 6       | 5        | 4 | 3 | 2    | П          | Л     |

| 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Х    | Х    | Х  | х  | Х    | Х       | Х     | х     | Х       | Х        | х | х | X X  | x :        | ζ.    |

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex, Virtex IX

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. Método de configuración de las Virtex

- Organización, estructura y direccionamiento de configuración

- Registros de configuración

- Modos de configuración: serie maestro / esclavo, paralelo (SelectMAP)

- Proceso de configuración

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

137

# Método de configuración de las Virtex

### Modos de configuración

- Los modos de configuración establecen la manera de cargar el "bitstream" con las operaciones.

- Los pines de configuración pueden ser dedicados o reutilizarse en el diseño después de la reconfiguración.

- Existen 4 modos de configuración básicos:

- Modo serie maestro.

- Modo serie esclavo.

- Modo paralelo (SelectMAP).

- Modo estándar JTAG.

| Configuration Mode         | M2  | M1 | Mo | Pull-ups |

|----------------------------|-----|----|----|----------|

| Master Serial              | 0   | 0  | 0  | No       |

| Slave Serial               | - 1 | 1  | 1  | No       |

| SelectMAP                  | - 1 | 1  | 0  | No       |

| Boundary Scan              | - 1 | 0  | 1  | No       |

| Master Serial (w/pull-ups) | - 1 | 0  | 0  | Yes      |

| Slave Serial (w/pull-ups)  | 0   | 1  | 1  | Yes      |

| SelectMAP (w/pull-ups)     | 0   | 1  | 0  | Yes      |

| Boundary Scan (w/pull-ups) | 0   | 0  | 1  | Yes      |

|                            |     |    |    |          |

# Método de configuración de las Virtex

### Modos de configuración

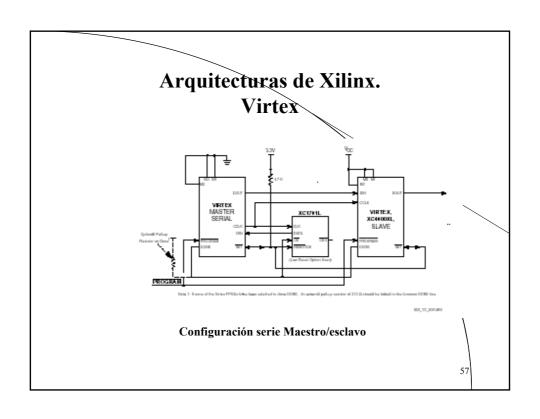

- Configuración serie :

- Se transmite un bit en cada ciclo de reloj (más significativo en primer lugar).

- Imposible reconfiguración parcial ni lectura de memoria.

- Dos modos de configuración:

- Maestro: el dispositivo Virtex genera la señal de reloj.

- Útil para cargar de memorias PROM.

- Esclavo: la señal de reloj se genera externamente.

- Adecuado para la configuración por un microprocesador.

- Modo daisy chain: combinar varias FPGAs en cadena (modos maestro \ esclavo). Cuando un dispositivo es configurado, éste configura al siguiente.

139

### Método de configuración de las Virtex Modos de configuración PROM DATA DIN DOUT C8 VIRTEX VIRTEX. MASTER XC4000X SERIAL Spartan-XL (Low Reset Option Used) Optional SLAVE Pul-up 7 140

# Método de configuración de las Virtex

Modos de configuración

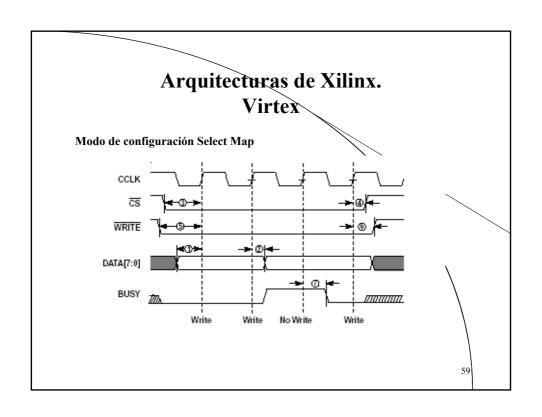

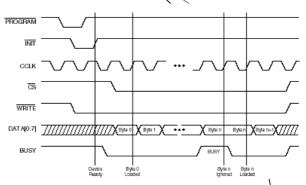

Modo Paralelo: Select Map

- Configuración a través de un bus de 8 bits.

- Se permite reconfiguración parcial y leer de la memoria de configuración

•Es el modo de configuración más adecuado cuando se realiza configuración mediante un microprocesador.

141

# Método de configuración de las Virtex

Modos de configuración

•No está previsto configuración daisy chain, pero si se permite configuración de varios dispositivos a la vez con la misma configuración.

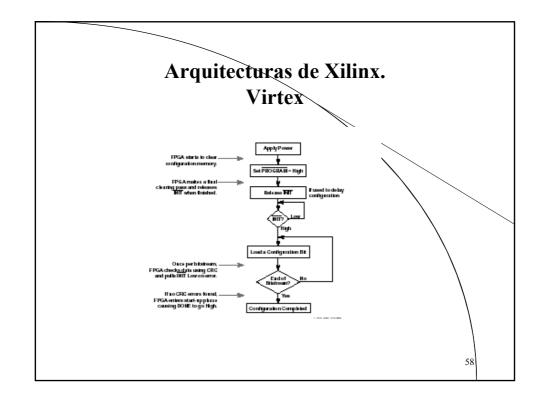

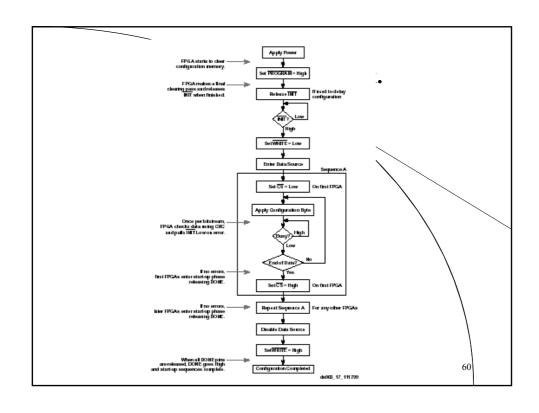

## Método de configuración de las Virtex Proceso de configuración

- Fases para la configuración del dispositivo Virte

- Inicialización de la configuración del dispositivo

- Encendido

- Borrado de memoria

- Carga de los datos de configuración:

- Sincronización

- Selección de opciones y frecuencia de configuración

- Carga de datos

- Chequeo CRC (primer chequeo)

- Carga del último frame

- Finalización del proceso de configuración:

- Secuencia de arranque (startup)

- Chequeo CRC (segundo chequeo)

- Transición al estado operacional

143

### Método de configuración de las Virtex Proceso de configuración

### -Inicialización:

- Encendido (POWER-UP) : los pines de alimentación del dispositivo deben suministrar voltaje mínimo (VCCint a un valor de 2.5V y VCCO 2 1.0 V).

- Borrado de la memoria de configuración: mientras señal PROGRAM se mantenga a 0 se realizará limpiado de memoria.

- Retrasar configuración: la señal INIT se pone en alta cuando se termina de limpiar la memoria de configuración, pero se puede forzar a baja para retrasar proceso.

- Inicio de la carga de los datos de configuración.

#### Método de configuración de las Virtex Proceso de configuración

Carga de los datos de configuración:

- Sincronización: se marca el inicio de las palabras de 32 bits mediante una de palabra de sincronización.

- Selección de opciones y frecuencia de configuración

- Escritura registro CMD RCRC: reseteo del registro de chequeo.

- Escritura registro FLR : establece la longitud de los frames del dispositivo.

- Escritura registros COR y MASK: se indican las opciones de configuración y se escribe en el registro de máscara.

- Escritura registro FAR : se establece dirección inicial del frame a cargar

- Escritura registro CMD WCFG: indicamos operación escritura de datos en la memoria de configuración.

#### Método de configuración de las Virtex Proceso de configuración

- Escritura registro FDRI : escritura de datos.

- En este registro se escriben los datos de configuración.

- El volumen de datos se indica en el campo correspondiente del comando de escritura al registro FDRI.

- Estructura de los datos (para una Virtex XCV100) :

| Data Frame 0 (38 words) | Pad Word |

|-------------------------|----------|

|                         | :        |

| Data Frame n (38 words) | Pad Word |

| Pad Frame (39 words)    | •        |

- Iterar secuencia <escritura registro FAR> <escritura registro FDR> tantas veces como se quiera.

- Chequeo CRC (primer chequeo) antes de cargar último frame.

#### Método de configuración de las Virtex Proceso de configuración

- •Carga del último frame

- •Escritura registro CMD LFRM : escritura último frame.

- Escritura registro FDR : escritura de los datos de configuración del último frame.

- •Finalización del proceso de configuración:

- •Secuencia de arranque

- •Chequeo CRC (segundo chequeo)

- •Transición al estado operacional

#### Método de configuración de las Virtex Proceso de configuración

- •Finalización del proceso de configuración:

- •Secuencia de arranque

- •Escritura registro CMD START :

- inicializamos secuencia de arranque.

- •Escritura registro CTL : seleccionamos opciones de control interno.

- Escritura registro CRC : segundo chequeo CRC (antes de pasar al estado operacional).

- •Chequeo CRC (segundo chequeo)

- •Transición al estado operacional

## Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex, Virtex IN

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. Método de configuración de las Virtex

- Organización, estructura y direccionamiento

- Registros de configuración

- Modos de configuración: serie maestro / esclavo, paralelo (SelèctMAP)

- Proceso de configuración

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

149

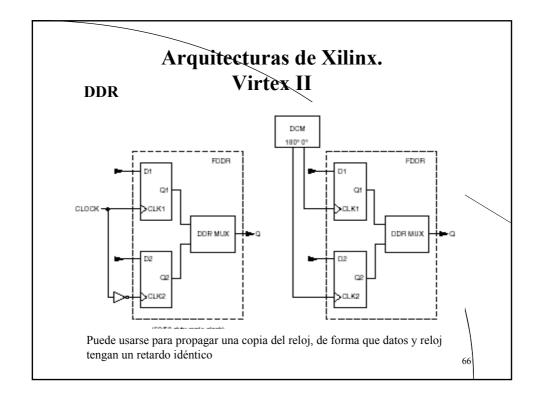

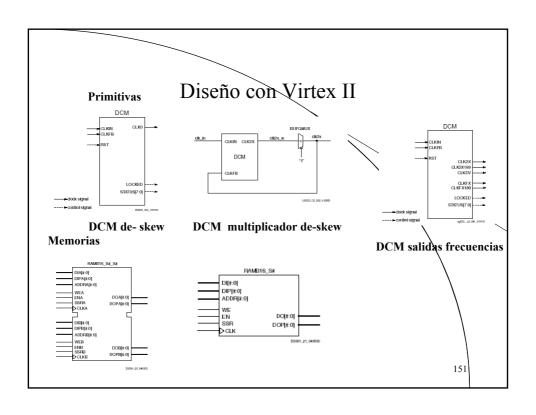

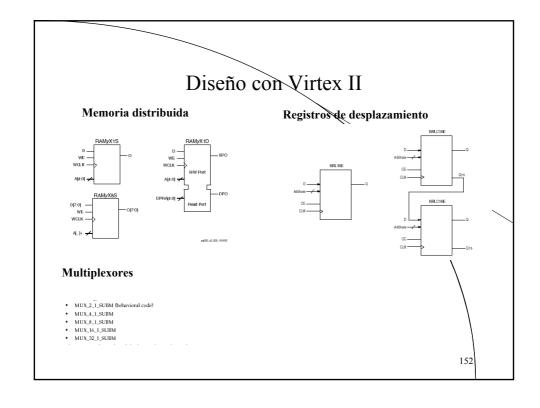

#### Diseño con Virtex II

- Utilización de las redes de reloj globales

- Utilización de los Digital Clock Managers (DCMs)

- Utilización de la Memoria Block SelectRAM<sup>TM</sup>

- Utilización de la Memoria Distribuida SelectRAM

- Utilización de los Look-Up Tables como Shift Registers (SRLXTs)

- Diseño de grandes Multiplexores

- Implementación de Lógica de Suma of Productos (SOP)

- Utilización de los Multiplicadores Empotrados

- Utilización de los recursos de E/S Single-Ended

- Utilización de la Digitally Controlled Impedance (DCI)

- Utilización de los Double-Data-Rate (DDR) I/O

- Utilización LVDS I/O

- Using the CORE Generator System

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex, Virtex II

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. Método de configuración de las Virtex

- Organización, estructura y direccionamiento

- Registros de configuración

- Modos de configuración: serie maestro / esclavo, paralelo (SelectMAP)

- Proceso de configuración

- 5. <u>Diseño con Virtex II</u>

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

#### Diseño con Virtex II

Cuando se genera el mapa de bits es posible utilizar la opción —g compress que permite comprimir las configuraciones mediante la escritura de varias frames idénticas mediante una única escritura

En las Virtex II existe un registro MFWR (Multiple Frame Write) y un nuevo comando MFWR que permite escribir los mismos datos en varias Frames simultáneamente.

- 1. Write WCFG command to CMD register

- 2. Write desired frame to FDRI

- 3. Write to FAR register with the first desired address

- 4. Write MFWR command to CMD register

- 5. Write two dummy words to the MFWR register

- 6. Write to FAR register with the second desired address

- 7. Write two dummy words to MFWR register

- 8. Repeat steps 6 and 7 until the last desired address

155

# Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex, Virtex IX

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. Método de configuración de las Virtex

- Organización, estructura y direccionamiento

- Registros de configuración

- Modos de configuración: serie maestro / esclavo, paralelo (SelèctMAP)

- Proceso de configuración

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

#### Diseño con Virtex II

>Las Virtex II disponen de un desencriptador en el propio chip, que permite que las configuraciones de bitstream no puedan analizarse.

> Existen hasta un total de 6 claves que se pueden almacenar en una RAM dedicada, alimentada por una batería externa.

> El método para encriptar los datos es Data Encryption Standard (DES), que utiliza una única clave, o bien el Triple Data Encryption Algorithm (TDEA), que utiliza 3 claves.

Cada clave tiene 56bits y sirve para encriptar bloques de 64bits cada vez.

Output<sub>encrypted</sub> =

$$E_{K3}(D_{K2}(E_{K1}(I)))$$

. . . .

Output<sub>decrypted</sub> =  $D_{K1}(E_{K2}(D_{K3}(I)))$

>Las claves para encriptar pueden elegirse aleatoriamente por el comando Bitgen, o bien por el usuario.

157

#### Diseño con Virtex II

> Una Virtex puede almacenar hasta 6 claves. Por tanto aceptar bitstream alternativos de dos vendedores IP. La única condición es que las claves deben almacenarse al mismo tiempo.

>Bitgen crea la bitstream encriptada a partir de las claves en la vínea de argumento o bien a partir de un Fichero de claves.

```

# Comment for key file

Key 0 0x9ac28ebeb2d93b;

Key 1 pick;

Key 2 string for my key;

Key 3 0x0000000000000;

Key 4 8774ebJebb4f84;

Keyaeq 0 F;

Keyaeq 1 M;

Keyaeq 2 L;

Keyaeq 3 F;

Keyaeq 4 M;

Keyaeq 5 L;

Keyaeq 5 L;

```

bitgen -g Encrypt:Yes -g Key0: 0x9ac28ebeb2d83b -g Key1:pick -g Key2: string for ny key" -g Key3ox0010000101000 -g Key4:8774eb3eb4f84 -g Keyseq0:F, -g Keyseq1:M, -gKeyseq2:I -g Keyseq3:F -g Keyseq4:M -g Keyseq5:L -g StartCBC:S03f2f655b1b2f82 -g StartKey:0 myinput.ncd

#### Diseño con Virtex II

- >No se pueden utilizar simultáneamente la opción de compresión con la de encriptación.

- > Tampoco se permite el readback ni la reconfiguración parcial (en el registro de control se coloca el nivel de seguridad a 1 o 2).

- Las claves se cargan a través de JTAG mediante la herramienta IMPACT.

- > Una vez programadas las claves, no pueden reprogramarse sin borrar el dispositivo.

- > Una vez programado el dispositivo con las claves correctas, la configuración se realiza normalmente utilizando el bitstream encriptado con cualquier método.

- > También pueden utilizarse bitstream no encriptados.

159

## Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex, Virtex IX

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. Método de configuración de las Virtex

- Organización, estructura y direccionamiento

- Registros de configuración

- Modos de configuración: serie maestro / esclavo, paralelo (SelèctMAP)

- Proceso de configuración

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

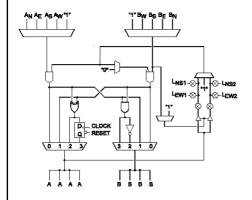

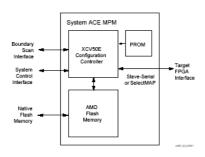

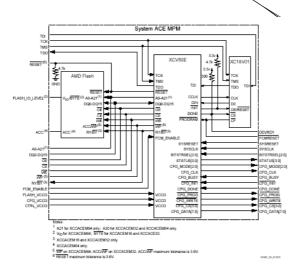

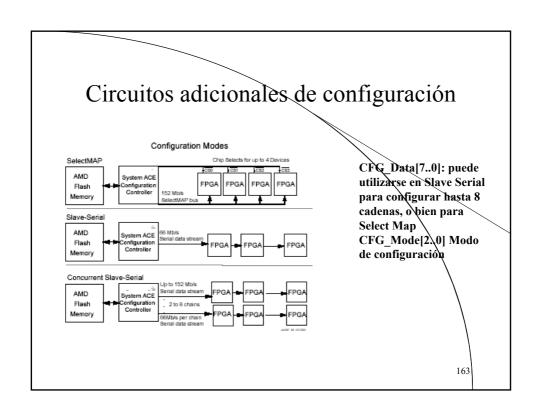

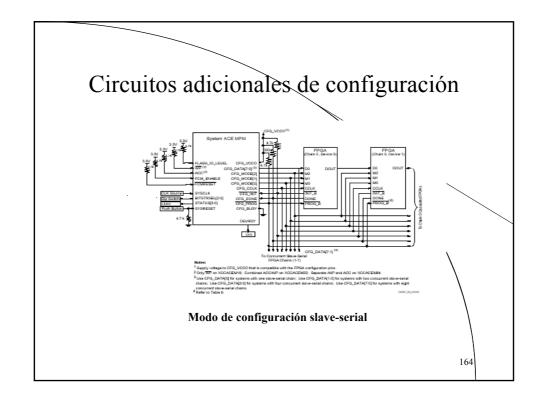

## Circuitos adicionales de configuración

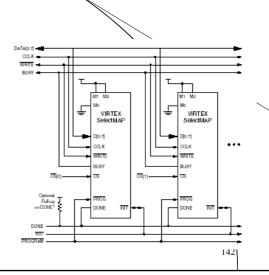

El Sistema ACE Multi-Package Module (MPM) está diseñado para realizar las tareas de configuración en un sistema Multi-FPGA. Está formado por tres bloques:

- 1.- Un controlador, diseñado sobre una Virtex XCV50E

- 2.- Una PROM XC18V01 de configuración de la Virtex atilizada para implementar el controlador

- 3.- Una memoria Flash para cargar las configuraciones de las virtex objetivo

#### **Tiene 4 interfaces:**

- 1. -JTAG interfaz para boundary scan test y programación de la PROM

- 2.- Interfaz de control: reloj, selección, señales de control y estado de configuración

- 3.- Interfaz de memoria Flash

- 4.- Interfaz con las FPGAs via Slaveserial o Select Map

## Circuitos adicionales de configuración

CFG CLK: fuente de reloj CFG CS[3..0] chip enables FCMRESET: fuerza a la XCX50E a reconfigurarse Sysreset: Resetea a lógica de control del MPM para iniciar download BITSTRSEL[2..0] determina la configuración que debe cargarse DEVRDY: conectado al pin DONE de la XCV50E 162

# Circuitos adicionales de configuración TORRES DE CONFIGURA ACE MPM PEDA DE CONFIGURA ACE MPM PEDA

## Circuitos adicionales de configuración

#### Organización de la Memoria Flash

Existe un directorio donde se almacena información sobre cada configuración:

- 1.- Opciones de configuración

- 2.- Dirección inicial de la conf.

- 3.- Longitud de la configuración

Se pueden cargar hasta 8 configuraciones, seleccionadas por BITSTRSEL[2:0].

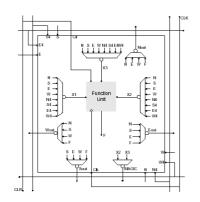

#### Diseño con Virtex II Estos dispositivos incorporan un descompresor, y permiten almacenar diferentes configuraciones en un ratio 2:1. System ACE SC Scan Interface Configuration Controller JTAG Configuration Formatter System Control Interface State Target FPGA SelectMAP Flash Interface I/F Decompressor Flash 167

## Circuitos adicionales de configuración

- La secuencia de configuración es:

- 1.- Se inicial al comenzar la alimentación o al pulsar SYSRESET

- 2.- Se muestrea BITSTRSEL[2:0]

- 3.- Se activa CFG\_PROGRAM para prepara las FPGAs destino

- 3.- Se espera que CFG INIT se active

- 4.- Se busca los datos de configuración a partir de la información del directorio y comienza a enviarse datos

- 5.- Se chequea que DONE se active al final de la configuración

## Circuitos adicionales de configuración

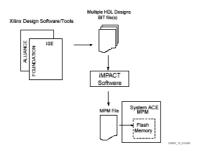

#### Flujo de diseño

Las herramientas de Xilinx permiten generar las distintas configuraciones.

La herramienta IMPACT permite compilar los \*.bit en una única imagen para a una única cadena en modo Slave-Serial o a una única FPGA en modo SelecMap.

También sirve para compilar los distintos conjuntos de datos en una imagen de la Memoria Flash (fichero \*.MPM), donde se guardan también los datos de configuración de cada conjunto de datos

Utilizando el mismo software se programa la memoria Flash

169

## Tema 2. Arquitecturas comerciales de Hw dinámicamente reconfigurable

- 1. Arquitecturas de Xilinx: 6200, Virtex Virtex II

- 2. Arquitecturas de Altera: Flex 6000, Flex 10K

- 3. Arquitecturas de Atmel: AT 6000, AT 40K

- 4. Método de configuración de las Virtex

- 5. Diseño con Virtex II

- Compresión

- Cifrado

- Circuitos adicionales de configuración

- 6. Herramientas para reconfiguración dinámica

- 1. Jbits

- 2. Diseño Modular para reconfiguración parcial

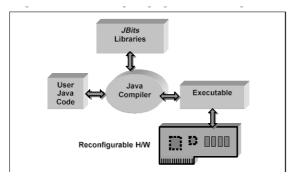

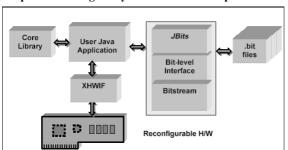

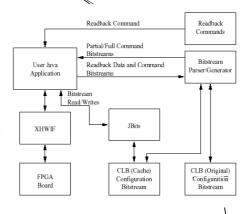

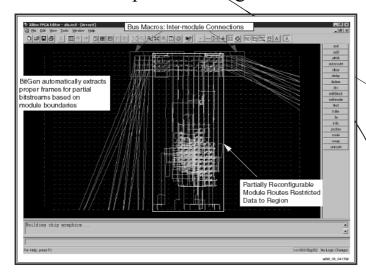

# Herramientas para reconfiguración dinámica JBits

Se trata de un conjunto de clases Java que proporcionar un interfaz (API) para acceder a un mapa de bits de Xilinx para las XC4000 y las Virtex Permite tanto construir circuitos como modificarlos

Es un soporte software para la reconfiguración dinámica de los circuitos. Es muy rápida, permite colocación e interconexionado, y proporciona información física del circuito La biblioteca de clases precompiladas que permite un acceso completo a todas los recursos configurables del dispositivo

El código ejecutable proporciona información de datos y control

171

# Herramientas para reconfiguración dinámica JBits

XHWIF Xilinx standard HardWare Interfaz es un interfaz hardware que permite configurar y realizar readback para una determinada plataforma

La biblioteca de Cores es una colección de clases Java que definen macroceldas parametrizables y que pueden situarse en cualquier lugar (contadores, sumadores, multiplicadores, etc.)

El interfaz Bit-Level proporciona el soporte para todos los dispositivos de una determinada familia

La clase bitstream permite leer y escribir bitstream desde y sobre ficheros, así como manejar datos del readback. No se realizan configuraciones parciales

BoardScope es una herramienta de depuración que proporciona un interfaz gráfico Permite obtener el estado interno del circuito y su configuración mientras el hardware está operativo

173

# Herramientas para reconfiguración dinámica JBits

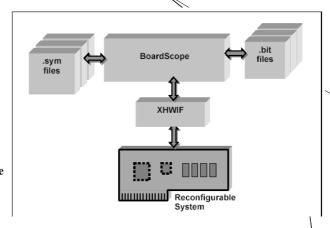

El XHWIF Server es una aplicación que implementa el interfaz XHWIF. Permite que las aplicaciones que trabajan con JBits se comuniquen con las tarjetas de HW Reconfigurable a través de Internet

# Herramientas para reconfiguración dinámica JRoute y JRTR

JBits no soporta reconfiguración parcial, y el interconexionado se realiza de forma manual.

JRoute permite realizar interconexionado con distintos niveles de control.

JRTR permite realizar reconfiguraciones parciales, a través de una cache de configuraciones

175

# Herramientas para reconfiguración dinámica JRTR

| Function        | Description                                                                                                                     |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| parse()         | Parses write and readback bitstream packet commands and overlays them onto the CLB and Block RAM (BRAM) configuration memories. |

| get()           | Generates full or partial CLB and BRAM configuration packet streams.                                                            |

| clearPartial()  | Clears the partial reconfiguration flag and forces a full reconfiguration only on the next get().                               |

| clearFull()     | Clears the partial and full configuration flags and puts the object into an initial state.                                      |

| writeClbCache() | Forces a write of the cache to the original CLB configuration.                                                                  |

| getClbCache()   | Returns a pointer to the CLB configuration stream. This will be used to synch up with the JBits object after parsing.           |

El Parser/Generador se usa para analizar una configuración y generar configuraciones globales o parciales

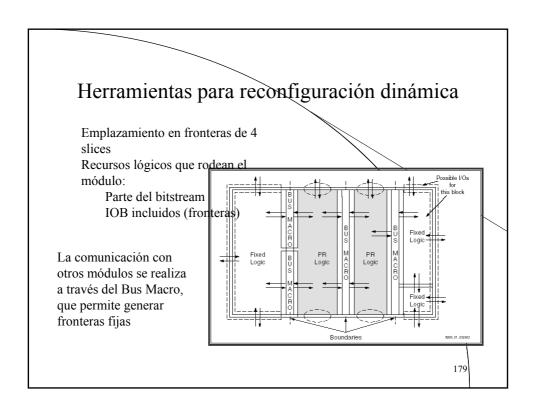

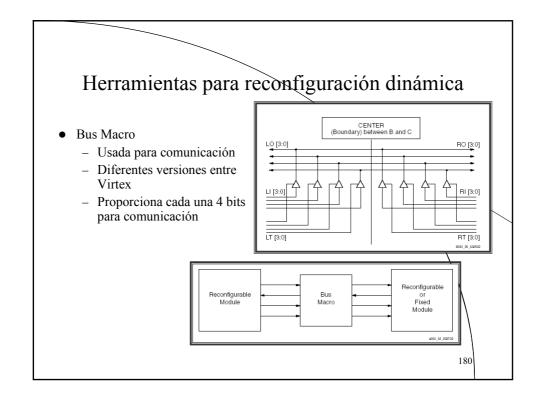

## Herramientas para reconfiguración dinámica

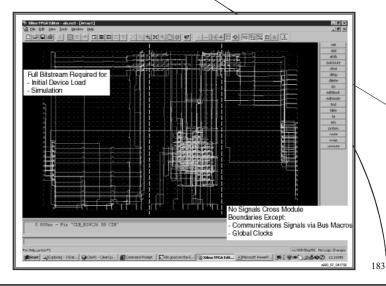

#### • Reconfiguración parcial con Diseño Modular

- Reconfiguración parcial: se trata de reconfigurar ma parte de la FPGA mientras el resto del diseño sigue todavía operativo.

- Estilos:

- Parcial Multicolumna:

- Diseños independientes

- Comunicación entre diseños (Bus Macro)

- Manipulaciones Small-Bit

- Sólo una pequeña parte del diseño se modifica

- Bitstream pequeños (diferentes ordenes de magnitud)

- Politica de reemplazamiento de bitstream

- Cambios

- · Ecuaciones LUT

- · Contenidos RAM

- I/O

- · Otras propiedades

177

#### Herramientas para reconfiguración dinámica

- Características de un modulo reconfigurable:

- Dimensiones

- Altura = Altura dispositivo (FPGA)

- Ancho = Mínimo de 4 slices y múltiplos.

- Responsabilidad programador la comunicación entre los distintos módulos fijos y/o reconfigurables

- Estado elementos almacenamiento se preserva cuando se reconfiguran

Lógica del reloj va separada

Modulo reconfigurable no deben compartir clk, reset...

Se recomienda clk globales

#### Herramientas para reconfiguración dinámica

- Cuando se realiza la colocación y rutado de un diseño hay que especificar:

- Localización de cada módulo, y en particular de todos los bus macros

- Ligaduras de área

- Lógica de alto nivel

- Bus macro

- Ligadura de tiempo globales

181

## Herramientas para reconfiguración dinámica

## Herramientas para reconfiguración dinámica