# FUNDAMENTOS DE ELECTRÓNICA

Examen 1ª Convocatoria. Segundo Parcial. Parte 1 (2016-2017)

Apellidos, Nombre:

| Compañía: Sección AGM: | Grupo CUD: |

|------------------------|------------|

|------------------------|------------|

Este examen consta de tres ejercicios y una cuestión. **Se divide en dos partes que debe presentar por separado.** Esta hoja será grapada a los folios con las soluciones correspondientes. Lea atentamente las siguientes normas:

- Rellene sus datos personales

- Comience cada ejercicio en cara nueva de folio

- Compruebe que tiene todas las cuestiones y ejercicios resueltos

- El examen deberá ser escrito a bolígrafo

- No usar bolígrafo rojo ni Tipp-Ex

- Se puede utilizar calculadora pero debe ser NO programable

- Utilice exclusivamente folios proporcionados por el profesorado

| PARTE 1 |                         |  |         | NOTA |

|---------|-------------------------|--|---------|------|

|         | Ejercicio 1 Ejercicio 2 |  | PARTE 1 |      |

|         | / 4.5                   |  | / 1.5   |      |

### **EJERCICIO 1**

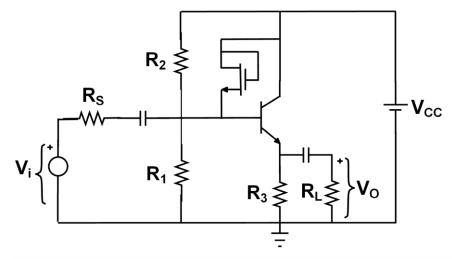

Sea el siguiente circuito basado en un transistor bipolar NPN y un transistor NMOS.

$V_{CC}$  = 12 V,  $R_1$  = 2.4 kΩ,  $R_3$  = 0.9 kΩ,  $R_S$  = 1.2 kΩ,  $R_L$  = 1.8 kΩ,  $V_i$  fuente de tensión alterna W/L = 30, K = 20 μA/V²,  $V_{TH}$  = 1 V,  $\beta$  = 100,  $V_{BE}$  = 0.6 V si la unión BE está en directa

- a) En qué región no puede estar el transistor NMOS. Justifique su respuesta.

- b) Si el transistor NMOS no está en corte, en qué región no puede estar el transistor bipolar. Justifique su respuesta.

- c) Calcular el punto de polarización de ambos transistores y el valor de la resistencia  $R_2$  si la tensión  $V_{GS}$  es igual a 4.2 V. Resolver sin despreciar la corriente de base.

- d) Calcule la ganancia máxima de la etapa. Tome  $V_T = 25.8 \text{ mV}$ .

- e) Calcule la impedancia de entrada de la etapa incluyendo efecto Early para ambos transistores ( $V_A = 15 \text{ V}$ ).

- f) Calcule el valor mínimo de R2 para que el cual el transistor NMOS no cambia de región.

### **EJERCICIO 2**

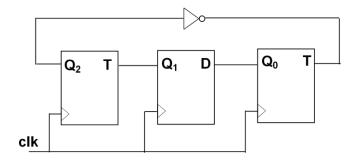

Dado el siguiente circuito secuencial, constituido por biestables flip-flop (dos T y uno D) activados por flanco de subida:

- a) ¿Cuáles son las tablas de transición de estados del biestable D y del biestable T?

- b) ¿En qué instante de tiempo un cambio de estado del biestable T (salida Q<sub>0</sub>), produce un cambio de estado en el biestable D? Justifique su respuesta.

- c) Indique los ciclos que se generan en dicho circuito secuencial.

# FUNDAMENTOS DE ELECTRÓNICA

Examen 1ª Convocatoria. Segundo Parcial. Parte 2 (2016-2017)

Apellidos, Nombre:

| Compañía: | Sección AGM: | Grupo CUD: |

|-----------|--------------|------------|

|-----------|--------------|------------|

Este examen consta de tres ejercicios y una cuestión. **Se divide en dos partes que debe presentar por separado.** Esta hoja será grapada a los folios con las soluciones correspondientes. Lea atentamente las siguientes normas:

- Rellene sus datos personales

- Comience cada ejercicio en cara nueva de folio

- Compruebe que tiene todas las cuestiones y ejercicios resueltos

- El examen deberá ser escrito a bolígrafo

- No usar bolígrafo rojo ni Tipp-Ex

- Se puede utilizar calculadora pero debe ser NO programable

- Utilice exclusivamente folios proporcionados por el profesorado

| PARTE 2 |             |            | NOTA |         |

|---------|-------------|------------|------|---------|

|         | Ejercicio 3 | Cuestión 1 |      | PARTE 2 |

|         | /3          |            | /1   |         |

### **EJERCICIO 3**

Para el circuito de la figura, basado en un AO y un transistor NMOS, en el cual existe realimentación negativa si el transistor está conduciendo, calcule:

$$R_{1} = 0.5 \text{ k}\Omega, R_{L} = 3 \text{ k}\Omega$$

$$V_{CC} = 9 \text{ V}, V_{EE} = -9 \text{ V}, I_{0,max} = 40 \text{ mA}$$

$$V_{TH} = 1 \text{ V}, W/L = 40, K = 20 \text{ } \mu\text{A}/\text{V}^{2}$$

$$V_{i}$$

- a) La tensión de entrada V<sub>i</sub> y salida V<sub>o</sub> si por el transistor fluye una corriente 4.9 mA.

- b) La tensión de entrada  $V_i$  mínima para que el transistor conduzca. El valor de la tensión de salida  $V_o$  en ese caso.

- c) El valor de la tensión de salida V<sub>o</sub> si la tensión de entrada es inferior a la calculada en el apartado b.

- d) La tensión de entrada  $V_i$  máxima para no sobrepasar la tensión de salida límite definida por el AO.

- e) El valor de la tensión de salida V<sub>o</sub> si la tensión de entrada es superior a la calculada en el apartado d.

- f) La resistencia  $R_L$  mínima para no sobrepasar la corriente máxima de salida del AO en el rango de tensión de entrada  $V_i$  definido entre los apartados b y d.

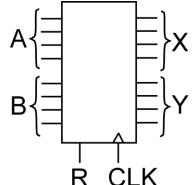

## **CUESTIÓN 1**

Sea un sistema digital con entradas A y B y salidas X e Y, todas ellas compuestas por cuatros bits. Una de las salidas es combinacional y la otra es secuencial, para la cual el sistema dispone de reloj (CLK) y reset (R). Se ha anotado el valor de las entradas y salidas en distintos momentos, que se recogen en la siguiente tabla. Deducir que salida es combinacional y que salida es secuencial. Justifique su respuesta.

| A    | В    | X    | Y    |

|------|------|------|------|

| 1000 | 0001 | 1001 | 0101 |

| 1101 | 0001 | 1100 | 0111 |

| 1101 | 0110 | 1011 | 0000 |

| 1101 | 0110 | 1011 | 1001 |

| 0011 | 1010 | 1001 | 1100 |

| 0011 | 1101 | 1110 | 0110 |

Describa brevemente ejemplos de dos sistemas digitales combinacionales y dos secuenciales.

Nota: Una puerta lógica o un biestable no se consideran sistemas digitales para esta cuestión.