# **Sistemas Digitales Secuenciales**

## Ejercicio 1:

Siendo X un número binario de tres bits, diseñar la entrada lógica necesaria para poner a '1' un biestable J-K si X tiene un número impar de unos y ponerle a '0' en caso contrario.

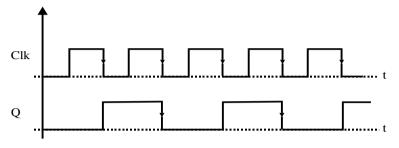

#### Ejercicio 2:

Se dispone del siguiente cronograma. Identifíquese que tipo de biestable se ha empleado y explique por qué.

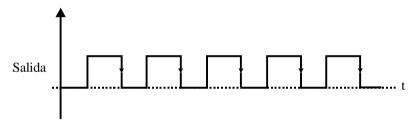

## Ejercicio 3:

Se desea un circuito secuencial que tenga como señal de salida la representada en la figura. Diséñese dicho circuito digital a base de biestables y puertas lógicas, sabiendo que se trata de un divisor por 4.

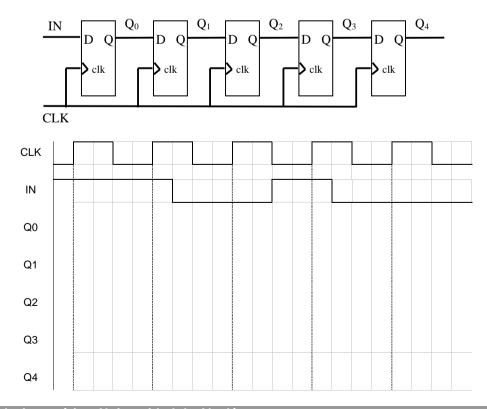

#### Eercicio 4:

Obtener los estados del registro de 5 bits mostrado (inicialmente 0000), para las señales de reloj (CLK) y entrada de datos (IN) indicadas

## Ejercicios Tema 4: Sistemas secuenciales Fundamentos de Tecnología de Computadores

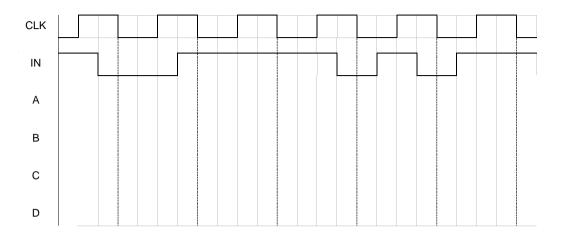

## Ejercicio 5:

Hacer un diagrama de tiempos de un registro de desplazamiento con entrada serie y 4 salidas paralelas (A-B-C-D), suponiendo que está compuesto de biestables tipo D con entrada de reloj activa en flanco de bajada y que la entrada serie aplicada es la mostrada a continuación. ¿Qué dato se obtendría tras 6 ciclos de reloj?

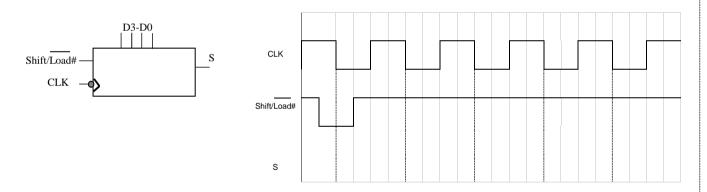

## Ejercicio 6:

Determinar la forma de onda de la salida de datos de un registro entrada paralela / salida serie para las señales de entrada mostradas en la figura y suponiendo que las entradas D3-D0 tienen los datos 1010.

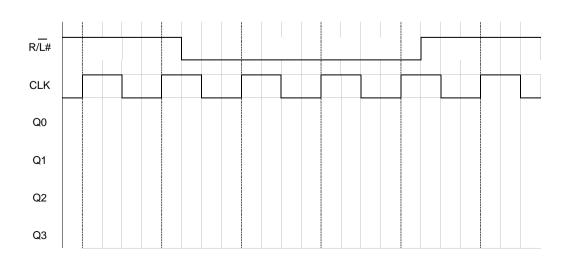

## Ejercicio 7:

Determinar el estado en cada pulso de reloj de un registro de desplazamiento bidireccional de 4 bits en el que la entrada de datos está en nivel BAJO, si se aplica la señal de control RIGHT/LEFT# indicada. Suponer que el estado inicial del registro es Q0-Q3 = 1101 y que la sincronización es con el flanco de subida del reloj.

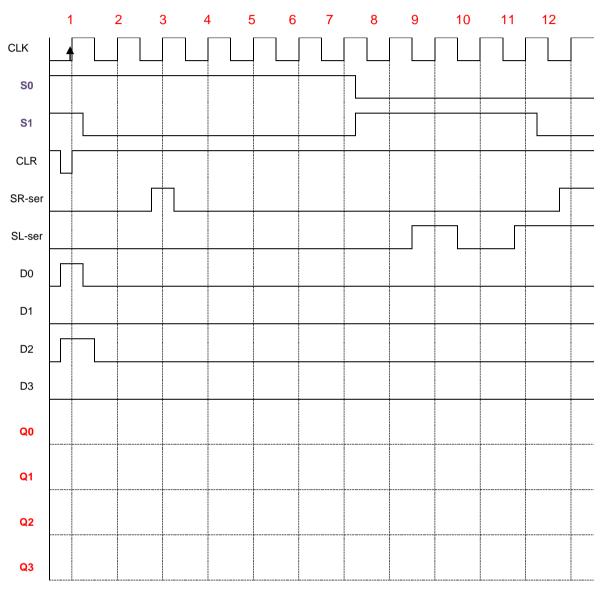

## Ejercicio 8:

Determinar el estado en cada pulso de reloj de un registro de desplazamiento universal bidireccional de 4 bits en el que se aplican las señales de entrada y de control mostradas (sincronización con flanco de subida del reloj). Suponer que solo CLR es asíncrona y que las señales de control S0-S1 codifican el siguiente comportamiento: S0=S1=1: Carga paralela (D0-D3); S0=S1=0 no hay cambios; S0=0 y S1=1 desplazamiento a la izquierda y S0=1 y S1=0 desplazamiento a la derecha. SR-ser y SL-ser son las entradas de datos serie derecha e izquierda respectivamente.

#### Ejercicio 9:

Diseñar un contador síncrono ascendente de módulo 4 con biestables D

## Ejercicio 10:

Diseñar un contador síncrono ascendente/descendente de 0 a 7 con biestables J-K.

#### Ejercicio 11:

Diseñar un contador síncrono con biestables D que cuente de 5 a 0 (descendente). También se requiere que si el contador está en algún estado distinto del 0 al 5, vuelva a 0 en el siguiente pulso de reloj.

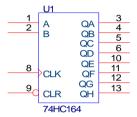

#### Ejercicio 12:

Se dispone de dos conversores serie-paralelo de 8 bits como el de la figura. Diseñe un conversor serie-paralelo de 16 bits.

#### Ejercicio 13:

Diseñe un circuito con flip-flops JK que detecte en la entrada Y la secuencia "101" configurando la salida Z a 1.

#### Ejercicio 14:

Diseñe un circuito con flip-flops D que detecte en la entrada Y cuatro "1" consecutivos ajustando la salida Z a 1.

#### Ejercicio 15:

Diseñe un circuito con una entrada Y y una salida Z que debe tomar el valor "1" siempre que los dos últimos bits en la entrada sean iguales, y "0" en caso contrario.