## **Circuitos Combinacionales**

Fundamentos de Computadores Escuela Politécnica Superior. U.A.M

## Índice de la Unidad 2

#### U2. Circuitos combinacionales

- **U2.1.** Implementación de la lógica combinacional. Funciones lógicas.

- U2.2. Circuitos combinacionales básicos

- U2.2.1. Decodificador.

- U2.2.2. Multiplexor y Demultiplexor.

- U2.2.3. Codificador de prioridad.

- U2.2.4. Conversor de código.

- U2.2.5. Comparador de bits.

- **U2.3**. Uso de decodificadores y multiplexores como generadores de funciones

## Circuito combinacional

- Circuito sin memoria, las salidas son función de una o varias variables de entrada

- Para una misma combinación de variables a la entrada siempre se obtiene (tras un cierto retraso) la misma combinación de variables a la salida

- Representar la tabla de verdad de la función

- Simplificar la función a su expresión más sencilla (Diagrama de Karnaugh).

- Construir el circuito combinacional con el número menor de puertas.

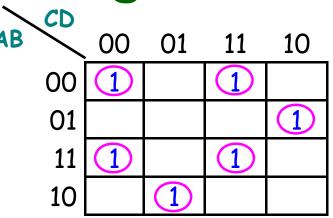

**Ejemplo1**: Sea un circuito que tiene 4 entradas que representan un número binario (ABCD). El circuito dispone de una salida  $Z_1$  que debe activarse ( $Z_1$ =1) cuando el número binario sea múltiplo de 3, y una salida  $Z_2$  que debe activarse cuando el número binario sea múltiplo de 2.

## Ejemplo1:

| N°                                             | A                               | В                          | С                     | D                                                   | Z <sub>1</sub>        | Z <sub>2</sub>        |

|------------------------------------------------|---------------------------------|----------------------------|-----------------------|-----------------------------------------------------|-----------------------|-----------------------|

| 0                                              | 0                               | 0                          | 0                     | 0                                                   | 1                     | 1                     |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>1<br>0 | 1                                                   | 0                     | 1<br>0<br>1<br>0<br>1 |

| 2                                              | 0                               | 0                          | 1                     | 0                                                   | 0<br>0<br>1<br>0      | 1                     |

| 3                                              | 0                               | 0                          | 1                     | 1                                                   | 1                     | 0                     |

| 4                                              | 0                               | 1                          | 0                     | 0                                                   | 0                     | 1                     |

| 5                                              | 0                               |                            | 0                     | 1                                                   |                       | 0                     |

| 6                                              | 0                               | 1<br>1<br>0<br>0           | 0<br>1<br>1<br>0<br>0 | 0                                                   | 0<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0 |

| 7                                              | 0                               | 1                          | 1                     | 1                                                   | 0                     | 0                     |

| 8                                              | 1                               | 0                          | 0                     | 0                                                   | 0                     | 1                     |

| 9                                              | 1                               | 0                          | 0                     | 1                                                   | 1                     | 0                     |

| 10                                             | 1                               | 0                          | 1                     | 0                                                   | 0                     | 1                     |

| 11                                             | 1                               | 0<br>1                     | 1                     | 1                                                   | 0                     |                       |

| 12                                             | 1                               | 1                          | 0                     | 0                                                   | 1                     | 1                     |

| 13                                             | 1                               | 1                          | 1<br>0<br>0<br>1      | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | 0<br>1<br>0           | 0<br>1<br>0<br>1<br>0 |

| 14                                             | 1                               | 1                          | 1                     |                                                     | 0                     | 1                     |

| 15                                             | 1                               | 1                          | 1                     | 1                                                   | 1                     | 0                     |

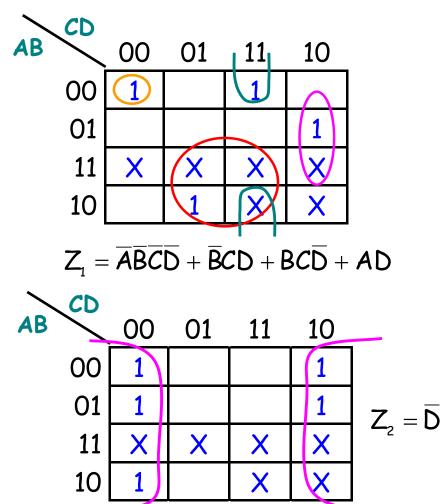

$$Z_{1} = \overline{A}\overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}CD + \overline{A}BC\overline{D} + ABC\overline{D} + ABCD + A\overline{B}\overline{C}D$$

$$Z_2 = \overline{D}$$

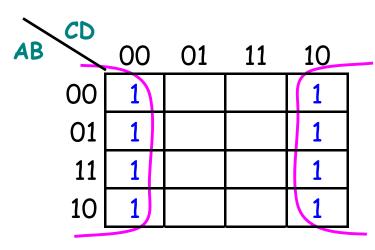

- Funciones incompletamente especificadas

- Funciones que no tienen definidos todos sus estados.

- Los estados no definidos se representan como "X" a la salida.

- A la hora de resolver la tabla de Karnaugh las "X" se toman como 0 o 1 según convenga.

- Funciones incompletamente especificadas

- Ejemplo2: Ejemplo1 pero definiendo sólo de 0 a 9

| N°                                                                                 | A                                              | В                                              | C                                                             | D                                                        | $Z_1$                                                    | Z <sub>2</sub>                                      |

|------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|

| 0                                                                                  | 0                                              | 0                                              |                                                               | 0                                                        | 1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>1<br>X<br>X<br>X | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>X<br>X<br>X |

| 1                                                                                  | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 0                                              | 0                                                             | 1                                                        | 0                                                        | 0                                                   |

| 2                                                                                  | 0                                              | 0                                              | 1                                                             | 0                                                        | 0                                                        | 1                                                   |

| 3                                                                                  | 0                                              | 0                                              | 1                                                             | 1                                                        | 1                                                        | 0                                                   |

| 4                                                                                  | 0                                              | 1                                              | 0                                                             | 0                                                        | 0                                                        | 1                                                   |

| 5                                                                                  | 0                                              | 1                                              | 0                                                             | 1                                                        | 0                                                        | 0                                                   |

| 6                                                                                  | 0                                              | 1                                              | 1                                                             | 0                                                        | 1                                                        | 1                                                   |

| 7                                                                                  | 0                                              | 1                                              | 1                                                             | 1                                                        | 0                                                        | 0                                                   |

| 8                                                                                  | 1                                              | 0                                              | 0                                                             | 0                                                        | 0                                                        | 1                                                   |

| 9                                                                                  | 1                                              | 0                                              | 0                                                             | 1                                                        | 1                                                        | 0                                                   |

| 10                                                                                 | 1                                              | 0                                              | 1                                                             | 0                                                        | X                                                        | X                                                   |

| 11                                                                                 | 1                                              | 0                                              | 1                                                             | 1                                                        | X                                                        | X                                                   |

| 12                                                                                 | 1                                              | 1                                              | 0                                                             | 0                                                        | X                                                        | X                                                   |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | 1                                              | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | X                                                        | X                                                   |

| 14                                                                                 | 1                                              |                                                | 1                                                             | 0                                                        | X                                                        | X                                                   |

| 15                                                                                 | 1                                              | 1                                              | 1                                                             | 1                                                        | X                                                        | X                                                   |

## Circuitos combinacionales básicos

- Decodificador (n-2<sup>n</sup>): n entradas y 2<sup>n</sup> salidas (sólo una activa).

- Codificador (2<sup>n</sup>-n): n entradas (una o varias activas) y lg<sub>2</sub>n salidas.

- Multiplexor (n-1): n entradas, 1 salida y lg<sub>2</sub>n señales de control.

- Demultiplexor (1-n): 1 entrada, n salidas y lg<sub>2</sub>n señales de control.

- Conversor de código (n-m): n entradas y m salidas, sin relación entre ellas.

- Otros C. combinacionales:

- Comparadores

- Semisumadores y Sumadores

- Circuito combinacional con n entradas y 2<sup>n</sup> salidas

- Activa una única línea de salida para cada combinación de las líneas de entrada

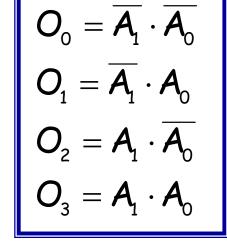

- Decodificador 2-4. 2 entradas y  $2^2 = 4$  salidas

- Tabla de la verdad y ecuaciones:

| $A_1$ | $A_0$ | O <sub>3</sub> | O <sub>2</sub> | $O_1$ | <i>O</i> <sub>0</sub> |

|-------|-------|----------------|----------------|-------|-----------------------|

| 0     | 0     | 0              | 0              | 0     | 1                     |

| 0     | 1     | 0              | 0              | 1     | 0                     |

| 1     | 0     | 0              | 1              | 0     | 0                     |

| 1     | 1     | 1              | 0              | 0     | 0                     |

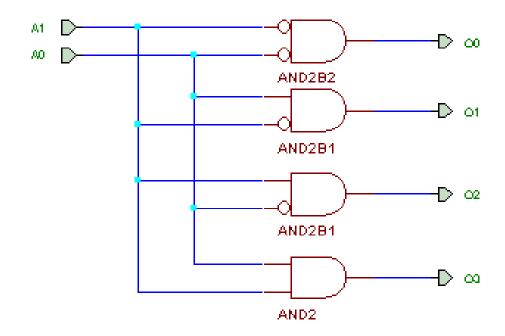

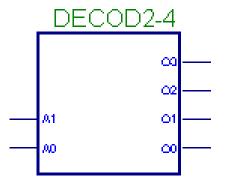

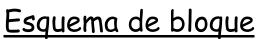

• Decodificador 2-4. Circuito lógico:

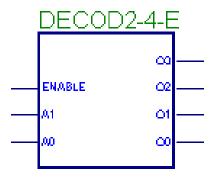

#### Circuito esquemático

#### Esquema de bloque

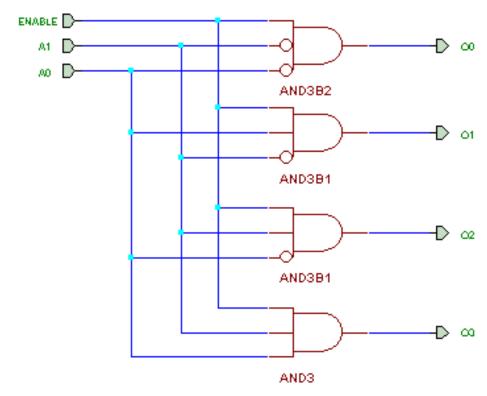

- Decodificador 2-4 con entrada de habilitación (Enable)

- Enable activado: El decodificador funciona normalmente

- Enable desactivado: Ninguna salida activa. Circuito "inhabilitado"

- Tabla de la verdad y ecuaciones:

| Е | $A_1$ | $A_0$ | O <sub>3</sub> | O <sub>2</sub> | $O_1$ | <i>O</i> <sub>0</sub> |

|---|-------|-------|----------------|----------------|-------|-----------------------|

| 0 | 0     | 0     | 0              | 0              | 0     | 0                     |

| 0 | 0     | 1     | 0              | 0              | 0     | 0                     |

| 0 | 1     | 0     | 0              | 0              | 0     | 0                     |

| 0 | 1     | 1     | 0              | 0              | 0     | 0                     |

| 1 | 0     | 0     | 0              | 0              | 0     | 1                     |

| 1 | 0     | 1     | 0              | 0              | 1     | 0                     |

| 1 | 1     | 0     | 0              | 1              | 0     | 0                     |

| 1 | 1     | 1     | 1              | 0              | 0     | 0                     |

$$O_0 = \mathbf{E} \cdot \overline{A_1} \cdot \overline{A_0}$$

$$O_1 = \mathbf{E} \cdot \overline{A_1} \cdot A_0$$

$$O_2 = \mathbf{E} \cdot A_1 \cdot \overline{A_0}$$

$$O_3 = \mathbf{E} \cdot A_1 \cdot A_0$$

• Decodificador 2-4 con habilitación. Circuito lógico:

#### Circuito esquemático

#### Esquema de bloque

• Decodificador 3-8. 3 entradas y  $2^3 = 8$  salidas

Tabla de la verdad y ecuaciones

| A <sub>2</sub> | $A_1$ | $A_0$ | O <sub>7</sub> | O <sub>6</sub> | O <sub>5</sub> | O <sub>4</sub> | O <sub>3</sub> | O <sub>2</sub> | $O_1$ | <i>O</i> <sub>0</sub> |

|----------------|-------|-------|----------------|----------------|----------------|----------------|----------------|----------------|-------|-----------------------|

| 0              | 0     | 0     | 0              | 0              | 0              | 0              | 0              | 0              | 0     | 1                     |

| 0              | 0     | 1     | 0              | 0              | 0              | 0              | 0              | 0              | 1     | 0                     |

| 0              | 1     | 0     | 0              | 0              | 0              | 0              | 0              | 1              | 0     | 0                     |

| 0              | 1     | 1     | 0              | 0              | 0              | 0              | 1              | 0              | 0     | 0                     |

| 1              | 0     | 0     | 0              | 0              | 0              | 1              | 0              | 0              | 0     | 0                     |

| 1              | 0     | 1     | 0              | 0              | 1              | 0              | 0              | 0              | 0     | 0                     |

| 1              | 1     | 0     | 0              | 1              | 0              | 0              | 0              | 0              | 0     | 0                     |

| 1              | 1     | 1     | 1              | 0              | 0              | 0              | 0              | 0              | 0     | 0                     |

$$O_{0} = \mathbf{m}_{0} = \overline{\mathbf{A}_{2}} \cdot \overline{\mathbf{A}_{1}} \cdot \overline{\mathbf{A}_{0}}$$

$$O_{1} = \mathbf{m}_{1} = \overline{\mathbf{A}_{2}} \cdot \overline{\mathbf{A}_{1}} \cdot \overline{\mathbf{A}_{0}}$$

$$O_{2} = \mathbf{m}_{2} = \overline{\mathbf{A}_{2}} \cdot \overline{\mathbf{A}_{1}} \cdot \overline{\mathbf{A}_{0}}$$

$$O_{3} = \mathbf{m}_{3} = \overline{\mathbf{A}_{2}} \cdot \overline{\mathbf{A}_{1}} \cdot \overline{\mathbf{A}_{0}}$$

$$\vdots$$

$$O_{7} = \mathbf{m}_{7} = \overline{\mathbf{A}_{2}} \cdot \overline{\mathbf{A}_{1}} \cdot \overline{\mathbf{A}_{0}}$$

- Circuito combinacional con n entradas y log<sub>2</sub>n salidas

- Codificador Elemental: Para una única línea de entrada activa, codifica a la salida un código que la identifica (número de la entrada).

- Codificador de Prioridad: Dadas varias líneas de entrada activas, codifica a la salida un código (número de la entrada), que identifica a la más prioritaria.

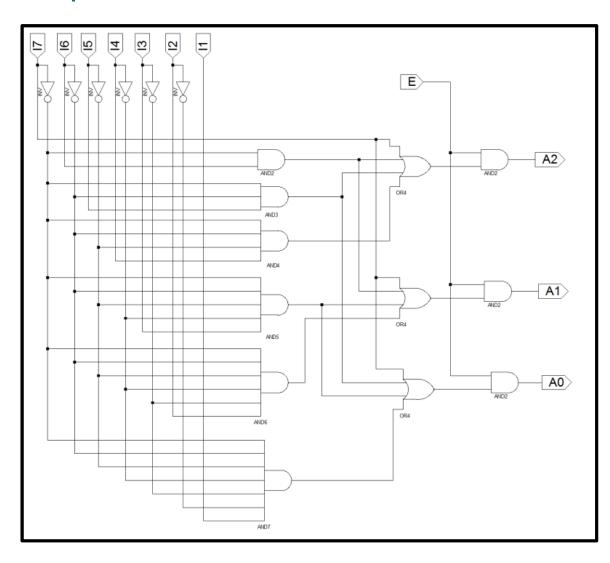

- Codificador de prioridad 8-3 con Enable

- Entre varias entradas activas, se asigna la mayor prioridad a la entrada con índice más alto.

#### Tabla de la verdad

| E | $I_7$ | $I_6$ | $I_5$ | $I_4$ | $I_3$ | $I_2$ | $I_1$ | Io | A <sub>2</sub> | $A_1$ | $A_0$ |

|---|-------|-------|-------|-------|-------|-------|-------|----|----------------|-------|-------|

| 0 | X     | X     | X     | X     | X     | X     | X     | X  | 0              | 0     | 0     |

| 1 | 1     | X     | X     | X     | X     | X     | X     | X  | 1              | 1     | 1     |

| 1 | 0     | 1     | X     | X     | X     | X     | X     | X  | 1              | 1     | 0     |

| 1 | 0     | 0     | 1     | X     | X     | X     | X     | X  | 1              | 0     | 1     |

| 1 | 0     | 0     | 0     | 1     | X     | X     | X     | X  | 1              | 0     | 0     |

| 1 | 0     | 0     | 0     | 0     | 1     | X     | X     | X  | 0              | 1     | 1     |

| 1 | 0     | 0     | 0     | 0     | 0     | 1     | X     | X  | 0              | 1     | 0     |

| 1 | 0     | 0     | 0     | 0     | 0     | 0     | 1     | X  | 0              | 0     | 1     |

| 1 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1  | 0              | 0     | 0     |

| 1 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0  | 0              | 0     | 0     |

Codificador de prioridad 8-3 con Enable

#### **Ecuaciones:**

$$A_{0} = (I_{7} + \overline{I_{7}} \overline{I_{6}} I_{5} + \overline{I_{7}} \overline{I_{6}} \overline{I_{5}} \overline{I_{4}} I_{3} + \overline{I_{7}} \overline{I_{6}} \overline{I_{5}} \overline{I_{4}} I_{3} I_{2} I_{1}) E$$

$$A_{1} = (I_{7} + \overline{I_{7}} I_{6} + \overline{I_{7}} \overline{I_{6}} \overline{I_{5}} \overline{I_{4}} I_{3} + \overline{I_{7}} \overline{I_{6}} \overline{I_{5}} \overline{I_{4}} I_{3} I_{2}) E$$

$$A_{2} = (I_{7} + \overline{I_{7}} I_{6} + \overline{I_{7}} \overline{I_{6}} I_{5} + \overline{I_{7}} \overline{I_{6}} \overline{I_{5}} I_{4}) E$$

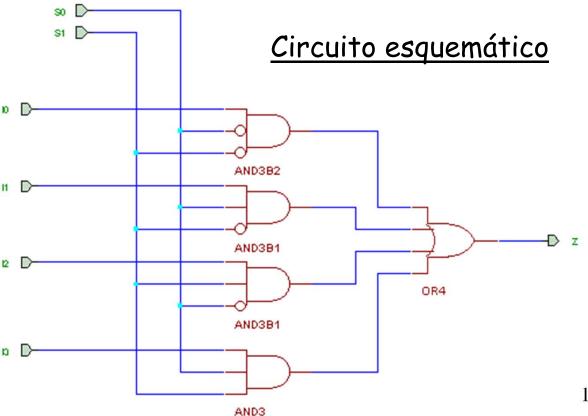

Codificador de prioridad 8-3 con Enable

Circuito:

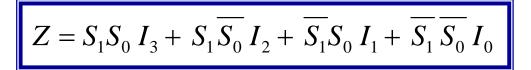

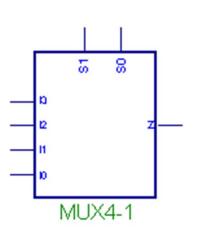

- Realiza la transmisión de datos desde una entrada seleccionable hacia una salida única

- Se caracteriza por tener n líneas de control que seleccionan (multiplexan) una de las 2<sup>n</sup> líneas de entrada y la transmiten a la salida

- Cada combinación de las líneas de control activa una puerta

- Hay dos tipos de entradas:

- Entradas de datos

- Entradas de control

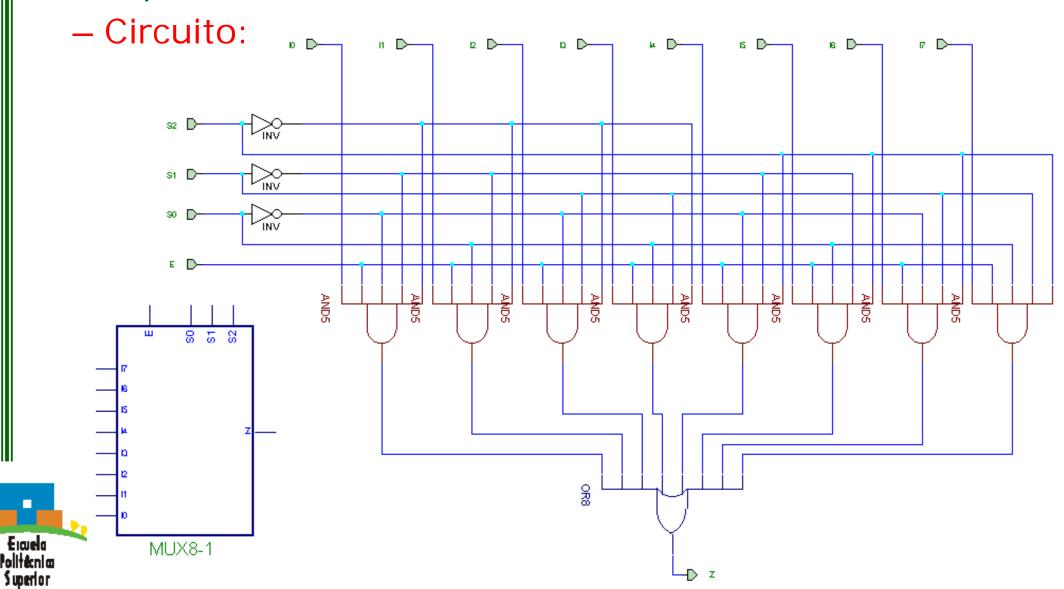

Multiplexor 4-1. 4 entradas (datos), 2 entradas (control) y 1 salida

Tabla de la verdad, ecuación y circuito:

| <b>S</b> <sub>1</sub> | <b>S</b> <sub>0</sub> | Salida (Z) |

|-----------------------|-----------------------|------------|

| 0                     | 0                     | Io         |

| 0                     | 1                     | $I_1$      |

| 1                     | 0                     | $I_2$      |

| 1                     | 1                     | $I_3$      |

Multiplexor 8-1 con entrada de habilitación. 8 entradas (datos), 4 entradas (control) y 1 salida

Tabla de la verdad y ecuación

| Е | <b>S</b> <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Z     |

|---|-----------------------|----------------|----------------|-------|

| 0 | X                     | X              | X              | 0     |

| 1 | 0                     | 0              | 0              | Io    |

| 1 | 0                     | 0              | 1              | $I_1$ |

| 1 | 0                     | 1              | 0              | $I_2$ |

| 1 | 0                     | 1              | 1              | $I_3$ |

| 1 | 1                     | 0              | 0              | $I_4$ |

| 1 | 1                     | 0              | 1              | $I_5$ |

| 1 | 1                     | 1              | 0              | $I_6$ |

| 1 | 1                     | 1              | 1              | $I_7$ |

$$Z = (S_2 S_1 S_0 I_7 + S_2 S_1 \overline{S_0} I_6 + S_2 \overline{S_1} S_0 I_5 + S_2 \overline{S_1} \overline{S_0} I_4 + \overline{S_2} S_1 S_0 I_3 + \overline{S_2} S_1 \overline{S_0} I_2 + \overline{S_2} \overline{S_1} S_0 I_1 + \overline{S_2} \overline{S_1} \overline{S_0} I_0) E$$

Multiplexor 8-1 con entrada de habilitación

# Demultiplexor

- Realizan la función inversa del multiplexor

- Puede seleccionarse la transmisión de un dato desde una única línea de entrada hacia una de las posibles líneas de salida

- Utilizando n líneas de control, transmite (demultiplexa) la información de su única línea de entrada por cualquiera de sus 2<sup>n</sup> líneas de salida

- Es lo mismo que un decodificador con enable, siendo la línea de datos equivalente al enable

# Demultiplexor

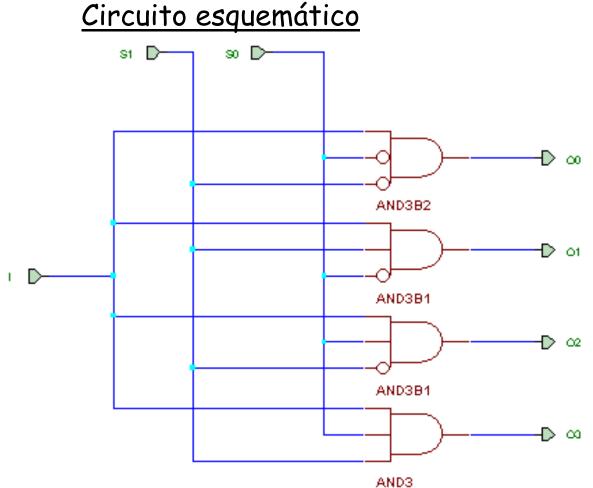

- Demultiplexor 1-4. 1 entrada (dato), 2 entradas (control) y 4 salidas

- Tabla de la verdad y ecuaciones:

| S <sub>1</sub> | <b>S</b> <sub>0</sub> | <i>O</i> <sub>3</sub> | O <sub>2</sub> | $O_1$ | <i>O</i> <sub>0</sub> |

|----------------|-----------------------|-----------------------|----------------|-------|-----------------------|

| 0              | 0                     | 0                     | 0              | 0     | I                     |

| 0              | 1                     | 0                     | 0              | I     | 0                     |

| 1              | 0                     | 0                     | I              | 0     | 0                     |

| 1              | 1                     | I                     | 0              | 0     | 0                     |

$$O_{0} = \overline{S_{1}} \cdot \overline{S_{0}} \cdot I$$

$$O_{1} = \overline{S_{1}} \cdot S_{0} \cdot I$$

$$O_{2} = S_{1} \cdot \overline{S_{0}} \cdot I$$

$$O_{3} = S_{1} \cdot S_{0} \cdot I$$

# Demultiplexor

• Demultiplexor 1-4. Circuito:

- Dada una palabra de n bits a la entrada se convierte o traduce a otra palabra de m bits a la salida.

- No existe una relación entre el número de líneas de entrada y de salida.

- Ambas palabras representan la misma información en distintos códigos.

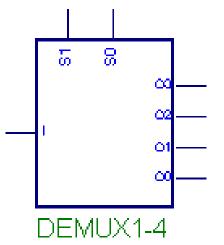

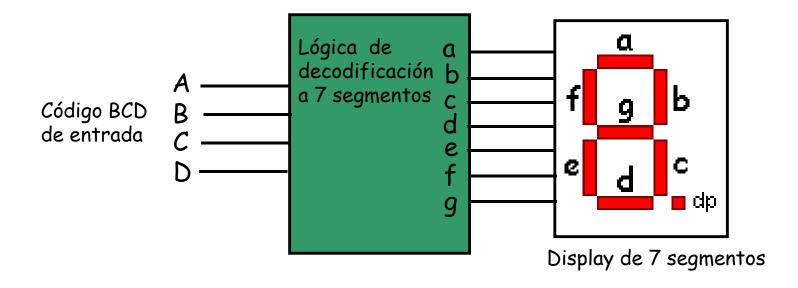

- Conversor BCD a 7 segmentos

- Acepta código BCD (0..9) en sus 4 entradas y proporciona 7 salidas capaces de excitar un display de 7 segmentos que indican el dígito decimal de la entrada.

- Diagrama de bloques de la lógica:

- Conversor BCD a 7 segmentos

- Segmentos activados para cada dígito decimal

| Dígito | Segmentos activados |

|--------|---------------------|

| 0      | a,b,c,d,e,f         |

| 1      | b,c                 |

| 2      | a,b,d,e,g           |

| 3      | a,b,c,d,g           |

| 4      | b,c,f,g             |

| 5      | a,c,d,f,g           |

| 6      | a,c,d,e,f,g         |

| 7      | a,b,c               |

| 8      | a,b,c,d,e,f,g       |

| 9      | a,b,c,d,f,g         |

- Conversor BCD a 7 segmentos

- Tabla de verdad:

| Digito  | Entradas |   |   |   |   | Sc | alidas | de se | gment | os |   |

|---------|----------|---|---|---|---|----|--------|-------|-------|----|---|

| Decimal | ٥        | С | В | Α | а | b  | С      | d     | e     | f  | 9 |

| 0       | 0        | 0 | 0 | 0 | 1 | 1  | 1      | 1     | 1     | 1  | 0 |

| 1       | 0        | 0 | 0 | 1 | 0 | 1  | 1      | 0     | 0     | 0  | 0 |

| 2       | 0        | 0 | 1 | 0 | 1 | 1  | 0      | 1     | 1     | 0  | 1 |

| 3       | 0        | 0 | 1 | 1 | 1 | 1  | 1      | 1     | 0     | 0  | 1 |

| 4       | 0        | 1 | 0 | 0 | 0 | 1  | 1      | 0     | 0     | 1  | 1 |

| 5       | 0        | 1 | 0 | 1 | 1 | 0  | 1      | 1     | 0     | 1  | 1 |

| 6       | 0        | 1 | 1 | 0 | 1 | 0  | 1      | 1     | 1     | 1  | 1 |

| 7       | 0        | 1 | 1 | 1 | 1 | 1  | 1      | 0     | 0     | 0  | 0 |

| 8       | 1        | 0 | 0 | 0 | 1 | 1  | 1      | 1     | 1     | 1  | 1 |

| 9       | 1        | 0 | 0 | 1 | 1 | 1  | 1      | 1     | 0     | 1  | 1 |

| 10      | 1        | 0 | 1 | 0 | X | X  | X      | X     | X     | X  | X |

| 11      | 1        | 0 | 1 | 1 | X | X  | X      | X     | X     | X  | X |

| 12      | 1        | 1 | 0 | 0 | X | X  | X      | X     | X     | X  | X |

| 13      | 1        | 1 | 0 | 1 | X | X  | X      | X     | X     | X  | X |

| 14      | 1        | 1 | 1 | 0 | X | X  | X      | X     | X     | X  | X |

| 15      | 1        | 1 | 1 | 1 | X | X  | X      | X     | X     | X  | X |

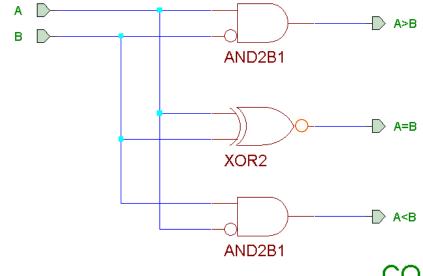

## Comparador de bits

- Comparador de bits: circuito con 2 entradas y 3 salidas que se utiliza para comparar bits

- Comparador de 2 bits. Tabla de la verdad, ecuaciones y circuito

| A | В | A>B | A=B | A <b< th=""></b<> |

|---|---|-----|-----|-------------------|

| 0 | 0 | 0   | 1   | 0                 |

| 0 | 1 | 0   | 0   | 1                 |

| 1 | 0 | 1   | 0   | 0                 |

| 1 | 1 | 0   | 1   | 0                 |

$$A > B = A\overline{B}$$

$A = B = \overline{A} \oplus B$

$A < B = \overline{A}B$

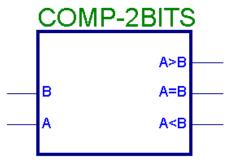

## Funciones lógicas con DEC o MUX

Ejemplo: | A) Diseñar F mediante un Decodificador 4-16 y una puerta OR

| Α                                                        | В | С | D                | F   |

|----------------------------------------------------------|---|---|------------------|-----|

| 0                                                        | 0 | 0 | 0                | 1   |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 | 0 | 0 | 1                | 1   |

| 0                                                        | 0 | 1 | 0                |     |

| 0                                                        | 0 | 1 | 0<br>1           | 0 1 |

| 0                                                        | 1 | 0 | 0<br>1           | 0   |

| 0                                                        | 1 | 0 | 1                | 1   |

| 0                                                        | 1 | 1 | 0                | 0   |

| 0                                                        | 1 | 1 | 1                |     |

| 1                                                        | 0 | 0 | 0                | 1 0 |

| 1                                                        | 0 | 0 | 1                |     |

| 1                                                        | 0 | 1 | 0                | 1 0 |

| 1                                                        | 0 | 1 | 1                | 0   |

| 1                                                        | 1 | 0 | 1<br>0<br>1<br>0 | 1   |

| 1                                                        | 1 | 0 | 0                |     |

|                                                          | 1 | 1 | 0                | 0   |

| 1                                                        | 1 | 1 | 1                | o   |

Eicielo

Sweeter

Equivalente a suma de productos.

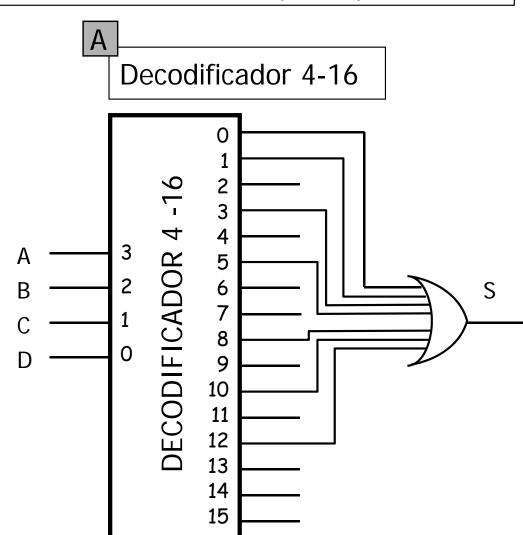

# Funciones lógicas con DEC o MUX

Ejemplo:

B) Diseñar F mediante un Multiplexor 8-1

| Α                                                             | В      | С | D | F                          |          |

|---------------------------------------------------------------|--------|---|---|----------------------------|----------|

| 0                                                             | 0      | 0 | 0 | 1                          | ์<br>โ   |

| 0                                                             | 0      | 0 | 1 | 1 1                        |          |

| 0                                                             | 0      | 1 | 0 | 0                          | ĺ        |

| 0                                                             | 0      | 1 | 1 | 0<br>1<br>0<br>1<br>0<br>0 | <b> </b> |

| 0                                                             | 1      | 0 | 0 | 0                          |          |

| 0                                                             | 1      | 0 | 1 | 1                          |          |

| 0                                                             | 1      | 1 | 0 | 0                          | ו        |

| 0                                                             | 1      | 1 | 1 | 0                          | }        |

| 1                                                             | 0      | 0 | 0 | 1 0                        |          |

| 1                                                             |        | 0 | 1 | 0                          |          |

| 1                                                             | 0<br>0 | 1 | 0 | 1                          | $]$      |

| 1                                                             | 0      | 1 | 1 | 0                          | Į        |

| 1                                                             | 1      | 0 | 0 | 1                          |          |

| 1                                                             | 1      | 0 | 1 | 0                          | ļ        |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 | 1      | 1 | 0 | 1<br>0<br>1<br>0<br>0      |          |

| 1                                                             | 1      | 1 | 1 | 0                          |          |

Si es 11, se pone 1 en su entrada

Si es 01, se pone D en su entrada

Si es 00, se pone 0 en su entrada

Si es 10, se pone /D en su entrada

- 1. Asociar variables (A,B,C,D,...) a las entradas de control  $(S_n...S_2,S_1,S_0)$ .

- 2. Las variables no asociadas al control, forman parte de las entrada del MUX

- 3. Las variables asociadas al control, NUNCA forman parte las entrada del MUX

- 4. Algunas entradas al MUX pueden ser '0' ó '1'