# Problemas de Fundamentos de Computadores $Tema\ 6$

## Problemas básicos:

- 1. Los dispositivos USB transmiten los datos en serie utilizando un formato denominado non-return-to-zero inverted (NRZI). Se desea diseñar un circuito secuencial con una entrada, x, y una salida, z, ambas de 1 bit, que convierta una secuencia binaria en una secuencia equivalente en formato NRZI. Lo hará de la siguiente manera:

- Si x vale '1', la salida conservará su valor anterior.

- Si x vale '0', la salida cambiará de polaridad, es decir, si valía '1' pasará a '0' y si valía '0' pasará a '1'.

Por ejemplo, asumiendo que el valor inicial de la salida es '1', la secuencia de entrada "10001110011010..." deberá transformarse en la secuencia "10100001000110..."

## Se pide:

- a) Especificar el sistema como máquina de Mealy.

- b) Implementar el conversor usando biestables D y puertas lógicas.

- c) Encontrar una implementación equivalente como máquina de Moore.

- **2.** Un sistema secuencial síncrono tiene una entrada, *x*, y una salida, *z*, ambas de 1 bit. Inicialmente la salida vale '0' y no pasa a valer '1' hasta que no recibe tres '0' consecutivos. Desde ese momento, la salida vale 1 durante dos ciclos de reloj con independencia del valor que tome la entrada. Después vuelve al estado inicial. Implemente el sistema como máquina de Moore usando el menor número de puertas y biestables D. Calcule el coste y la frecuencia de reloj máxima a la que podría funcionar el circuito utilizando los datos de la biblioteca de celdas presentada en teoría.

- **3.** Implemente un sistema secuencial que realice el complemento a 2 de números de longitud variable recibidos en serie y en orden creciente de pesos (primero el bit menos significativo). El sistema tiene una entrada de datos, *x*, una salida de datos, *z*, y una entrada de control, *inicio*, que se pone a 1 para indicar el comienzo y el final del número a complementar. El comportamiento esperado es el siguiente:

|           |   |   |   |   |   |   |   |   |   |   |   |   | 12 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|----|

| inicio(t) | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1  |

| x(t)      | - | - | 0 | 0 | 1 | 0 | 1 | - | 0 | 1 | 1 | 1 | -  |

| z(t)      | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0  |

- **4.** Usando el menor número de puertas lógicas y series de biestables D encadenados, diseñe como máquina de Mealy un reconocedor de secuencias que responda a las siguientes especificaciones:

- Tiene una entrada,  $\underline{x}$  de 3 bits, por la que en cada ciclo de reloj llega un dígito decimal del conjunto  $\{0,1,...,7\}$  codificado en binario.

• La salida binaria, z de 1 bit, toma el valor '1' si y solo si los últimos 4 dígitos recibidos forman la secuencia (0,3,4,7).

## **Problemas adicionales:**

- 5. Un circuito secuencial con dos biestables D, dos entradas, x e y, y una salida, z, está definido por las siguientes ecuaciones lógicas:

- $\bullet \quad D_1 = x \cdot Q_1 + x \cdot y$

- $\bullet \quad \bar{D_0} = \bar{x} \cdot Q_0 + x \cdot Q_1$

- $z = \bar{x} \cdot Q_0$

## Se pide:

- a. Dibuje el circuito.

- b. Obtenga la tabla de transición de estados.

- c. Dibuje el diagrama de estados que lo define.

- d. Convierta el diagrama Mealy a un diagrama Moore equivalente. Obtenga la tabla de transición de estados y el circuito resultante.

- **6.** Diseñe un circuito secuencial síncrono que genere la secuencia "00000001" cada vez que su entrada, x, valga '1'. Una vez que la secuencia comienza, debe completarse con independencia del valor que tome la entrada. Si la entrada vale 0, la salida debe mantenerse constantemente a '1'.

## Se pide:

- a. Especificar el sistema como máquina de Moore.

- b. Diseñe el circuito utilizando biestables D y puertas lógicas. No olvide distribuir adecuadamente la señal de *reset* para que el circuito se inicialice al estado inicial (en donde lee el valor de la entrada para determinar si debe comenzar a generar la secuencia o debe mantener a '1' la salida).

- 7. Usando el menor número de puertas lógicas y series de biestables D encadenados, diseñe un circuito con una entrada de 4 bits, <u>x</u>, por la que en cada ciclo de reloj recibe un dígito BCD y una salida, <u>z</u>, que puede tomar, codificados en binario, los siguientes valores:

- 0 si  $\{x(t-2), x(t-1), x(t)\}$  forman un número múltiplo de 5.

- 1 si  $\{x(t-2), x(t-1), x(t)\}$  forman un número mayor o igual que 400.

- 2 si se cumplen las dos anteriores condiciones a la vez.

- 3 en cualquier otro caso.

Para el diseño se utilizarán biestables y puertas lógicas. Calcule el coste y la frecuencia de reloj máxima a la que podría funcionar el circuito utilizando los datos de la biblioteca de celdas presentada en teoría.

8. Se desea diseñar un sistema secuencial síncrono con una entrada  $x \in \{\text{Norte, Sur, Este, Oeste}\}\$  y una salida  $z \in \{0,1\}$ . La salida z(t) tomará el valor '1' si:

$$\{x(t-2), x(t-1), x(t)\} = \{$$

Norte, Este, Este  $\}$  o  $\{$  Sur, Este, Este  $\}$

En todos los demás casos el valor de z(t) será '0'. Se pide:

- a) Construir el diagrama de estados del sistema en la forma de una máquina Mealy. Explique el significado de cada estado.

- b) Implemente el sistema con el menor número posible de biestables D y puertas lógicas.

**9.** Implemente un sistema secuencial que realice la suma de 2 de números de longitud variable recibidos en serie y en orden creciente de pesos (primero el bit menos significativo). El sistema tiene dos entradas de datos, x e y, una salida de datos, z, y una entrada de control, *inicio*, que se pone a '1' para indicar el comienzo y el final de los números sumar. El comportamiento esperado es el siguiente:

|           |   |   |   |   |   |   |   |   |   |   |   |   | 12 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|----|

| inicio(t) | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1  |

| x(t)      | - | - | 0 | 0 | 1 | 0 | 1 | - | 0 | 1 | 1 | 1 | -  |

| y(t)      | - | - | 0 | 1 | 1 | 0 | 1 | - | 0 | 1 | 1 | 1 | -  |

| z(t)      | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1  |

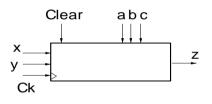

**10.** Diseñe un comparador para números de números binarios de *n* bits sin signo, *A* y *B*, según el esquema mostrado en la figura. Los números llegan en serie por las entradas *x* e y, comenzando por el bit menos significativo. El circuito es capaz de analizar diversas relaciones de comparación entre *A* y B, mediante las entradas de control (*a*, *b*, *c*) de acuerdo con la tabla. La salida, z, toma el valor '1' si la relación es cierta y '0' en otro caso. Use puertas y biestables D. Calcule el coste y la frecuencia de reloj máxima a la que podría funcionar el circuito utilizando los datos de la biblioteca de celdas presentada en teoría.

| abc | relación<br>analizada |

|-----|-----------------------|

| 000 | A=B                   |

| 001 | A#B                   |

| 010 | A>B                   |

| 011 | A>=B                  |

| 100 | A <b< th=""></b<>     |

| 101 | A<=B                  |

- 11. Un sistema secuencial tiene una entrada, <u>x</u>, de 2 bits y dos salidas, z y m. La salida z vale '1' cuando el valor actual de la entrada es igual al valor anterior de la misma. Cuando el valor actual y anterior de <u>x</u> no coinciden, la salida m vale '1' si el valor actual de la entrada es mayor que el anterior. En el resto de casos z y m valen '0'. Implemente el sistema como máquina de Mealy usando el menor número de biestables D y puertas lógicas. Ídem como máquina de Moore. Calcule en cada caso el coste y la frecuencia de reloj máxima a la que podría funcionar el circuito utilizando los datos de la biblioteca de celdas presentada en teoría.

- **12.** Se desea diseñar el sistema de control de una escalera mecánica bidireccional que puede estar parada, subiendo o bajando.

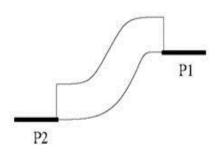

El sistema tiene 2 entradas conectadas a dos sensores de presión, *P1* y *P2*, situados en las posiciones mostradas en la figura. Cuando se activa un sensor, la escalera empieza a moverse en sentido al otro sensor y no para hasta que dicho sensor se active. No se considera la situación de que se activen simultáneamente ambos sensores ya que cuando se activa uno, se desactiva automáticamente y no vuelve a activarse hasta que se ha activado el contrario y viceversa.

El sistema tiene 2 salidas: encendido, *E*, (si *E* vale '1' la escalera se mueve) y sentido, *S*, (si *S* vale '1' la escalera sube y si vale '0' la escalera baja).

Diseñe el sistema como máquina de Moore usando el menor número de biestables D y puertas lógicas.

- 13. Diseñe como máquina de Moore un sistema capaz de detectar los flancos de una señal digital que transmite a baja velocidad datos en serie (es decir, el tiempo transcurrido entre dos cambios sucesivos de polaridad es bastante superior al periodo del reloj del sistema). El sistema tendrá una entrada, x, y dos salidas, up y down. La salida up valdrá 1 durante un ciclo de reloj cada vez que detecte una transición de 0 a 1 en la entrada. La salida down valdrá 1 durante un ciclo de reloj cada vez que detecte una transición de 1 a 0 en la entrada.

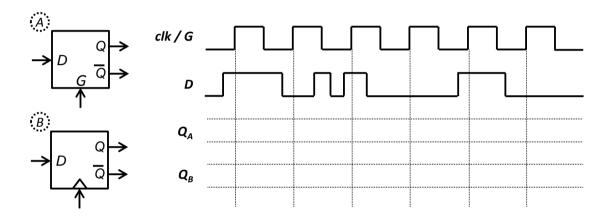

- **14.** Despreciando los retardos, complete el cronograma mostrado en la figura para un latch D (biestable D síncrono por nivel en alta) y un flip-flop D (biestable D síncrono por flanco de subida). Suponga que el valor inicial de la salida de ambos biestables es '0'.

**15.** Usando un biestable D disparado por flanco y las puertas necesarias, implemente un biestable T cuyo comportamiento coincida con el de la tabla siguiente:

| T(t) | Q(t+1)            |

|------|-------------------|

| 0    | Q(t)              |

| 1    | $\overline{Q(t)}$ |

**16.** Usando un biestable D disparado por flanco y las puertas necesarias, implemente un biestable JK cuyo comportamiento coincida con el de la tabla siguiente:

| J(t) | K(t) | Q( <i>t</i> +1)            |

|------|------|----------------------------|

| 0    | 0    | Q(t)                       |

| 0    | 1    | 0                          |

| 1    | 0    | _1_                        |

| 1    | 1    | $\overline{\mathbf{Q}(t)}$ |

#### Problemas de examen:

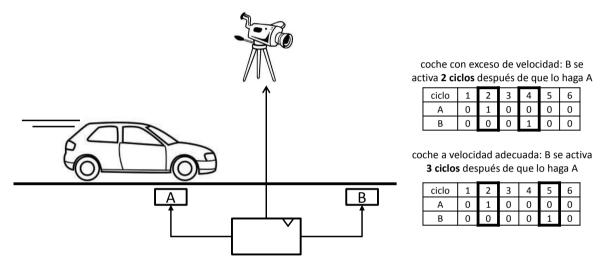

**17.** (Junio 2012) Se desea diseñar un sistema que permita fotografiar las matrículas de aquellos coches que circulen con exceso de velocidad por una carretera.

El sistema tendrá 2 entradas (A y B) conectadas a sensores de presión ubicados debajo del pavimento y una salida (F) conectada al disparador de una cámara. En ausencia de

coches las entradas valdrán '0' y cada vez que un coche pase por encima de un sensor la correspondiente entrada se activará (valdrá '1' durante un ciclo de reloj). Supóngase que nunca ambas entradas valdrán simultáneamente '1' y que los pulsos en A y en B se irán alternando (es decir, tras un pulso en A vendrá siempre un pulso en B y viceversa).

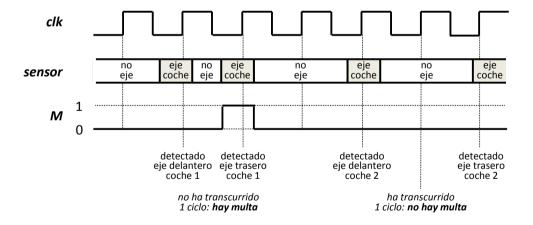

Un coche irá a más velocidad de la permitida si el número de ciclos de reloj que transcurren desde la activación de *A* hasta la activación de *B* es menor que 3, en cuyo caso deberá ser fotografiado (véase la figura).

## Se pide:

- a) Especificar el sistema como máquina de Mealy.

- b) Implementarlo utilizando 2 biestables D y el menor número de puertas lógicas.

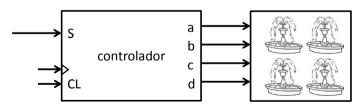

- **18.** (Febrero 2013) Se quiere diseñar el sistema que controla el encendido y apagado de las 4 fuentes (llamadas *a*, *b*, *c* y *d*) que hay en un parque. La secuencia en la que se apagan y encienden depende de una señal de control *S*.

- Si el valor de S es '1', la secuencia es: **ab**, **bc**, **cd**, **ab**, **bc**... Es decir (**a** y **b**: encendidas; **c** y **d**: apagadas), (**b** y **c**: encendidas; **a** y **d**: apagadas), (**c** y **d**: encendidas; **a** y **b**: apagadas)...

- Si el valor de S es '0', la secuencia es: ad, bc, ad, bc...

Siempre que cambia el valor de S, se empieza por el primer estado de la secuencia correspondiente. El sistema tiene además un estado inicial en el que todas las fuentes están apagadas y desde el que salta a la correspondiente secuencia según el valor de S.

#### Se pide:

- a) Especificar el sistema mediante un diagrama de estados como máquina de Moore.

- b) Indicar las tablas de verdad que especifican las funciones de salida y transición de estados del sistema.

- c) Implementar el sistema mediante biestables D y una memoria ROM de tamaño mínimo.

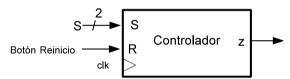

- **19.** (Junio 2013) Se quiere diseñar un circuito digital que controle el funcionamiento de una máquina expendedora de caramelos. Dicho controlador recibe una señal de entrada *S* procedente de un sensor que toma el valor (00)<sub>2</sub> mientras no se introduzca ninguna moneda en la máquina, o la moneda introducida no sea de 5 o 10 céntimos. Cuando se introduce una moneda de 5 o 10 céntimos la señal *S* toma los valores (01)<sub>2</sub> y (10)<sub>2</sub> respectivamente. Para expender un caramelo el controlador deberá activar la señal de salida *z*. La máquina se comporta de la siguiente manera:

- Cada caramelo cuesta 15 céntimos.

- El cliente puede ir introduciendo monedas en el orden que quiera.

- Cuando el saldo introducido alcanza o supera los 15 céntimos la máquina expende un caramelo, quedando almacenado el saldo restante por si el cliente quiere comprar otro caramelo. Por ejemplo, si un cliente introduce dos monedas de 10 céntimos seguidas, al introducir la segunda moneda la máquina expende un caramelo y deja almacenados los 5 céntimos sobrantes por si el cliente quiere seguir comprando.

- El cliente puede pulsar en cualquier momento un botón de reinicio, la máquina le devolverá entonces el saldo actual y quedará a la espera de que algún nuevo cliente comience a usar la máquina.

## Se pide:

- a) Especificar el sistema mediante un diagrama de estados como máquina de Moore.

- b) Indicar las tablas de verdad que especifican las funciones de salida y transición de estados del sistema.

- c) Implementar el sistema mediante biestables D y una memoria ROM de tamaño mínimo.

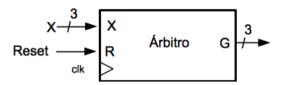

- **20.** (Septiembre 2013) Se quiere diseñar un circuito digital para arbitrar el acceso de tres dispositivos a un bus, con el interfaz indicado en la figura. El árbitro recibirá una señal de petición por cada canal,  $\underline{X} = (x_2, x_1, x_0)$ : si  $x_i$  vale '1' hay petición por el canal i, si vale '0' no la hay. El canal 0 es más prioritario que el 1, que a su vez es más prioritario que el 2. El árbitro concederá el bus activando la correspondiente señal de grant:  $\underline{G} = (g_2, g_1, g_0)$ : si  $g_i$  vale '1' se concede el uso del bus al dispositivo conectado al canal i, si vale '0' el dispositivo no puede hacer uso del bus. El comportamiento del árbitro debe ser el siguiente:

- Mientras no haya petición por ninguno de los canales el árbitro permanece Inactivo, dejando las tres señales de *grant* a '0'.

- Si estando Inactivo se recibe petición por alguno de los canales (puede haber varias peticiones simultáneas), el árbitro debe conceder el uso del bus al canal más prioritario, activando su señal de *grant*.

- Una vez concedido el bus a un dispositivo, la señal de *grant* correspondiente debe permanecer activa hasta que el dispositivo que está siendo atendido desactive la petición (incluso si otro dispositivo más prioritario solicita el uso del bus). Por ejemplo, si se ha concedido el bus al dispositivo del canal 1, la señal *g*<sub>1</sub> debe permanecer activa hasta que *x*<sub>1</sub> se ponga a '0'. Cuando el dispositivo desactiva la petición el árbitro pasará a estado Inactivo para iniciar un nuevo ciclo de bus.

#### Se pide:

a) Especificar el sistema mediante un diagrama de estados como máquina de Moore.

- b) Indicar las tablas de verdad que especifican las funciones de salida y transición de estados del sistema.

- c) Implementar el sistema usando biestables D y puertas.

**21.** (Febrero 2014) Se desea diseñar un sistema secuencial para controlar la velocidad de circulación en un túnel por el que únicamente pueden circular coches y camiones (ambos vehículos de dos ejes). Para ello se instala un sensor de presión que ofrece tres lecturas: eje de coche detectado, eje de camión detectado y eje no detectado.

Para comprobar si un vehículo circula a la velocidad permitida el sistema mide los ciclos de reloj que transcurren entre la detección del eje delantero y el trasero aplicando las siguientes reglas:

- En caso de que se haya detectado el eje delantero de un coche, deberá transcurrir al menos 1 ciclo de reloj hasta la detección del trasero.

- En caso de detección de eje delantero de un camión, deberán transcurrir al menos 2 ciclos de reloj hasta la detección del eje trasero.

En caso de que no se cumplan los márgenes de tiempo el sistema activará una señal de salida multa (M) y volverá al estado inicial. En caso de que la detección del eje trasero no corresponda al mismo tipo de vehículo que el delantero activará una señal de error (E) y volverá al estado inicial. La figura muestra un ejemplo del comportamiento esperado.

#### Se pide:

- a) Especifique el sistema mediante un diagrama de estados como máquina de Mealy, definiendo las entradas, salidas y estados.

- b) Implemente el sistema utilizando biestables D y una memoria ROM.