| Apel                                                                                                                                                                                                                     | lidos                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Non                                                    | bre                                       |                                                                                                                | Grupo                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A                                                                                                                                                                                                                        | rquit                                                                                                                                        | tectura e Ingeniería de Computadores. Examen Fi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | inal (Te                                               | oría                                      | a – parte primer cı                                                                                            | uatrimestre). 18/06/2012                                                                                                                                                                                |

| ción e<br>na " <b>F</b> '                                                                                                                                                                                                | s cier<br>". Si c                                                                                                                            | nes Cada pregunta consta de cinco afirmaciones, y cada una d<br>ta marque con un aspa la casilla de la columna "C"; por el contar<br>considera que alguna respuesta es ambigua y, por tanto, podría<br>explique sus argumentos al dorso de la hoja. No se permite la utiliz                                                                                                                                                                                                                                                                                                                                                                          | io, si con<br>conside                                  | sider<br>arse                             | a que es falsa marque cierta o falsa en funcio                                                                 | con un aspa la casilla de la colum-                                                                                                                                                                     |

| La ted                                                                                                                                                                                                                   | oría de                                                                                                                                      | n Pregunta con 5 aciertos: 1 punto. 4 aciertos: 0,6 puntos. 3 acie el primer cuatrimestre supone la mitad de la nota del primer cuatri primer cuatrimestre tenga un peso del 65% en la nota final de la a                                                                                                                                                                                                                                                                                                                                                                                                                                            | imestre.                                               | Tante                                     |                                                                                                                |                                                                                                                                                                                                         |

| comp<br>2 cic<br>instru<br>frecu                                                                                                                                                                                         | ouesto<br>los d<br>iccior<br>encia                                                                                                           | X segmentado en 7 etapas ejecuta un programa o por 10 <sup>6</sup> instrucciones invirtiendo un promedio de le reloj por instrucción. El programa contiene 10 <sup>5</sup> nes de punto flotante y el resto son enteras. La de reloj es 2 GHz. Marque cuáles de las siguienciones son correctas.                                                                                                                                                                                                                                                                                                                                                     | págin<br>nable<br>bits. I<br>ticas:<br>- Tam<br>- Nive | as d<br>indi<br>∟a je<br>naño<br>el 1     | e 32 Kbytes. Cada b<br>ividualmente mediar<br>rarquía de memoria<br>de bloque de cache:<br>(I-cache): emplazam | on memoria virtual que maneja oyte de la memoria es direccionte direcciones físicas de 32 tiene las siguientes caracteríses siempre 64 bytes. Niento directo, virtualmente acde tamaño máximo. Tiene un |

| X                                                                                                                                                                                                                        |                                                                                                                                              | a) El tiempo de ejecución del programa es 1 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | buffer                                                 | de p                                      | orebúsqueda con cap<br>(D-cache): emplazam                                                                     | pacidad para un bloque.<br>niento asociativo por conjuntos                                                                                                                                              |

| X                                                                                                                                                                                                                        |                                                                                                                                              | b) La penalización media por instrucción es de 0,5 ns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tamai                                                  | ňo m                                      | áximo.                                                                                                         | edida físicamente marcada, de nplazamiento directo, accedida                                                                                                                                            |

|                                                                                                                                                                                                                          | X                                                                                                                                            | c) El rendimiento es 100 GFLOPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |                                           |                                                                                                                | tamaño de 8 Mbytes.                                                                                                                                                                                     |

| X                                                                                                                                                                                                                        |                                                                                                                                              | d) Si sabemos que la penalización media por cada instrucción entera es de 0,5 ciclos de reloj, entonces podemos concluir que la penalización media por cada instrucción de punto flotante es 5,5 ciclos de                                                                                                                                                                                                                                                                                                                                                                                                                                           | Marq<br><b>C</b><br>⊠                                  | ue cu<br><b>F</b>                         | -                                                                                                              | es afirmaciones son correctas.  I-cache del nivel 1 es 32 Kbytes.                                                                                                                                       |

| X                                                                                                                                                                                                                        |                                                                                                                                              | reloj. e) Si hacemos una mejora de la arquitectura, de tal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        | X                                         | b) El tamaño de la                                                                                             | D-cache del nivel 1 es 64 Kbytes                                                                                                                                                                        |

| Arquite  Instruccione ción es cierta na "F". Si co llamada y ex  Puntuación. La teoría del para que el p  1. Un DLX compuesto 2 ciclos de instruccione frecuencia tes afirmaci  C F  I I I I I I I I I I I I I I I I I I | forma que en la ejecución del programa se invierte un promedio de 1,6 ciclos de reloj por instrucción, entonces el Speedup obtenido es 1,25. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X                                                      | c) El campo TAG e<br>nivel 1 tiene una ar | n el directorio de la D-cache del<br>nchura de 19 bits.                                                        |                                                                                                                                                                                                         |

|                                                                                                                                                                                                                          |                                                                                                                                              | gamos la arquitectura básica del DLX (sin planifica-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | X                                                      |                                           |                                                                                                                | G en el buffer de prebúsqueda de<br>1 tiene una anchura de 26 bits.                                                                                                                                     |

| acces<br>reloj<br>de re<br>wardi<br>DE, y<br>comp<br>trucci<br>en el<br>suma<br>segm<br>cálcu                                                                                                                            | so a lay el a eloj. La ing). I ing). I ing) se bilado iones ador o entado de la elo 4,                                                       | nica), pero segmentado en ocho etapas, donde el la memoria de instrucciones consume dos ciclos de acceso a la memoria de datos consume tres ciclos a máquina posee anticipación de operandos (for-Las instrucciones de salto se resuelven en la etapa implementa una política de saltos retardados. El or rellena el hueco de retardo (delay slot) con inserprevias al salto en el 60% de los casos y con NOP de los casos. Además la etapa EX incluye un de punto flotante segmentado, un multiplicador no do y un divisor no segmentado, con tiempos de 7 y 20 ciclos de reloj, respectivamente. Marque las siguientes afirmaciones son correctas. | X                                                      |                                           | e) El campo de TA<br>nivel 2 tiene una ar                                                                      | AG en el directorio de la cache de<br>nchura de 9 bits.                                                                                                                                                 |

|                                                                                                                                                                                                                          |                                                                                                                                              | a) La ejecución de una instrucción LOAD puede provocar un máximo de cuatro ciclos de reloj de penalización debido a las dependencias LDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |                                           |                                                                                                                |                                                                                                                                                                                                         |

| X                                                                                                                                                                                                                        |                                                                                                                                              | b) La penalización media por salto es 0,8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |                                           |                                                                                                                |                                                                                                                                                                                                         |

| X                                                                                                                                                                                                                        |                                                                                                                                              | c) La presencia en un programa de tres instrucciones<br>consecutivas de la forma:<br>MULD F2, F4, F6<br>ADDD F8, F4, F0<br>MULD F10, F0, F6<br>provocará penalización.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                        |                                           |                                                                                                                |                                                                                                                                                                                                         |

| X                                                                                                                                                                                                                        |                                                                                                                                              | d) En esta arquitectura es necesario detectar los riesgos EDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |                                           |                                                                                                                |                                                                                                                                                                                                         |

□ ⊠ e) El intervalo de iniciación del multiplicador es 1.

## Arquitectura e Ingeniería de Computadores. Examen Parcial (Problemas). 18/06/2012

Nombre------Grupo-------

- **1)** Sea un procesador segmentado con planificación dinámica mediante el algoritmo de Tomasulo sin especulación. El procesador tiene las siguientes características:

- Los datos que se escriben en la etapa de escritura no se pueden usar en la etapa de ejecución de una instrucción dependiente hasta el ciclo siguiente.

- Las instrucciones de load y store tienen ambas una latencia de 3 ciclos y utilizan una unidad funcional común para su ejecución.

- Existe un único bus común de datos (CDB).

- Se dispone de las siguientes unidades funcionales, estaciones de reserva, buffers de load (LB) y buffers de store (SB):

| UF         | Cantidad | Latencia | Segmentación |

|------------|----------|----------|--------------|

| FP ADDD    | 1        | 2        | Sí           |

| FP MULD    | 1        | 5        | Sí           |

| FP DIVD    | 1        | 7        | No           |

| LOAD/STORE | 1        | 3        | No           |

| INT ALU    | 1        | 1        | No           |

| Estaciones de reserva /LB /SB | Cantidad |

|-------------------------------|----------|

| FP ADDD                       | 2        |

| FP MULD                       | 1        |

| FP DIVD                       | 1        |

| LOAD                          | 1        |

| STORE                         | 1        |

a) Para el siguiente código mostrar en qué ciclo o ciclos se llevan a cabo cada una de las tres fases del algoritmo de Tomasulo para cada instrucción, indicando también en cada caso el tipo de parada que se produce. (1.25 ptos)

|    | Instrucción            | ISSUE | <b>EJECUCIÓN</b> | ESCRITURA |

|----|------------------------|-------|------------------|-----------|

| 1  | ADDD F0,F2,F4          |       |                  |           |

| 2  | LD F2,0(R3)            |       |                  |           |

| 3  | DIVD F4,F0,F4          |       |                  |           |

| 4  | SD 0(R2), F2           |       |                  |           |

| 5  | <b>ADDD F4, F0, F8</b> |       |                  |           |

| 6  | MULD F8,F2,F2          |       |                  |           |

| 7  | SD 0(R2),F8            |       |                  |           |

| 8  | DIVD F0,F8,F4          |       |                  |           |

| 9  | ADDD F4,F8,F0          |       |                  |           |

| 10 | ADDD F8,F2,F2          |       |                  |           |

- b) Indicar el estado de las estaciones de reserva, buffers de loads, buffers de stores y banco de registros en punto flotante al final del ciclo 4. **(0.5 ptos)**

- c) Si la unidad de suma en punto flotante fuese no segmentada, ¿variarían los ciclos correspondientes a las fases de ejecución de las dos últimas instrucciones del código? Razona la respuesta y en caso afirmativo indica los nuevos ciclos de ejecución de ambas instrucciones. (0.25 ptos)

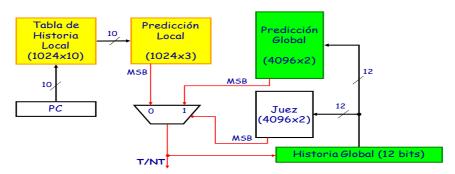

- **2)** Partiendo del esquema del Tournament predictor del Alpha 21264 visto en clase (figura 1), planteamos sobre el mismo las siguientes modificaciones:

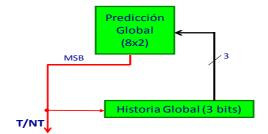

- Prescindimos de la parte de predicción local y del juez, por lo que la predicción obtenida depende únicamente del predictor global

- La tabla de predicción global pasa a ser de 8 entradas con 2 bits por entrada, y el registro de historia global pasa a ser únicamente de 3 bits

Estas modificaciones dan lugar al esquema que se muestra en la figura 2. Supongamos un procesador con predicción dinámica de saltos que usa el predictor mostrado en dicha figura 2, en el que se ejecuta el siguiente programa:

```

addi r1,r0,#6

loop1: add r5,r1,r1

subi r1,r1,#1

store 0(r1),r5

bnez r1, loop1

addi r2,r0,#4

loop2: add r6,r2,r2

subi r2,r2,#1

store 0(r2),r6

bnez r2, loop2

end: add r1,r2,r1

```

Si inicialmente tanto el registro de historia como la tabla de predicción contienen únicamente ceros. Indicar para cada salto ejecutado en este código: la entrada de la tabla de predicción a la que se accede, los bits de predicción de la misma antes y después de la ejecución del salto, el comportamiento del salto (tomado/no tomado) y si se trata de un acierto o un fallo. (1 pto)

Figura 1. Esquema del Tournament predictor del Alpha 21264

Figura 2. Esquema modificado

## Solución

1)

a)

|    | Instrucción            | ISSUE             | <b>EJECUCIÓN</b>     | <b>ESCRITURA</b>  |

|----|------------------------|-------------------|----------------------|-------------------|

| 1  | ADDD F0,F2,F4          | 1                 | 2-3                  | 4                 |

| 2  | LD F2,0(R3)            | 2                 | 3-5                  | 6                 |

| 3  | DIVD F4,F0,F4          | 3                 | 5-11 <sup>LDE</sup>  | 12                |

| 4  | SD 0(R2), F2           | 4                 | 7-9 <sup>LDE</sup>   | -                 |

| 5  | <b>ADDD F4, F0, F8</b> | 5                 | 6-7                  | 8                 |

| 6  | <b>MULD F8,F2,F2</b>   | 6                 | 7-11                 | 13 <sup>CDB</sup> |

| 7  | SD 0(R2),F8            | 10 EST            | 14-16 <sup>LDE</sup> | -                 |

| 8  | DIVD F0,F8,F4          | 13 <sup>EST</sup> | 14-20                | 21                |

| 9  | ADDD F4,F8,F0          | 14                | 22-23 <sup>LDE</sup> | 24                |

| 10 | ADDD F8,F2,F2          | 15                | 16-17                | 18                |

b)

|       | Op       | Busy | Vj              | Vk              | Qj    | Qk |

|-------|----------|------|-----------------|-----------------|-------|----|

| Suma1 | Suma     | No   | <del>[F2]</del> | <del>[F4]</del> | 0     | 0  |

| Suma2 |          | No   |                 |                 |       |    |

| Mul1  |          | No   |                 |                 |       |    |

| Div1  | División | Sí   | [F2+F4]         | [F4]            | Suma1 | 0  |

|       |          |      |                 |                 |       |    |

|        | Busy | Dir. | Qi    |

|--------|------|------|-------|

| Store1 | Sí   | 0+R3 | Load1 |

|       | Busy | Dir. |

|-------|------|------|

| Load1 | Sí   | 0+R3 |

|    | F0    | F2    | F4   | F6 | F8 |

|----|-------|-------|------|----|----|

| UF | Suma1 | Load1 | Div1 |    |    |

## c) No variarían

**2)** El primer salto del código se toma 5 veces, a la 6ª iteración no se toma, mientras que el segundo salto se toma 3 veces y no se toma a la 4ª iteración, a continuación el programa finaliza.

| Entrada tabla | Bits predicción | Comportamiento | Acierto/Fallo | Nuevos bits |

|---------------|-----------------|----------------|---------------|-------------|

| predicción    |                 | salto (T/NT)   |               | predicción  |

| 000           | 00              | T              | F             | 01          |

| 001           | 00              | T              | F             | 01          |

| 011           | 00              | T              | F             | 01          |

| 111           | 00              | T              | F             | 01          |

| 111           | 01              | T              | F             | 10          |

| 111           | 10              | NT             | F             | 01          |

| 110           | 00              | T              | F             | 01          |

| 101           | 00              | T              | F             | 01          |

| 011           | 01              | T              | F             | 10          |

| 111           | 01              | NT             | A             | 00          |